1

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах на ОДП-транзисторах в интегральном исполнении для выработки сигнала на числовой шине накопителя при определенной комбинации входньк адресных сигналов.

Цель изобретения - расщирение области его применения путем обеспечения статического режима работы.

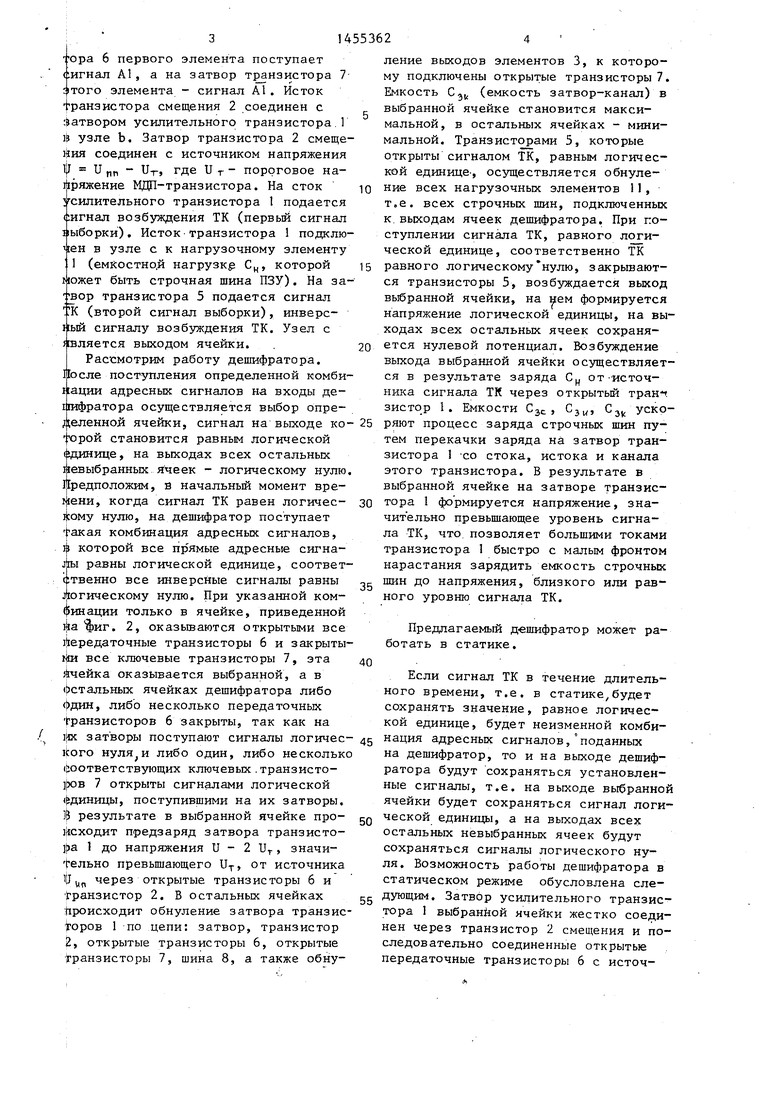

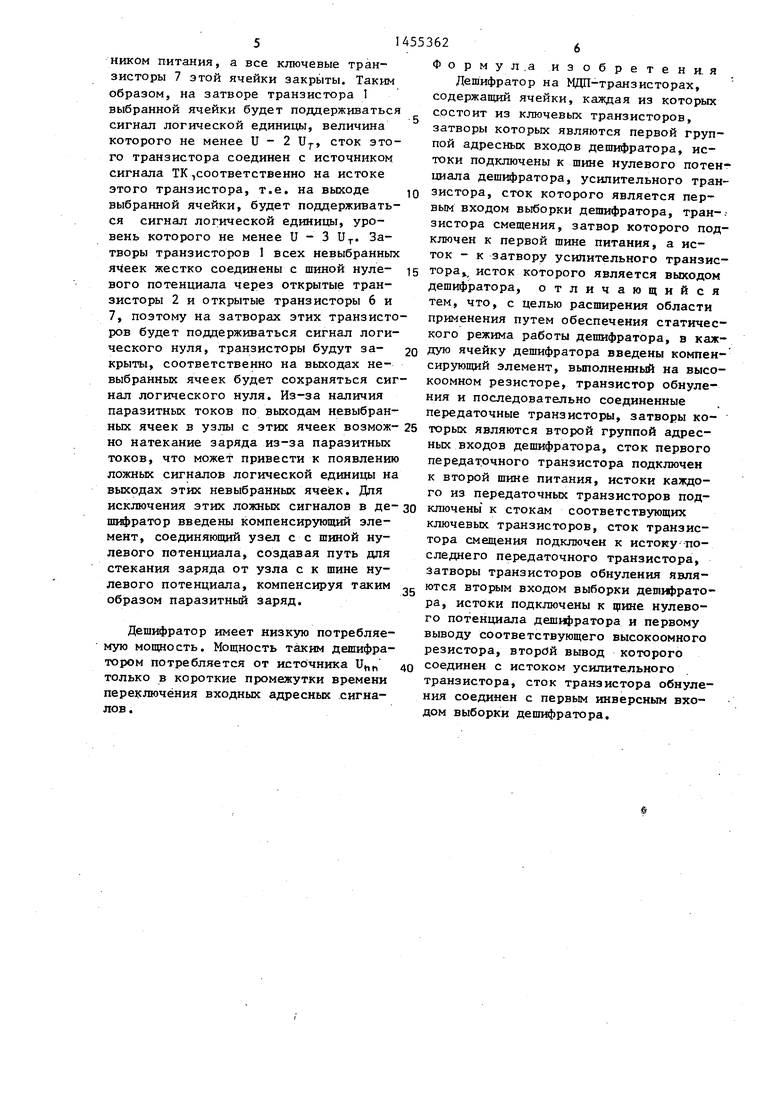

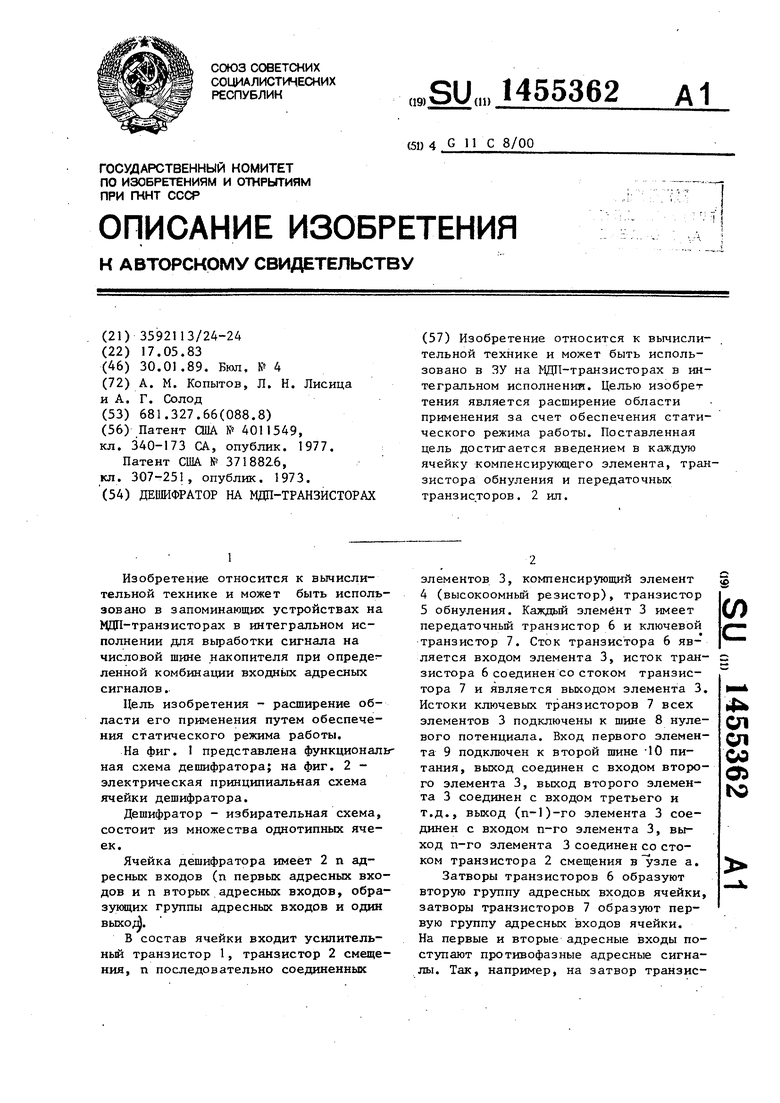

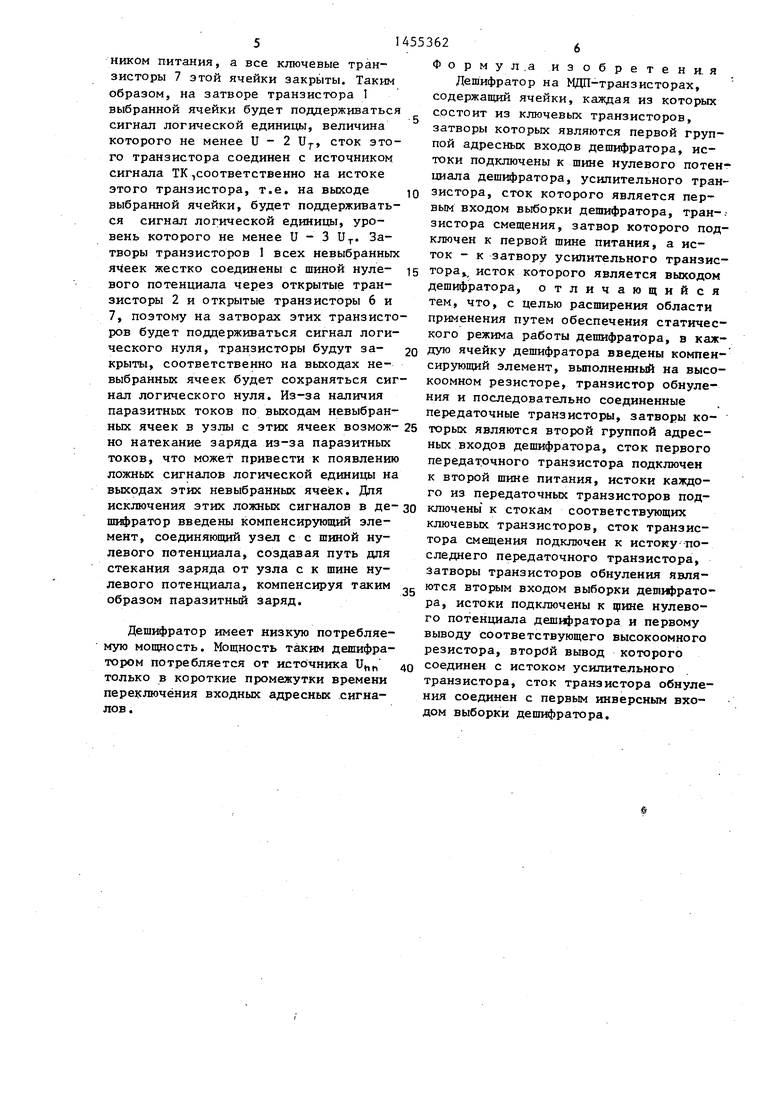

На фиг. 1 представлена функциональ- ная схема дешифратора; на фиг. 2 - электрическая принципиальная схема ячейки дешифратора.

Дешифратор - избирательная схема, состоит из множества однотипных ячеек.

Ячейка дешифратора имеет 2 п адресных входов (п первьк адресных входов и п вторых адресных входов, обра- зукицих группы адресных входов и один выхоА

В состав ячейки входит усилитель- ньй транзистор 1, транзистор 2 смещения, п последовательно соединенных

2

элементов 3, компенсирующий элемент

4(высокоомный резистор), транзистор

5обнуления. Каждый элемент 3 имеет передаточный транзистор 6 и ключевой транзистор 7. Сток транзистора 6 является входом элемента 3, исток транзистора 6 соединен со стоком транзистора 7 и является выходом элемента 3. Истоки ключевых транзисторов 7 всех элементов 3 подключены к шине 8 нулевого потенциала. Вход первого элемента 9 подключен к второй шине 10 питания, выход соединен с входом второго элемента 3, выход второго элемента 3 соединен с входом третьего и т.д., выход (п-1)-го элемента 3 соединен с входом п-го элемента 3, выход п-го элемента 3 соединен со стоком транзистора 2 смещения а.

Затворы транзисторов 6 образуют вторую группу адресных входов ячейки, затворы транзисторов 7 образуют первую группу адресных входов ячейки. На первые и вторые адресные входы поступают противофазные адресные сигналы. Так, наприкер, на затвор транзис fi

(Л

СП СП

со

О

1C

ора 6 первого элемента поступает сигнал А1, а на затвор транзистора 7 1ТОГО элемента - сигнал А1 . Исток франзистора смещения 2 соединен с :Итвором усилительного транзистора. и узле Ь. Затвор транзистора 2 смеще- Йия соединен с источником напряжения f и „„ - U-r, где и г - пороговое на- Аряжение МДП-транзистора. На сток усилительного транзистора 1 подается сигнал возбуждения ТК (первый сигнал пыборки). Исток транзистора 1 подключен в узле с к нагрузочному элементу

1 (емкостно.й нагрузку С, которой может быть строчная шина ПЗУ). На за- вор транзистора 5 подается сигнал . К (второй сигнал выборки), инверс- сигналу возбуждения ТК. Узел с является выходом ячейки.

Рассмотрим работу дешифратора. После поступления определенной комбинации адресных сигналов на входы де- 1гифратора осуществляется выбор опреление выходов элементов 3, к которому подключены открытые транзисторы 7. Емкость Cj (емкость затвор-канал) в выбранной ячейке становится максимальной , в остальных ячейках - минимальной. Транзисторами 5, которые открыты сигналом ТК, равным логической единице-, осуществляется обнуле-

10 ние всех нагрузочньк элементов 11, т.е. всех строчных шин, подключенных к, вьсходам ячеек дешифратора. При поступлении сигнала ТК, равного логической единице, соответственно ТК

15 равного логическому нулю, закрьшают- ся транзисторы 5, возбуждается выход выбранной ячейки, на нем формируется напряжение логической единицы, на вы ходах всех остальных ячеек сохраня20 ется нулевой потенциал. Возбуждение выхода выбранной ячейки осуществляет ся в результате заряда С от-источ- ника сигнала ТК через открытый тран зисто р 1. Емкости Сзс , C, Сэ уско

деленной ячейки, сигнал на выходе ко- 25 ряют процесс заряда строчных шин пуфорой становится равным логической (здинице, на выходах всех остальных иевыбранных ячеек - логическому нулю. Предположим, в начальный момент вре- ени, когда сигнал ТК равен логичес- зо ijcoMy нулю, на дешифратор поступает факая комбинация адресных сигналов, ф которой все прямые адресные сигнаЕ равны логической единице, соответ- венно все инверсные сигналы равны гическому нулю. При указанной ком- финации только в ячейке, приведенной 1 иг. 2, оказьшаются открытыми все 1)1ередаточные транзисторы 6 и закрыты- |tи все ключевые транзисторы 7, эта до йчейка оказывается выбранной, а в Остальных ячейках дешифратора либо фдин, либо несколько передаточных tpaH3HCTopoB 6 закрыты, так как на

35

тем перекачки заряда на затвор транзистора 1 СО стока, истока и канала этого транзистора. В результате в выбранной ячейке на затворе транзистора 1 формируется напряжение, значительно превьшгающее уровень сигнала ТК, что позволяет большими токами транзистора 1 быстро с малым фронтом нарастания зарядить емкость строчных шин до напряжения, близкого или равного уровню сигнала ТК.

Предлагаемый дешифратор может работать в статике.

Если сигнал ТК в течение длительного времени, т.е. в статике,будет сохранять значение, равное логической единице, будет неизменной комби |к затворы поступают сигналы логичес- 45 нация адресных сигналов, поданных koro нулями либо один, либо несколько на дешифратор, то и на выходе дешиф- фоответствующих ключевых.транзисто |юв 7 открыты сигналами логической фдиницы, поступившими на их затворы. 1 результате в выбранной ячейке про- (1сходит предзаряд затвора транзисто- ра 1 до напряжения U - 2 U, значительно превышающего U-j-, от источника ill ,„ через открытые транзисторы 6 и Транзистор 2. В остальных ячейках ;йроисходит обнуление затвора транзисторов 1 по цепи: затвор, транзистор 2, открытые транзисторы 6, открытые Транзисторы 7, шина 8, а также обнуратора будут сохраняться установленные сигналы, т.е. на выходе выбранной ячейки будет сохраняться сигнал логи5Q ческой единицы, а на выходах всех остальных невыбранных ячеек будут сохраняться сигналы логического нуля. Возможность работы дешифратора в статическом режиме обусловлена сле55 дующим. Затвор усилительного транзистора 1 выбранйой ячейки жестко сое}(я- нен через транзистор 2 смещения и последовательно соединенные открытые передаточные транзисторы 6 с источление выходов элементов 3, к которому подключены открытые транзисторы 7. Емкость Cj (емкость затвор-канал) в выбранной ячейке становится максимальной , в остальных ячейках - минимальной. Транзисторами 5, которые открыты сигналом ТК, равным логической единице-, осуществляется обнуле-

ние всех нагрузочньк элементов 11, т.е. всех строчных шин, подключенных к, вьсходам ячеек дешифратора. При поступлении сигнала ТК, равного логической единице, соответственно ТК

равного логическому нулю, закрьшают- ся транзисторы 5, возбуждается выход выбранной ячейки, на нем формируется напряжение логической единицы, на выходах всех остальных ячеек сохраняется нулевой потенциал. Возбуждение выхода выбранной ячейки осуществляется в результате заряда С от-источ- ника сигнала ТК через открытый тран зисто р 1. Емкости Сзс , C, Сэ ускоряют процесс заряда строчных шин пу

тем перекачки заряда на затвор транзистора 1 СО стока, истока и канала этого транзистора. В результате в выбранной ячейке на затворе транзистора 1 формируется напряжение, значительно превьшгающее уровень сигнала ТК, что позволяет большими токами транзистора 1 быстро с малым фронтом нарастания зарядить емкость строчных шин до напряжения, близкого или равного уровню сигнала ТК.

Предлагаемый дешифратор может работать в статике.

нация адресных сигналов, поданных на дешифратор, то и на выходе дешиф-

ратора будут сохраняться установленные сигналы, т.е. на выходе выбранной ячейки будет сохраняться сигнал логической единицы, а на выходах всех остальных невыбранных ячеек будут сохраняться сигналы логического нуля. Возможность работы дешифратора в статическом режиме обусловлена следующим. Затвор усилительного транзистора 1 выбранйой ячейки жестко сое}(я- нен через транзистор 2 смещения и последовательно соединенные открытые передаточные транзисторы 6 с источНИКОМ питания, а все ключевые транзисторы 7 этой ячейки закрыты. Таким образом, на затворе транзистора 1 выбранной ячейки будет поддерживаться сигнал логической единицы, величина которого не менее U - 2 U, сток этого транзистора соединен с источником сигнала ТК,соответственно на истоке этого транзистора, т.е. на выходе выбранной ячейки, будет поддерживаться сигнал логической единицы, уровень которого не менее U - 3 U,.. Затворы транзисторов 1 всех невыбранных

рмул.а изобретен и. я Дешифратор на МДП-транзисторах, содержащий ячейки, каждая из которых состоит из ключевых транзисторов, затворы которых являются первой группой адресных входов дешифратора, истоки подключены к шине нулевого потенциала дешифратора, усилительного транзистора, сток которого является первым входом выборки дешифратора, тран-. зистора смещения, затвор которого подключен к первой шине питания, а исток - к затвору усилительного транзисячеек жестко соединены с шиной нуле- ig тора, исток которого является выходом вого потенциала через открытые тран- дешифратора, отличающийся

тем, что, с целью расширения области

зисторы 2 и открытые транзисторы 6 и

7, поэтому на затворах этих транзисто-применения путем обеспечения статичес- ров будет поддерживаться сигнал логи-кого режима работы дешифратора, в каж- ческого нуля, транзисторы будут за- 20 ДУЮ ячейку дешифратора введены компен- крыты, соответственно на выходах не-сирующий элемент, выполненный на высо- выбранных ячеек будет сохраняться сиг-коомном резисторе, транзистор обнуле- нал логического нуля. Из-за наличияния и последовательно соединенные паразитных токов по выходам невыбран-передаточные транзисторы, затворы ко- ных ячеек в узлы с этих ячеек возмож- 25 торых являются второй группой адресно натекание заряда из-за паразитныхных входов дешифратора, сток первого токов, что может привести к появлениюпередаточного транзистора подключен ложных сигналов логической единицы нак второй шине питания, истоки каждо- выходах этих невыбранных ячеек. Дляго из передаточных транзисторов под- исключения этих ложных сигналов в де- зоключены к стокам соответствующих шифратор введены компенсирующий эле-ключевых транзисторов, сток транзис- мент, соединяющий узел ее шиной ну-тора смещения подключен к истоку полевого потенциала, создавая путь дляследнего передаточного транзистора, стекания заряда от узла с к шине ну-затворы транзисторов обнуления явля- левого потенциала, компенсируя таким дются вторым входом выборки дешифрато- образом паразитный заряд.ра, истоки подключены к щине нулевого потенциала деши})ратора и первому

Дешифратор имеет низкую потребляе-выводу соответствующего высокоомного

мую мощность. Мощность таким дешифра-резистора, второй вывод которого

тором потребляется от источника и,„ 40соединен с истоком усилительного

только в короткие промежутки временитранзистора, сток транзистора обнулепереключёния входных адресных сигна-ния соединен с первым инверсным вхо ° дом выборки дешифратора.

62 Ф о

рмул.а изобретен и. я Дешифратор на МДП-транзисторах, содержащий ячейки, каждая из которых состоит из ключевых транзисторов, затворы которых являются первой группой адресных входов дешифратора, истоки подключены к шине нулевого потенциала дешифратора, усилительного транзистора, сток которого является первым входом выборки дешифратора, тран-. зистора смещения, затвор которого подключен к первой шине питания, а исток - к затвору усилительного транзистора, исток которого является выходом дешифратора, отличающийся

тем, что, с целью расширения области

применения путем обеспечения статичес кого режима работы дешифратора, в каж ДУЮ ячейку дешифратора введены компен сирующий элемент, выполненный на высо коомном резисторе, транзистор обнуле- ния и последовательно соединенные передаточные транзисторы, затворы ко- торых являются второй группой адресных входов дешифратора, сток первого передаточного транзистора подключен к второй шине питания, истоки каждо- го из передаточных транзисторов под- ключены к стокам соответствующих ключевых транзисторов, сток транзис- тора смещения подключен к истоку последнего передаточного транзистора, затворы транзисторов обнуления явля- ются вторым входом выборки дешифрато- ра, истоки подключены к щине нулевого потенциала деши})ратора и первому

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Дешифратор на КМДП-транзисторах | 1982 |

|

SU1113853A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Формирователь адресных сигналов для блоков памяти | 1983 |

|

SU1163354A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЗУ на МДП-транзисторах в интегральном исполнении. Целью изобрет тения является расширение области применения за счет обеспечения статического режима работы. Поставленная цель достигается введением в каждую ячейку компенсирующего элемента, транзистора обнуления и передаточных транзисторов. 2 ил.

| Патент США № 4011549, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Патент США № 3718826, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1989-01-30—Публикация

1983-05-17—Подача