113631

Изобретение относится к вычисли - тельной технике и может быть использовано для моделирования рядов различных возвратных последовательностей. g

Выражение (1) позволяет моделиро вать унарную систему счисления и огромный класс возвратных последовательностей.

Sy(n)

0при

1при Oinsj;

J VA

(1)

L

S-() при .

При , ,l выражение (l) задает классическую двоичную систему счисления.

Цель изобретения - расширение функциональных возможностей за счет способности генерировать последова- тельности весов различг-шх возвратных последовательностей.

Сущность изобретения состоит в реализации выражения (1).

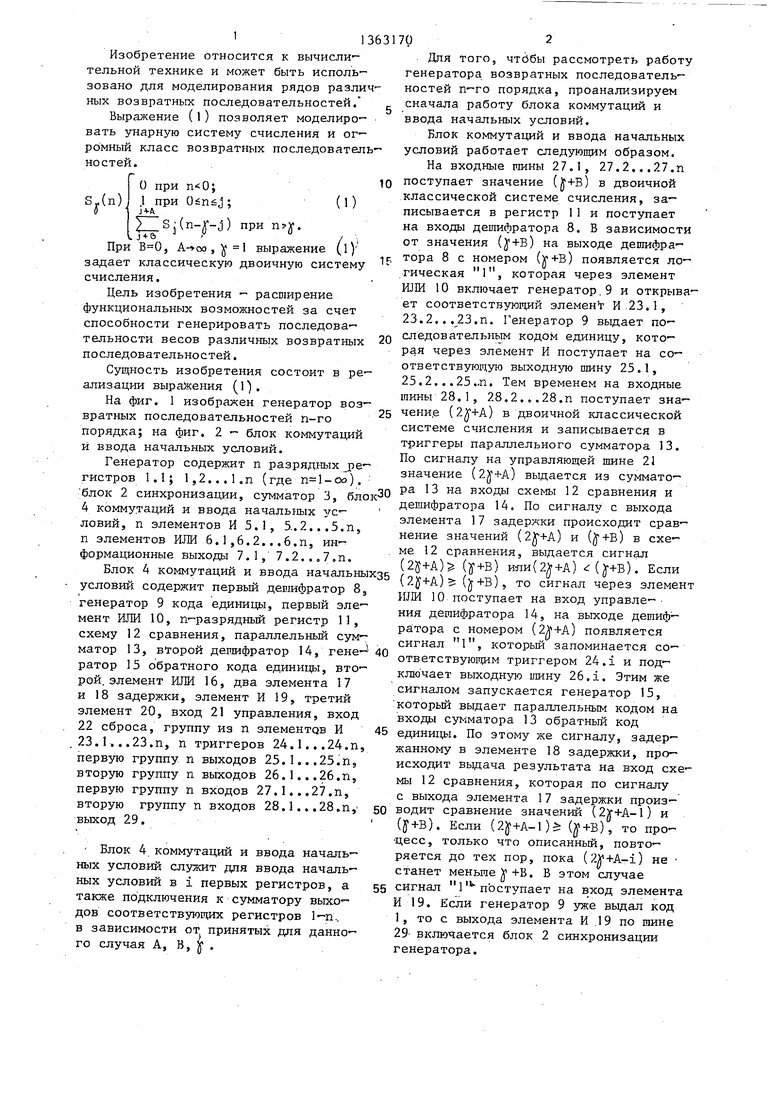

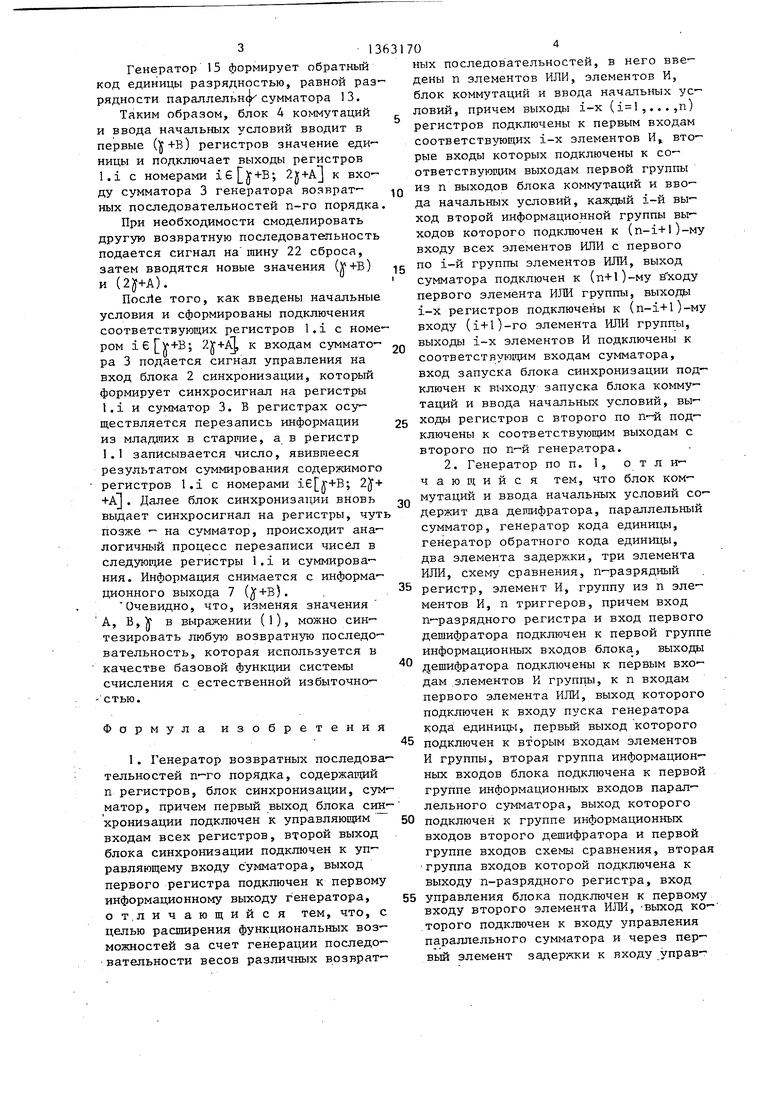

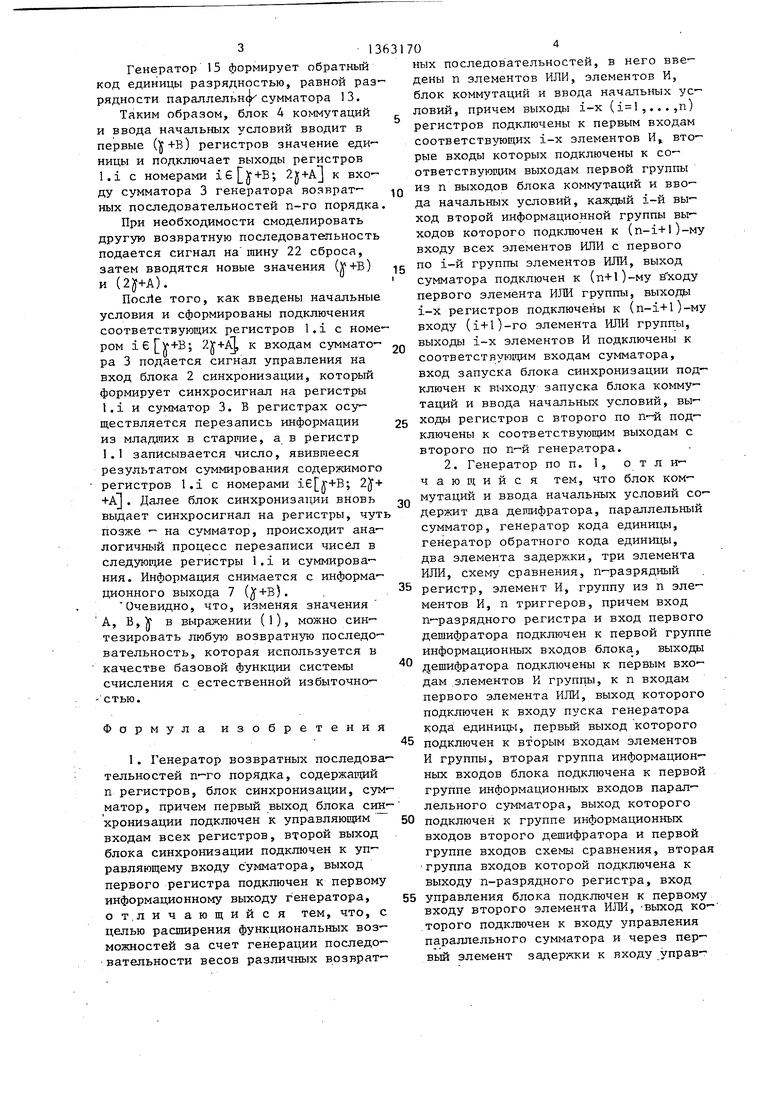

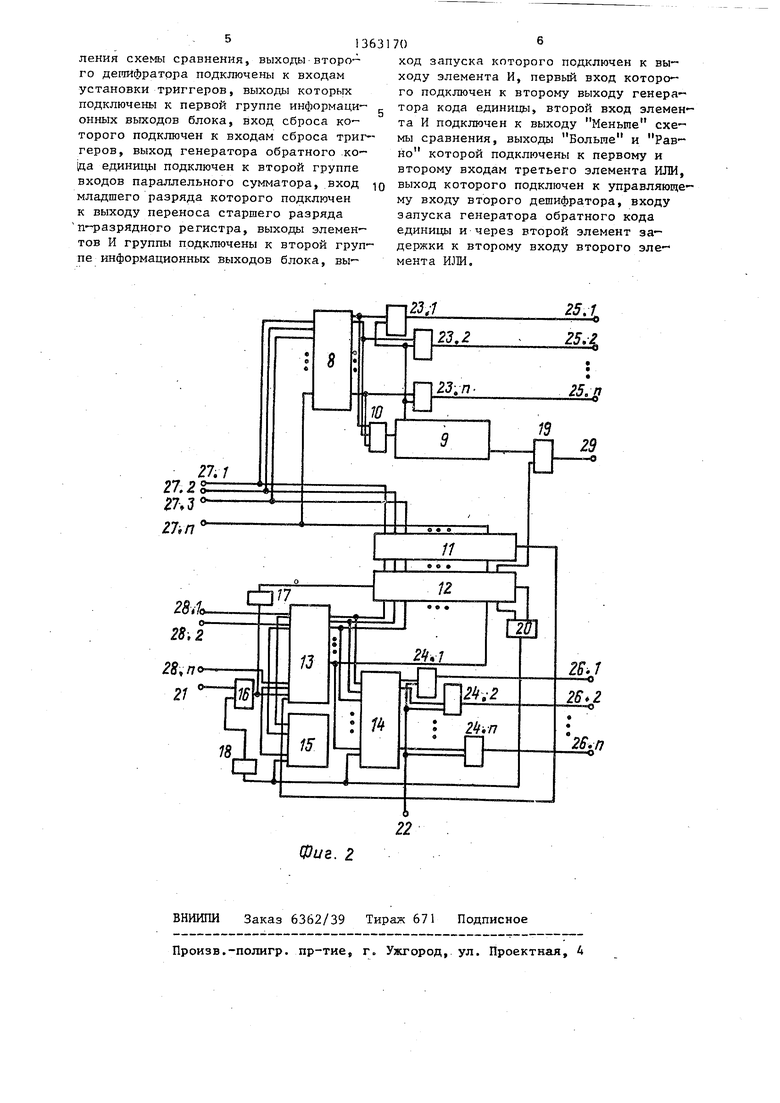

На фиг. 1 изображен генератор возвратных последовательностей п-го порядка; на фиг. 2 - блок коммутаций и ввода начальных условий.

Генератор содержит п разрядных регистров 1.1; 1,2...1,п (где ). блок 2 синхронизации, сумматор 3, бло 4 коммутаций и ввода начальных условий, п элементов И 5.1, 5..2...5.П, п элементов ИЛИ 6.1,6.2...6.П5 ин- формационные выходы 7.1,7.2,.,7.п.

Блок 4 коммутаций и ввода начальны условий содержит первый дешифратор 8 генератор 9 кода единицы, первый элемент ИЛИ 10, п-разрядный регистр 11, схему 12 сравнения, параллельный сумматор 13, второй дешифратор 14, гене- ратор 15 обратного кода единицы, второй, элемент ИЛИ 16, два элемента 17 и 18 задержки, элемент И 19, третий элемент 20, вход 21 управления, вход 22 сброса, группу из п элементов И 23. К..23.п, п триггеров 24.1...24.П первую группу п выходов 25.1...25.П5 вторую группу п выходов 26.1...26.П5 первую группу п входов 27.1...27.П, вторую группу п входов 28.1.. .28.П, выход 29.

Блок 4 коммутаций и ввода начальных условий служит для ввода начальных условий в i первых регистров, а также подключения к сумматору выходов соответствующих регистров 1-п., в зависимости от принятых для данного случая А, В, у .

g

0

If

20

25

зб 40

45

50

55

702

Для того, чтббы рассмотреть работу генератора возвратных последо ватель- ностей п-го порядка, проанализируем сначала работу блока коммутаций и ввода начальных условий.

Блок коммутаций и ввода начальных условий работает следующим образом.

На входные иины 27.1, 27.2...27.п поступает значение (|f+B) в двоичной классической системе счисления, записывается в регистр 11 и поступает на входы дешифратора В. Б зависимости от значения (j+B) на выходе дешифратора 8 с номером (у+В) появляется логическая 1, которая через элемент ИЛИ 10 включает генератор,9 и открывает соответствующий элемен г И .23.1, 23.2...23.п. Генератор 9 выдает последовательным кодом единицу, которая через элемент И поступает на соответствующую выходную шину 25.1, 25.2.. .25 ..п. Тем временем на входные шины 28.1, 28.2...28.п поступает зна- чени.е (2;j +A) в двоичной классической системе счисления и записывается в триггеры параллельного сумматора 13. По сигналу на управляющей шине 21 значение (2J +A) выдается из сумматора 13 на входы схемы 12 сравнения и дешифратора 14. По сигналу с выхода элемента 17 задержки происходит сравнение значений (2Х +А) и (+В) в схеме 12 сравнения, выдается сигнал (25+А) (у+в) ипи() (у+В). Если ()э: (х+В), ТО сигнал через элемент MJM 10 поступает на вход управле- НИН дешифратора 14, на выходе дешиф- ра:тора с номером () появляется сигнал 1, который запоминается соответствующим триггером 24.1 и подключает выходную шнну 26.1. Этим же сигналом запускается генератор 5, которьй выдает параллельным кодом на входы су ;матора 13 обратный код едини1ц 1. По этому же сигналу, задержанному в элементе 18 задержки, происходит вьщача результата на вход схемы 12 сравнения, которая по сигналу с выхода элемента 17 задержки производит сравнение значений (2ХЧ-А-1) и (у+В). Если {2J4-A-1) (J+B), то про- цесс, только что описанный, повторяется до тех пор, пока (2V+A-i) не станет меньше у+Б. В этом случае сигнал поступает на вход элемента И 19. Если генератор 9 уже выдал код 1, то с выхода элемента И .19 по шине 29- включается блок 2 синхронизации генератора.

Генератор 15 формирует обратный код единицы разрядностью, равной разрядности параллельнс сумматора 13.

Таким образом, блок 4 коммутаций и ввода начальных условий вводит в первые (J+B) регистров значение единицы и подключает выходы регистров l.i с номерами , -J+A к входу сумматора 3 генератора возврат- ных последовательностей п-го порядка

При необходимости смоделировать другую возвратную последовательность подается сигнал на шину 22 сброса, затем вводятся новые значения (У+В) и (2у+А).

ПосЛе того, как введены начальные условия и сформированы подключения соответствующих регистров l.i с номером -jf+AJ, к входам суммато- ра 3 подается сигнал управления на вход блока 2 синхронизации, который формирует синхросигнал на регистры l.i и сумматор 3. Б регистрах осу- ществляется перезапись информации из младших в стариие, а в регистр 1.1 записывается число, явившееся результатом суммирования содержимого регистров l.i с номерами ie x +B; 2(5 + +А . Далее блок синхронизации вновь выдает синхросигнал на регистры, чут позже - на сумматор, происходит аналогичный процесс перезаписи чисел в следующие регистры l.i и суммирования. Информация снимается с информационного выхода 7 (+В). .

Очевидно, что, изменяя значения А, В,Х в выражении (1), можно синтезировать любую возвратную последовательность, которая используется в качестве базовой функции системы счисления с естественной избыточностью.

Формула изобретения

1 . Генератор возвратных последовательностей п-го порядка, содержащий п регистров, блок синхронизации, сум- матор, причем первый выход блока син- хронизации подключен к управляющим входам всех регистров, второй выход блока синхронизации подключен к управляющему входу сумматора, выход первого регистра подключен к первому информационному выходу генератора, о т.лич ающий с я тем, что, с целью расширения функциональных возможностей за счет генерации последовательности весов различных возвратQ

g

п 5 д

5

0 5

ных последовательностей, в него введены п элементов ИЛИ, элементов И, блок коммутаций и ввода начальнь х условий, причем выходы i-x (,...,n) регистров подключены к первым входам соответствзпощих i-x элементов И, вторые входы которых подключены к со- ответствуюпщм выходам первой группы из п выходов блока коммутаций и ввода начальных условий, каждый i-й выход второй информационной группы выходов которого подключен к (n-i+l)-My входу всех элементов ИЛИ с первого по i-й группы элементов ИЛИ, выход сумматора подключен к (п+1)-му в ходу первого элемента ИЛИ группы, выходы i-x регистров подключены к (n-i+l)-My входу (i+l)-ro элемента ИЛИ группы, выходы i-x элементов И подключены к соответствующим входам сумматора, вход запуска блока синхронизации подключен к выходу запуска блока коммутаций и ввода начальных условий, выходы регистров с второго по п-й подключены к соответствующим выходам с второго по п-й генератора.

2. Генератор по п. 1, отличающийся тем, что блок коммутаций и ввода начальных условий содержит два дегчифратора, параллельный сумматор, генератор кода единицы, генератор обратного кода единицы, два элемента задержки, три элемента ИЛИ, схему сравнения, п-разрядный регистр, элемент И, группу из п элементов И, п триггеров, причем вход п-разрядного регистра и вход первого дещифратора подключен к первой группе информационных входов блока, выходы дещифратора подключены к первым входам элементов И группы, к п входам первого элемента ИЛИ, выход которого подключен к входу пуска генератора кода единицы, первый выход которого подключен к вторым входам элементов И группы, вторая группа информационных входов блока подключена к первой группе информационных входов параллельного сумматора, выход которого подключен к группе информационных входов второго дешифратора и первой группе входов схемы сравнения, вторая группа входов которой подключена к выходу п-разрядного регистра, вход управления блока подключен к первому входу второго элемента ИЛИ, ВЫход ко- торого подключен к входу управления параллельного сумматора и через первый элемент задержки к входу управления схемы сравнения, выходы-второго депгифратрра подключены к входам установки триггеров, выходы которых подключены к первой группе информаци- онных выходов блока, вход сброса которого подключен к входам сброса триггеров, выход генератора обратного ко- йа единицы подключен к второй группе входов параллельного сумматора, вход младшего разряда которого подключен к выходу переноса старшего разряда п-разрядного регистра, выходы элементов И группы подключены к второй группе информационных выходов блока, выФиг. 2

ВНИИПИ Заказ 6362/39 Тираж 671 Подписное Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, А

ход запуска которого подключен к выходу элемента И, первый вход которого подключен к второму выходу генератора кода единицы, второй вход элемента И подключен к выходу Меньте схемы сравнения, выходы Больше и Равно которой подключены к первому и второму входам третьего элемента ИЛИ, выход которого подключен к управляющему входу второго дешифратора, входу запуска генератора обратного кода единицы и через второй элемент задержки к второму входу второго эле- мента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство для отображения информации | 1986 |

|

SU1410097A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

Изобретение относится к вычислительной технике и предназначено для генерирования последовательностей весов возвратных последовательностей различного порядка. Цель изобретения- расширение функциональных возможностей за оч-ет генерации весов различных возвратных последовательностей. Генератор содержит п резисторов 1, блок 2 синхронизации, сумматор 3, блок 4 коммутаций и ввода начальных условий, п элементов И, п элементов ИЛИ. Поставленная цель достигается за счет введения блока 4 коммутаций и ввода начальных условий п элементов И, -п элементов ИЛИ. 1 з.п. ф-лы, 2 ил.

| Генератор последовательности @ -чисел Фибоначчи | 1983 |

|

SU1091146A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор последовательности обобщенных чисел фибоначчи с произвольными начальными условиями | 1976 |

|

SU662926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-11—Подача