(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня -ой степени | 1977 |

|

SU742929A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Устройство для вычисления функции вида ух | 1975 |

|

SU579612A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Цифровой функциональный преобразователь | 1975 |

|

SU586458A1 |

Иэо етение относится к цифровой вычислителшой технике н может бьпь приметно д;ш аппаратной реализацнн возведения числа одновременно в степень.от первой до N-бй а вычислительных и у1фавляющих устройствах н системах.

Известно устройство для вычислена экспоненциальной функции, coдepжaщeie счетчик, счетчик-регистр, схемы запрета и схему сборки (1).

Это устройство предназиачено для кия только одной функщ1И от аргумента в чио ло-импульсном коде.

Известно устройство для вьршсленкя cteпенных функций, сод жащее реверсивные и суммируюидие счетчики, вентили, триггер, генератор импульсов, множиТельно-делительное устройство 2. В этом устройстве одновременно вычисляется только одна степенная функция.

Известно арифметическое устройство специализированной цифровой вычислительной маишны, содержащее сумматоры, регистры, логические элементы, схемы анализа разрядов, схему вьфаботки цифр частного и т. д. 3. При помощи этого устройства невозможно, одновременно вычислить несколько степенных функций.

Наиболее к изобретению является устройство, позволяющее возводить двоичные числа в степень N н содержащее N 1 регистров (где N - показатель степени), входы сдвига которых соединены с выходами блока управления, первые вькодьт регис ов с первого по (N-1)-й соединены соответственно с первыми входами первого - (N-l)-ro сумматсфов-вычитателей, выходы соеданены соответственно с входами первого - (К-)-го регистров {41.

Известное устройство предназначено для . возведения чисел только в одну степень N за один процесс вычисления и не позволяет одновреме;шо вьршслить все степени до N включителы{о. Кроме того, время вычисления зависит от N.

Целью изобретения является расщирение функционалшых возможностей, заключающееся в одновременном получении всех степеней числа с пфвой по N-ю, а также исключения зависимости быстродействия от значения показателя степени.

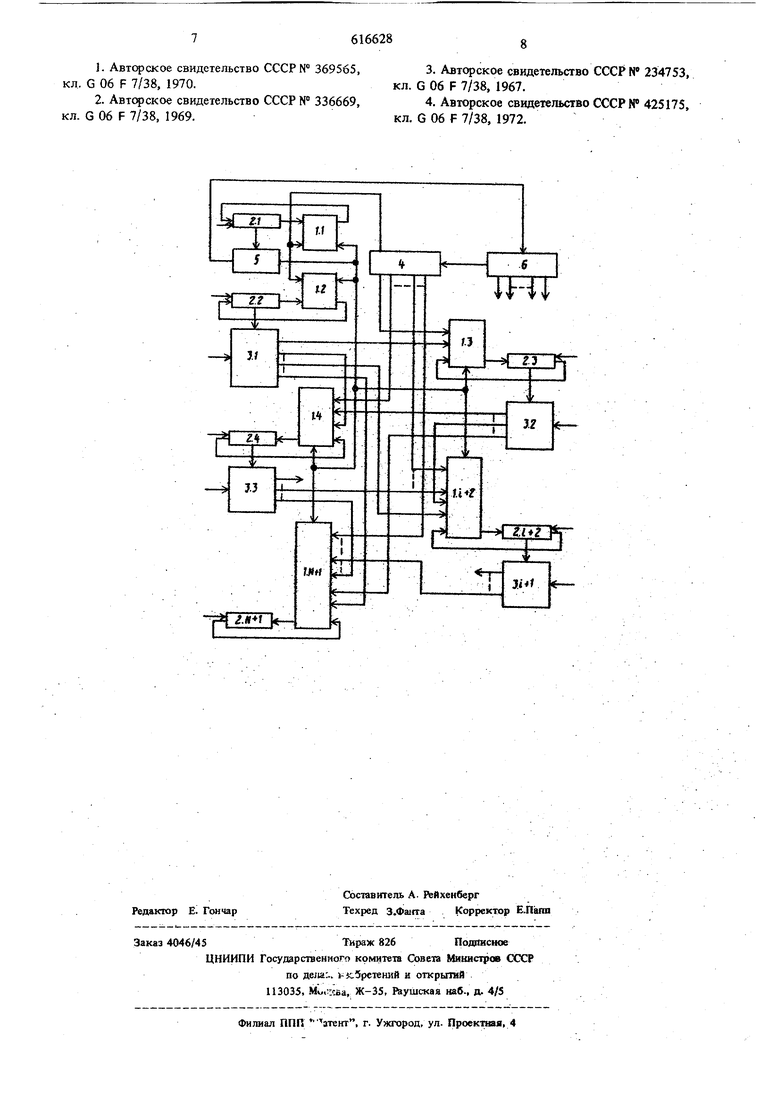

Достигается это тем, что устройство N и (N + 1)-й сулаптсфы-вы вт1т«ли. (N-1) блоков сдвига, блок памяти и блок анализа знака и сходимости, причем второй выход первого регистра соединен с входом блока анализа, знака и сходимести, первый выход которого соединен с входами управления первого - (N )-го.сумматоров-вычитатеяей, второй выход - с входом блока утфавления, вторые выходы второго - N-ro регистров соедшсшы соответственно с первыми входами первого - (N-1)-го блоков сдвига, первый (N-l)-fi выходы пфвого блока сдвига соедине ны соответствекио со вторБПйи входами третьего - (N 1)-го ;Сумматоров-вычитателей, пфвьш - (N-1)-;й выходы i-ro блока сдвига соответственно соединеш) с ( + ) входами (i 2) - (Н + 1)-го c wlмaтqpoв-вычитaтeлeй, выход (N-1)-го блока сдвщ-а соединен с N-M входом (N + 1)-го сумматоровычитателя, пер,вый вход блока ггамяти соединен со вторыми входами первого и втфого cyMMaxqjoB- вычитателей, второй вход - с третьим входом третьего сумматора-вычитателя, -ыйвыход -с (i+l)-M входом (i 1)-го сумматора-вычитателя, N-БШ выход - с (N + 1)-м входом (N + 1)-го сумматфа- вычитателя, вход блока памяти и втфы входы первого - ()-ro блоков сдвига соединены с выходами блока управления. Такое устройство позволяет одновременно получить все степени числа с по N-yro, время вычисления ттосгоянно для любо го значения. N. На чертеже представлена блок-схема устройства для возведения в степень. Устройство содержит сумматоры-вьгчитатели 1.1 - 1.N+1, регистры 2.1 - 2. , бло ки сдвига ЗЛ - 3.N-1, блок памяти 4, блок анализа знака и сходимости 5 и блок управления 6. Первые входы регистров 2.1 -2.N + 1 .соединены с первыми входами сумматоров-вычитателей Ы - l. соответственно, выходы котфьк соответственно соединены с входами этих регистров. Второй выход первого регистра 2.1 соединен с входом блока анализа знака и сходимости 5, первый выход KOTqpoго соединен с входами управления сумматоров вычитателей 1.1 - 1.N+1, а второй выход - с входом блока управления 6. Вторые выходы регистров 2.2 -2. N соединены с первыми входами блоков сдвига 3,1 - 3. N - 1 соответственно. Первый выход блока сдвига 3.1 соединен с вторым входом сумма тора-вычитате ля 1.3, второй вь1ход - с вторым входом сумматора-вычитателя 1.4, i-ый выход - с вторым Входом сумматора-вьмитателя l., а (М-О-й выход - с втфым входом сумматора - вычитателя 1. N + 1. Первый - (М-2)-й выходы второго блока сдвига 3.2 соединены соответственно с третьими входами сумматоров-вычитателей 1.4 - I. N + 1. Первый + (N-i)-й выходы i-ro блока сдвига 3.) соединены соответственно с (i + 1)-м входами сумматоров-вычитателей 1. (i-2) - I. N. Выход блока сдвига 3. N-1 соещшен с N-ым входом сумматора-вычитателя 1. N + 1. Первый выход блока памяти 4 соединен с вторыми входами сумматоров-вычитателей 1.1 и 1.2. По этому выходу выдае::я константа 2, где J- номер итерации. Второй вьрсод блока памяти 4 соединен с третьим входом сумматора-вычитателя 1.3- По этому выходу В})Здается константа 2 . i-ьш выход блока памяти 4 соединен с (i + 1)-м входом су№ матфа-вычитателя 1. i + I, По этому выходу выдается константа 2 . N-й выход блока памяти 4 соеддаен с (N + 1)-м выходом сумматора-вычитателя 1. N 1. Выходы блока управления 6 соединены соответственно со входами сдвига регистров 2.1 - 2. N 1, вторыми входами блоков сдвш-а 3.1 - 3. N-1 и входом блока памяти 4. Входом устройства является вход пфвого регистра 2.1. ВыходЬм устройства для второй степени является выход регистра 2.3, дпя третьей степени - выход регистра 2.4, для Г-и степши - выход регистра 2. i + 1, для N-ой степени - выход регистра 2. N + 1. Вычисление одновременно степени числа с первой по N-ую выполняется по разностнв-. итерационному алгоритму, записанного системой рекуррентных соотношений 2о Z.,-,,--X-X Z, Zh-О a.,,4,V Z.jjO . Т «d i-1 Itynj Z j о o° M. vo .,-л.2. и, W.O 5V.cx3..w. -e -Я и -з-г- л.-з-г- Ч i 2 ..2-Ч 4c.X. 4.2- -2- V -. v° d...- i r -2+ . ..X N-3NCN-t)(N-aj),-ij 35 -+/П N(NH)...(N-m4O ;mj -(.,} .- -,2 f .-.-«,)-S,N2- -Cq) , В описываемом устройстве рекуррентные соотношения вычисляются параллельно. Максимальное количество итераций равно п + 1, где п - число разрядов аргумента X

Первоначально все регистры 2.1 - 1.N + 1 устанавливаются в нулевое состояние. В регистр

С , выходов которого в каждой итерации выдается последовательность (серия) тактовых импульсов.

Вычисления в j-ой кгерации выполняются следующим образом.

Последовательность тактовых импульсов сдвигает подаваемые в блоки сдвига 3.1 3.N-1 содержания соответствующих регистров

Полученные величины с выходов блоков сдвига 3,1-- 3.N-1, константы с выходе блока памяти 4 и содержания регистров 2.2 - 2. N 1 продвигаются поразрядно каждым тактовым импульсом на соответствующие входы сумматоров- вычитатедей; 1.3 : 1. N + 1. На входь сумматоров-вычитателей 1.1 - 1.2 продвигаются содержания регистров 2.1 - 2.2 соответственно и константа с перъото входа блока памяти 4. Результаты суммирования-вычитания с выходов сумматоров-вычитателей 1.1 - l.N заносятся младщими разрядами вперед в освобождающиеся при старшие разряды регистров 2.1 - 2. N + 1 и продвигаются в стог ршу младших разрядов. После каждой итерации в регистрах 2.1 - 2. N + 1 записаны яромежуточные результаты. По знаку содержания регистра 2,1 в блоке анализа знака и сходимости 5 вьфабатывается сигнал«J,., определяющий режим сложения-вычитания по соответствующим входам в сумматорах-вычитателях 1,1 - 1. N + 1.

В следующих итерациях вычисления производятся аналогично.

Особенностью приведенного алгсфитма является то, что при нулевом содфжании регистра

После вьшолнення цикла вычисления, состоящего из п + 1 итераций, или при равенстве нулю содержания регистра 2.1 (в последнем случае со второго выхода блока анализа знака и сходимости 5 на блок управления 6 выдается сигнал останова и выдача тактовых импульсов на следующей итерации прекращается) в регистрах 2.1 - 2. N + 1 соответственно содержатся значения степеней аргументов от первой до N-й включите.тьно. Время одновременного возведения в степень в тактах равно + п (2 m 1), где m - число дополнительных разрядов для компенсащш погрешности при сдвиге.

Сравнителы1ые испытания данного изобретения с известным показали, что изобретение позволяет одновременно получить первую, вторую, третью, ..., N-ю степени числа, причем вре0мя вычисления не зависит от значения N. Это позволяет использовать изобретение в различных вычислительных и управляющих устройствах и системах.

5

Формула изобретения .

Устройство для возведения в степень, содержащее N + 1 регистров (где N - показатель степени), входы сдвига которых соединены с

0 выходами блока управления, первые выходы регистров с первого по (Ы-1)-й соединены соответственно с первмми входами первого (N-1)-го сумматоров-вычитателей, вькоды которых соединены соответственно со входами

5 первого - (N-l)-ro peritcTpoB, отличающееся тем, что, с целью расширения его функцисжалшых возможностей, закл1очаю1цегося в одаойремшном получении всех степеней числа с по N-ю,. устройство содержит

0 N и (N + 1)-й суМматоры-вычитатели, (N-1) блоков сдвига, блок памяти и блок анализа зиака и сходимости, причем втсрой выход первого регистра соещмен с входом блока анализа знака и сходимости, пер1вый выход которого

5 соеданен с входами управления первого - (N-i-l)-ro сумматсрой-вычитателей, второй выход - сО входом блока упрзвлен1{я, ъгарые выходы второго - М-го регистров соединены соотвётствейно с первыми входами первого - (N-1)-го блоков сдаий, первый - (N-l)-й выходы первого блока сдвига соедашены соответственно со BTqpbJMH входами третьего - (N + 1)-го сумматоров-вьрштатепей, первый - (N-)-й выходы i-ro блока сдвига соответствен5но соединены с (t + 1) входами (t + 2) - N-ro сумматфов-вычитателей, выход (N-l)-ro блока сдвига соединен с N-ым входом (N + 1)-го сумматора-вычитателя, первьп выход блока памяти соединен со вторыми входами первого и второ0го сумматоров-вычитателей, второй выход - с третьим входом третьего сумматора-вычщателя, t-й выход - с (i + i)-M входом (i + 1)-го сумматора-вьтитателя, N-ый выход - с (N + 1)-ым входом (М-)-го сумматс а-вычитателя, вход

5 блока памяти и втфые входы первого - (М-1) -го блоков сдвига сое;щнены с выходами блока управления.

Источники инфс мации, принятые во внимание при экспертизе: 1.ABTq cKoe свидетельство СССР № 369565, кл. G 06 F 7/38, 1970. 2.Авторское свидетельство СССР№ 336669, кл. G 06 F 7/38, 1969. 3. Авторское свидетельство СССР N 234753, кл. G 06 F 7/38. 1967. 4. Авторское свидетельство CCCPN 425175, кл. G 06 F 7/38, 1972.

Авторы

Даты

1978-07-25—Публикация

1975-08-07—Подача