области. Результат решения отыскивается вручную нуль-методом.

Однако это устройство обладает невысоким быстродействием в связи с необходимостью вручную отыскивать решение нуль-методом, а также невысокой (аналоговой) точностью решения конечно-разностных уравнений.

Цель изобретения - повышение быстродействия и точности решения.

Поставленная цель достигается тем, что в устройство для решения дифферен циальных уравнений в частных производных дополнительно введены аналоговый запоминающий блок, блок ключей, функциональный преобразователь, цифровой вычислительный блок, блок памяти и блок управления, причем вход устройства соединен с первыми входами блока памяти и блока управления, второй выход аналогового процессора подключен к первому входу блока ключей, первый выход которого соединен со вхойом аналогового запоминающего блока, выход которого подключен ко второму входу аналогового процессора, второй выход блока ключей соединен со вторым входом блока памяти и первым входом функционального преобразователя, выход которого подключен ко второму-входу блока ключей, первый выход блока памяти соединен со вторым входом функционального преобразователя, второй выход блока памяти подключен к первому входу цифрового вычислительного блока и ко второму входу блока управления, первый выход которого соединен с третьим входом блока памяти, второй выход блока управления соединен с третьими входс1ми функционсшьного преобразователя, блока ключей и со вторым входом цифрового вычислительного блока, выход которого подключен к четвертому входу блока памяти, третий выход которого является выходом устройства, кроме, того, блок управления содержит дешифратор адреса, дешифратор сзперации, генератор тактовых импульсов, счетчик и регистр, причем выход генератора такtoBfcix импульсов соединен с первьол входом счетчика, выход крторого подключен ко входу дешифратора гщреса, выход которого является перйым выходом блока управления, второй вход счетчика и вход регистра являются вторлм входом блока управления, первым входом которого является третий вход счетчика, выход регистра подключен ко входу дешйфрШорй Ь1Ш1сШСйй, йыхой которого является вторьм выходом блока управления. Цифровой вычислительный блок содержит накапливгиощий сумматор, коммутатор, умножитель, два регистра и дешифратор операции, причем первый вход цифрового вычислительного блока соединен с первыми , входами регистров и дешифратора операций, второй вход которого является

вторым входом цифрового вычислительного блока, выход дешифратора операции подключен ко вторым входам регисров и к первым входам коммутатора, умножителя и накапливающего сумматора, выход первого регистра соединен со вторым входом коммутатора, выход которого подключен ко второму входу умножителя, выход второго регистра соединен с третьим входом умножителя выход которого подключен ко второму входу накапливающего сумматора, выход которого соединен с третьим входом коммутатора и является выходом цифрового вычислительного блока.

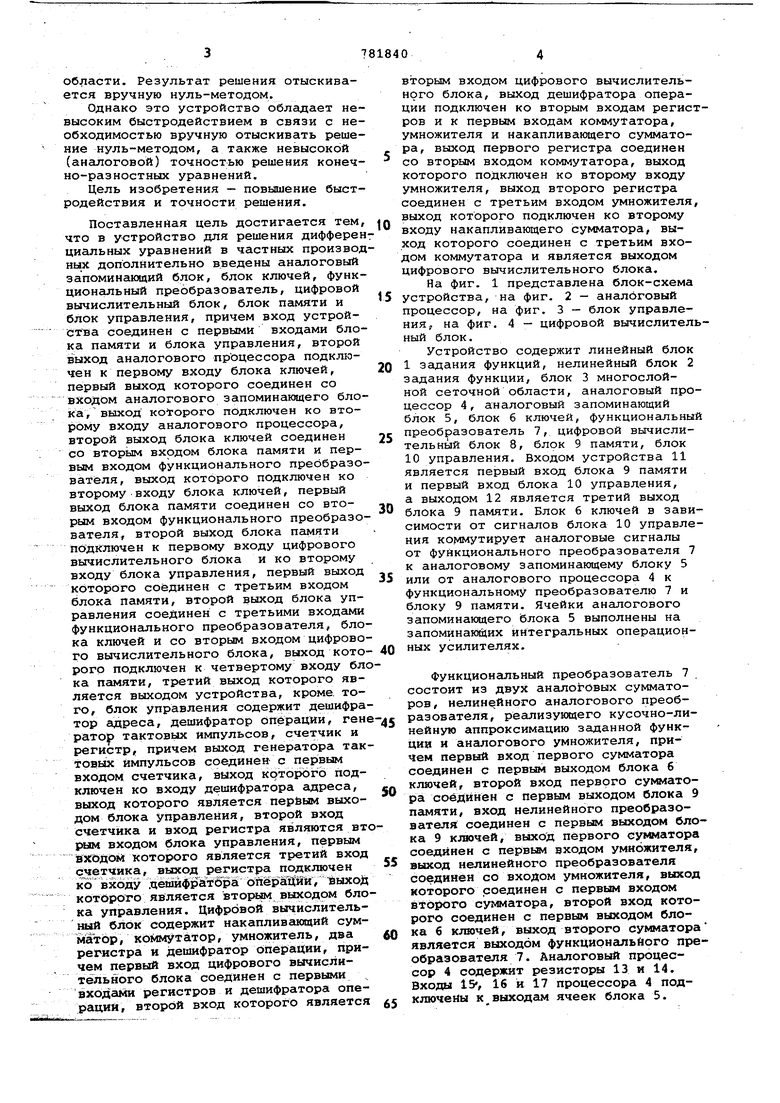

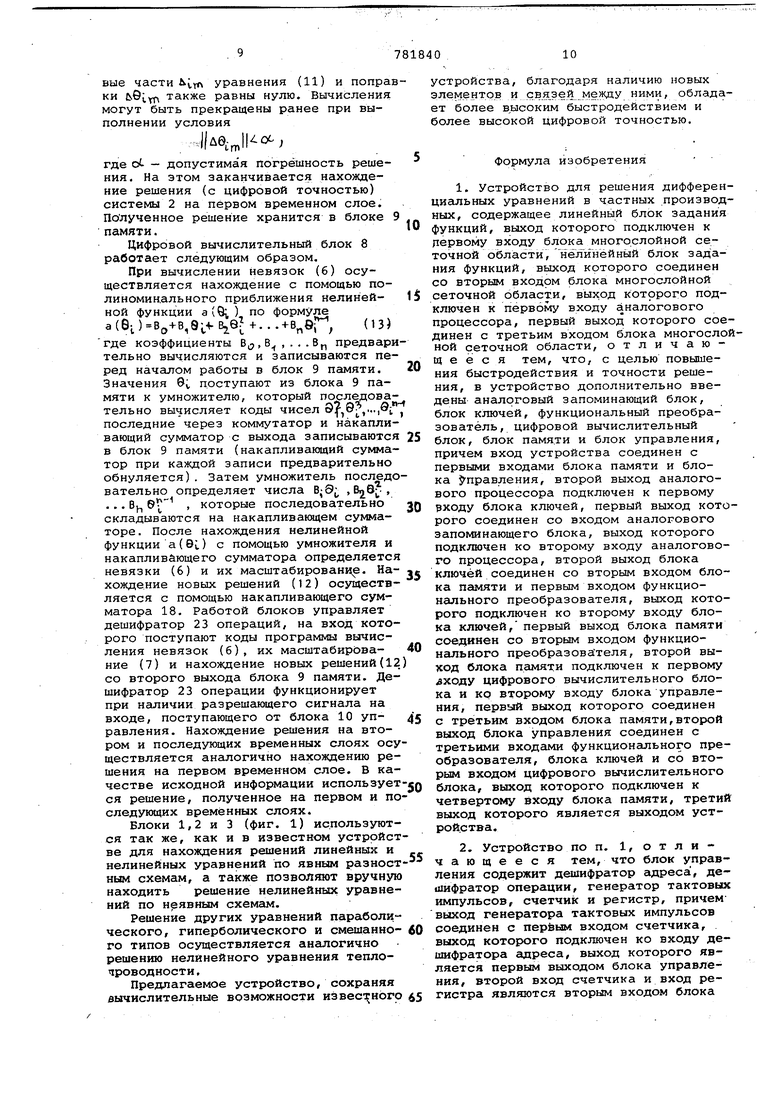

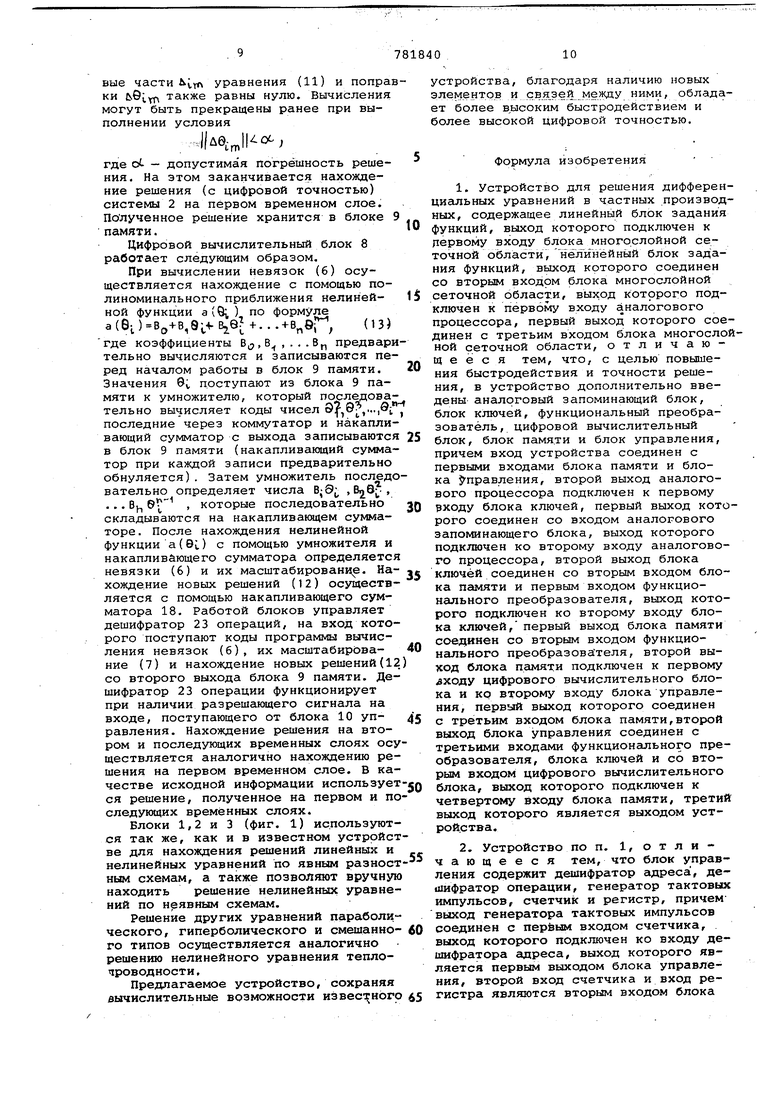

На фиг. 1 представлена блок-схема устройства, на фиг. 2 - аналоговый процессор, на фиг. 3 - блок управления, на фиг. 4 - цифровой вычислителный блок.

Устройство содержит линейный блок 1 Эсодания функций, нелинейный блок 2 задания функции, блок 3 многослойной сеточной области, аналоговый процессор 4, аналоговый запоминающий блок 5, блок б ключей, функциональны преобразователь 7, цифровой вычислительный блок 8, блок 9 памяти, блок 10 управления. Входом устройства 11 является первый вход блока 9 памяти и первый вход блока 10 управления, а выходом 12 является третий выход блока 9 памяти. Блок 6 ключей в зависимости от сигналов блока 10 управления ко лмутирует аналоговые сигналы от функционального преобразователя 7 к аналоговому запоминающему блоку 5 или от аналогового процессора 4 к функциональному преобразователю 7 и блоку 9 памяти. Ячейки аналогового запоминающего блока 5 выполнены на зап6минакй1их интегральных операционных усилителях.

Функциональный преобразователь 7 состоит из двух анс1ло1гОвых сумматоров, нелинейного аналогового преобразователя, реализующего кусочно-линейную аппроксимацию заданной функции и аналогового умножителя, причем первый вход первого сумматора соединен с первым выходом блока 6 ключей, второй вход первого cyNwaTOра соединен с первым выходом блока 9 памяти, вход нелинейного преобразователя соединен с первым выходом блока 9 ключей, выход первого сумматора соединен с первьвл входом умножителя, выход нелинейного преобразователя соединен со входом умножителя, выход которого соединен с первым входом второго сумматора, второй вход которого соединен с первым выходом блока б ключей, выход второго сумматора является выходом функциональйого преобразователя 7. Аналоговый процессор 4 содержит резисторы 13 и 14. Входы 15, 16 и 17 процессора 4 подключены к выходам ячеек блока 5. Цифровой вычислительный блок 8 (фиг. 4) содержит накапливающий сумматор 18,коммутатор 19, умножитель 20, два регистра 21, 22 и дешифратор 23 операции, причемпервые входы регистров и дешифратора операций соединены со вторым выходом блока 9 памяти, второй вход дешифратора операций соединен со вторым йыходом блока 10 управления, выход дешифратора опер ций соединен с первыми входами комм Г татора, умножителя, накапливающего сумматора и со вторыми входами регист ров/ второй вход коммутатора соединен с выходом накапливакицего сумматора, выход коммутатора соединен со вторьзм входом умножителя, выход которого сое динен со вторым входом накапливакяцего сумматора, выход первого регистра сое динен с третьим выходом умножителя, выход второго регистра соединен с третьим входом коммутатора, выходом цифрового вычислительного блока является выход накапливающего сумматора. Блок 9 памяти содержит ячейки для хранения цифровых кодов, аналого-цифровой преобразователь преобразования информации от аналогового процессора 4 и цифроаналоговый преобразователь для преобразования кодов, поступающих к функциональному преобразователю 7. Блок 10 управления (фиг. 3) включает дешифратор 24 гщреса, дешифратор 25 операции, генератор 26 тактовых им пульсов, счетчик 27 и регистр 28. При чем выход генератора тактовых импульсов соединен с первым входом счетчика, второй вход которого и вход регистра соединены со вторьм выходсж блока 9 памяти, выход счетчика соединен со входом дешифратора адреса, выход которого соединен с третьим входом блока 9 памяти, выход регистра соединен со входом дешифратора операции, выход которого соединен с третьи входом блока б ключей, с третьим входом функционального преобразователя 7 и со вторым входом цифрового ВЫЧИСЛИ:тельного блока 8. При решении дифференциальных уравнений в частных производных блок 10 управления реализует следующие операции: ввод информации в аналоговый про цессор 4, съем информации из аналогового процессора 4 и совместная работа с цифровым вычислительным бло.ком 8. Реализация этих опе1раций осуществляет ся с помощью подпрограмм, хранимых в блоке 9 памяти. Для того, чтобы соста вить в целом програтФлу работы предлаг емого устройства, необходимо составит последовательность выполнения подпрограмм, записать эту последовательность в блок 9 памяти и перед началом работы в счетчике управления установить начальный адрес программы. При этом возбуждается шина дешифратора адреса, соответствукяцая начальному ад ресу программы и из блока 9 памяти Б счетчик записывается начальный адрес массива кодов чисел Э;, , д , а в регистр- сод, который соответствует номеру начальной ячейки аналогового запоминающего блока 5. В резульDU1 W ланиишпсиищег/и jJlUKa :j, о pnyyjli гате считываются коды чисел 9° , тате RJ4 и поступают в функциональный преобразователь 7, который воспроизводит напряжение 4, последнее через блок 6 ключей, управляемых от. дешифратора операций, записывается в ячейку блока 5, номер которой был записан и регистре блока управления. С приходом следующего тактового импульса содержимое счетчика увеличивается на единицу и вьвиеопИсанные операции повторяются, в результате которых из блока 9 памяти считывается код числа 0f4 и напряжение, воспроизводимое блоком 7, через блок б записывается в следующую ячейку аналогового запоминшощего блока 5 и т.д. до тех пор, пока из блока 9 памяти не будет считан весь указанный в программе массив чисел. Для съема информации в счетчике 19 устанавливается начальный адрес ячейки блока 9 па /1яти, начиная с которой в блоке 9 памяти записывается массив информации из аналогового процессора. Управление ключами в блоке 6 ключей осуществляется от дешифратора операций по коду , записанного в регистре блока управления. В дальнейшем с приходом каждого тактового импульса из аналогового процессора 4 в блок 9 Пс1мяти записывается одно из значений решение до тех пор, пока не будет снят из процессора 4 весь указанный в програкиче массив чисел. При совместной работе с цифровым вычислительным блоком 8 блок 10 управления с псичощью счетчийа и дешифратора адреса выбирает из блока 9 памяти операнды, необходимые для работы цифрового блока 8. Работу устройства рассмотрим на примере решения нелинейного уравнения теплопроводности (в)|% Неявная конечно-разностная 1 уравнения имеет вид er-«i «r(9rYC-i ;): (-2,2N(2) Для моделирования системы 2 уравнений аналоговый процессор 4 собирается по схеАЮ (фиг. 2). Входы 15, 16 . и 17 аналогового процессора 4 соединены с выходами ячеек аналогового запсяхганаихцего блока 5. Соотношение ве- . личин резисторов 13 14, найденное из сравнения разностного уравнения 2 с уравнением потенциалов, для схемы (фиг. 2) должно равняться &ДЗ 41. - (Г ) Нц Дх: где рг,7 - численное значение сопротивлений 13, Кц - численное значение сопротив лений 14. Из формулы (3), выбирая сопротивле ния R,-ij постоянными, получаем закон изменения сопротивлений V 4t-r/-(L . (За) Моделирование нелинейных сопротивлений R,. осуществляется путем измене ния по определенному закону напряжений, записываемых в ячейки аналогового запоминающего блока 5, выходы кото рых соединены со входами линейных сопротивлений 14, а именно -ftlLH 14 М .a/eritet -e,-), (41 -Rvbi; где и -напряжение, записанное в .ячейку аналогового запоминающего блока, выход которо соединен со входом сопротив ления 14, включенного в 1-и узел аналогового процессора -численное значение линейных сопротивлений 14, заменяющие нелинейные сопротивления R|4 . Напряжение U;, определяемое формулой (4), получено из урайнения равенства токов, протекающих по нелинейному сопротивлению включенного одним концом в i-й узел аналогового процессора 4 (фиг. 2), а на второй конец по дается напряжение и по линейному сопротивлению R, включенного также одним концом в i-й узел аналогового процессора 4 (фиг. 2), а на второй конец подается напряжение U т.е. из уравнения ,. &11 - UI 9i -QI 1-Ме (ои югиолепие определяется формулой (3) , а напряжение - напряжение i-ro узла ансшогового процессора 4 (фиг. 2). Таким образом, из постоянных резис торов 13 и 14 собирается аналоговый процессор 4 (фиг. 2). Функциональный преобразователь 7 настраивается на ре ализацию зависимости (4). В блок 9 па мяти записываются программа работы устройства, начальные и граничные условия (Gf, ,1 ,2. . .N+1), а также коды, численно равные значениям Яц-6.Л/(й - .. ) по числу отыскиваемых их. ,2. . .N) . Осущестнеизвестныхвляется пуск устройства. Блок 10 управления подает импульсы считывания в блок 9 памяти, в котором считываются коды чисел 9-J,R и посту пают в функциональный преобразователь 7, который воспроизводит напряжение, последнее через блок б ключей записывается в ячейку аналогового запоминающего блока 5, выход которого соединенс резистором 14, включенным в i-й узел аналогового процессора 4. Далее в блоке памяти считывается код числа ®U , и повторяются вышеописанные операции. После считывания кода числи блок 10 управления подает импульс на считывание кода числа 9f и начинается новый цикл уравновешивания. По завершению определенного количества циклов уравновешивания в узлах аналогового процессора 4 устанавливаются напряжения, соответствующие решению конечно-разностной системы 2. Полученное аналоговое решение &|(i 1,2,.,.N) через блок 6 ключей записывается в блок 9 памяти. Далее цифровой вычислительный блок 8 вычисляет невязки .). i 1,2...М(6) осуществляет их масштабирование rPi4. i 1 , 2 , . . . N , (7) где MI -- масштабный коэффициент. Величины записываются в ячейки блока 9 памяти. Аналогично тому, как выше описано решение системы 2 на первом временном слое, осуществляется решение системы ,.(9;.) (81 Решение системы }Я, Д 0-( (i 1 , 2 , . . . N) через блок ключей записывается в блок 9 памяти и цифровой вычислительный блок 8 демасштабирует решение ) и определяет новое решение . Дальнейшие вычисления производятся по схеме с использованием формул, аналогичных 6-9. На т-й итерации вычисляются величины Л; «КтЕ: 4tfl где })(Y( масштаб m-й итерации. Решается система уравнения Stm-4m- ) ( ®6м тВычисляется (m+l)-e приближение решения , 9-/ xs.Q. -«-вМ 5 iCm4-il vm iw 2/ Поправки Л 9 в узлах аналогового процессора 4 появляются в связи с тем, что в ячейки блока 9. памяти записываются невязки Ь,гП увеличенные масштабом Н С увеличением числа итераций m масштабы и возрастают и поправки й9;уп уменьшаются по абсолютной величине. Вычисления прекращаются в том случае, когда невязки g-j обращаются в машинныв нули цифрового вычислительного блока 8, При этом пра

вые части (.ул уравнения (11) и поправки бб;, также равны нулю. Вычисления могут быть прекращены ранее при выполнении условия

...

где С5 - допустимая погрешность решения. На этом заканчивается нахождение решения (с цифровой точностью) системы 2 на первом временном слое. Полученное решение хранится в блоке 9 памяти.

Цифровой вычислительный блок 8 работает следующим образом.

При вычислении невязок (6) осуществляется нахождение с помощью полиноминального приближения нелинейной функции 3(9;,) по формуле а(6)В(,+В,...+В„в-, (13)

где коэффициенты Bjj , В , . . . В, предварительно вычисляются и записываются перед началом работы в блок 9 памяти. Значения 9 поступают из блока 9 памяти к умножителю, который последовательно вычисляет коды чисел Э,®, последние через коммутатор и накапливающий сумматор с выхода записываются в блок 9 памяти (накапливающий сумматор при каждой записи предварительно обнуляется). Затем умножитель последовательно определяет числа Bj9, , 626 , . .. Bj Э , которые последовательно складываются на накапливающем сумматоре. После нахождения нелинейной функции а (Bi.) с помощью умножителя и накапливающего сумматора определяется невязки (6) и их масштабирование. Нахождение новых решений (12) осуществляется с помощью накапливающего сумматора 18, Работой блоков управляет дешифратор 23 операций, на вход которого поступают коды программы вычисления невязок (б), их масштабирование (7) и нахождение новых решений (12. со второго выхода блока 9 памяти. Дешифратор 23 операции функционирует при наличии разрешающего сигнала на входе, поступающего от блока 10 управления. Нахождение решения на втором и последующих временных слоях осуществляется аналогично нахождению решения на первом временном слое. В качестве исходной информации использует ся решение, полученное на первом и последующих временных слоях.

Блоки 1,2 и 3 (фиг. 1) используются так же, как и в известном устройстве для нахождения решений линейных и нелинейных уравнений по явным разностным схемам, а также позволяют вручную находить решение нелинейных уравнений по неявным схемам.

Решение других уравнений параболического, гиперболического и смешанного типов осуществляется аналогично решению нелинейного уравнения теплопроводности ,

Предлагаемое устройство, сохраняя вычислительные возможности известного

устройства, благодаря наличию новых элементов и между ними, обладает более высоким быстродействием и более высокой цифровой точностью.

Формула изобретения

1.Устройство для решения дифференцисшьных уравнений в частных производных, содержащее линейный блок задания функций, выход которого подключен к первому входу блока многослойной сеточной области, нелинейный блок задания функций, выход которого соединен со вторым входом блока многослойной сеточной области, выход которого подключен к первому входу аналогового процессора, первый выход которого соединен с третьим входом блока многослоной сеточной области, отличающееся тем, что, с целью повышения быстродействия и точности решения, в устройство дополнительно введены аналоговый запоминающий блок, блок ключей, функциональный преобразователь, цифровой вычислительный блок, блок памяти и блок управления, причем вход устройства соединен с первыми входами блока памяти и блока правления, второй выход аналогового процессора подключен к первому ВХОДУ блока ключей, первый выход которого соединен со входом аналогового запоминающего блока, выход которого подключен ко второму входу аналогового процессора, второй выход блока ключей соединен со вторым входом блока памяти и первым входом функционального преобразователя, выход которого подключен ко второму входу блока ключей, первый выход блока памяти соединен со вторым входом функционального преобразователя, второй выход блока памяти подключен к первому лходу цифрового вычислительного блока и ко второму входу блока управления, первый выход которого соединен

с третьим входом блока памяти,второй выход блока управления соединен с третьими входами функционального преобразователя, блока ключей и со вторым входом цифрового вычислительного блока, выход которого подключен к четвертому входу блока памяти, третий выход которого является выходом устрой.ства.

2.Устройство по п. 1, отличающееся тем, что блок управления содержит дешифратор адреса , дешифратор операции, генератор тактовых импульсов, счетчик и регистр, причем выход генератора тактовых импульсов соединен с первым входом счетчика, выход которого подключен ко входу дешифратора адреса, выход которого является первым выходом блока управления, второй вход счетчика и вход регистра являются вторым входом блока

управления, первым входом которого является третий вход счетчика, выход регистра подключен ко входу дешифратора операции, выход которого является вторым выходом блока управления.

3. Устройство по .п. 1, о т л и чающееся тем, что цифровой вычислительный блок содержит накапливающий сумматор, ко «4утатор, умножигель, два регистра и дешифратор операции, причем первый вход цифрового вычислительного блока соединен с первыми входгши регистров и дешифратора опе1; щии, второй вход которого является вторым входом цифрового вычислительного блока, выход дешифратора операции подключен ко вторым входам регистров и к первым входам коммутатора, умножителя и накапливеиощёго сумматора, выход первого регистра соединен со вторым входом коммутатора, выход которого подключен ко второму входу умножителя, выход второго регистра соединен с третьим входом умножителя, выход которого подключен ко 5 второму входу накапливающего сумматора, выход которого соединен с третьим входом коючутатора и является выходом цифрового вычислительного блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 363992, кл. G 06 G 7/44, 1973,

2.Дзнбалов Ю.И., Жеребетьев Н.Ф., Лукьянов А.Т., Гуленбаев М.Б. Разра5 бртка и применение статических электроинтеграторов. Проблемы электроники и вычислительной техники, К., Наукова думка, 1976, с. 208 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей | 1986 |

|

SU1325516A1 |

| ОПТИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА, А ТАКЖЕ ОПТИЧЕСКИЙ ПОДБЛОК ПОЛИХРОМАТИЧЕСКИХ ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАНИЙ И ОПТИЧЕСКИЙ УПРАВЛЯЕМЫЙ ТАКТОВЫЙ ГЕНЕРАТОР ДЛЯ НЕЕ | 2005 |

|

RU2297026C1 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| Устройство для цифровой фильтрации | 1983 |

|

SU1109889A1 |

| Гибридное устройство для решения систем дифференциальных уравнений | 1977 |

|

SU662950A1 |

| Следящий аналого-цифровой преобразователь | 1989 |

|

SU1674371A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

IS

П

13

Фиг.2

Авторы

Даты

1980-11-23—Публикация

1979-02-13—Подача