Изобретение относится к области вычислительной техники и предназначено для решения дифференциальных уравнений в частных производных.

Целью данного предложения является повышение быстродействия„

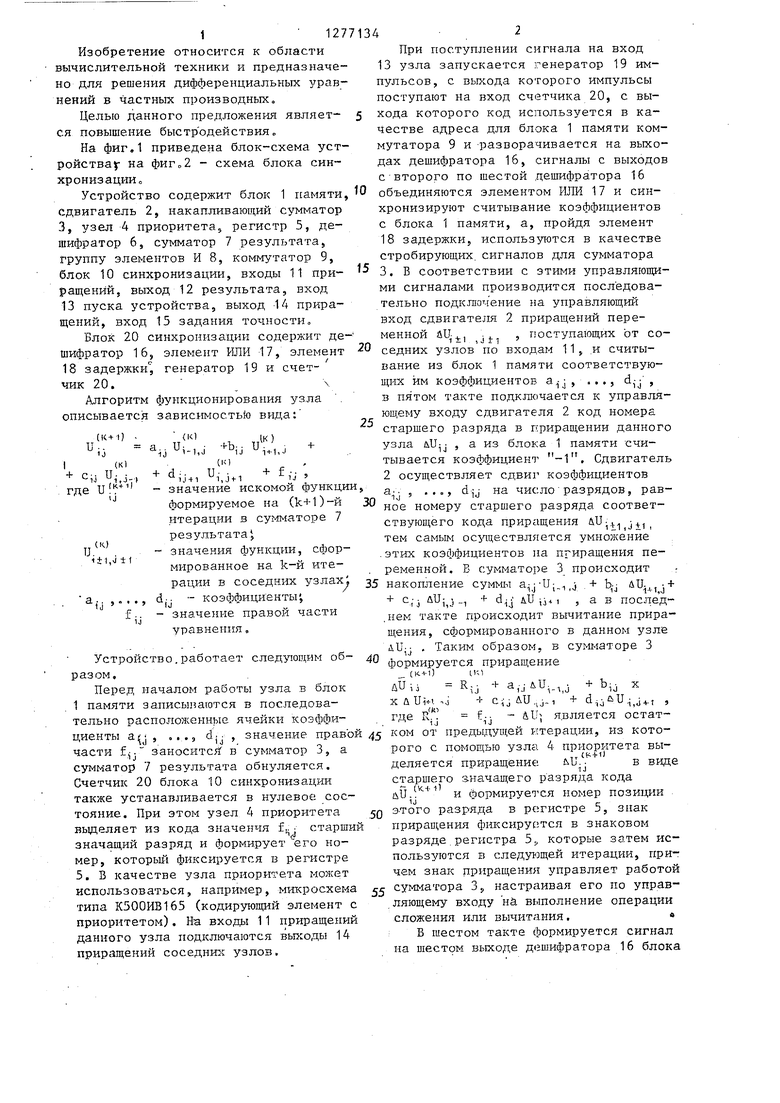

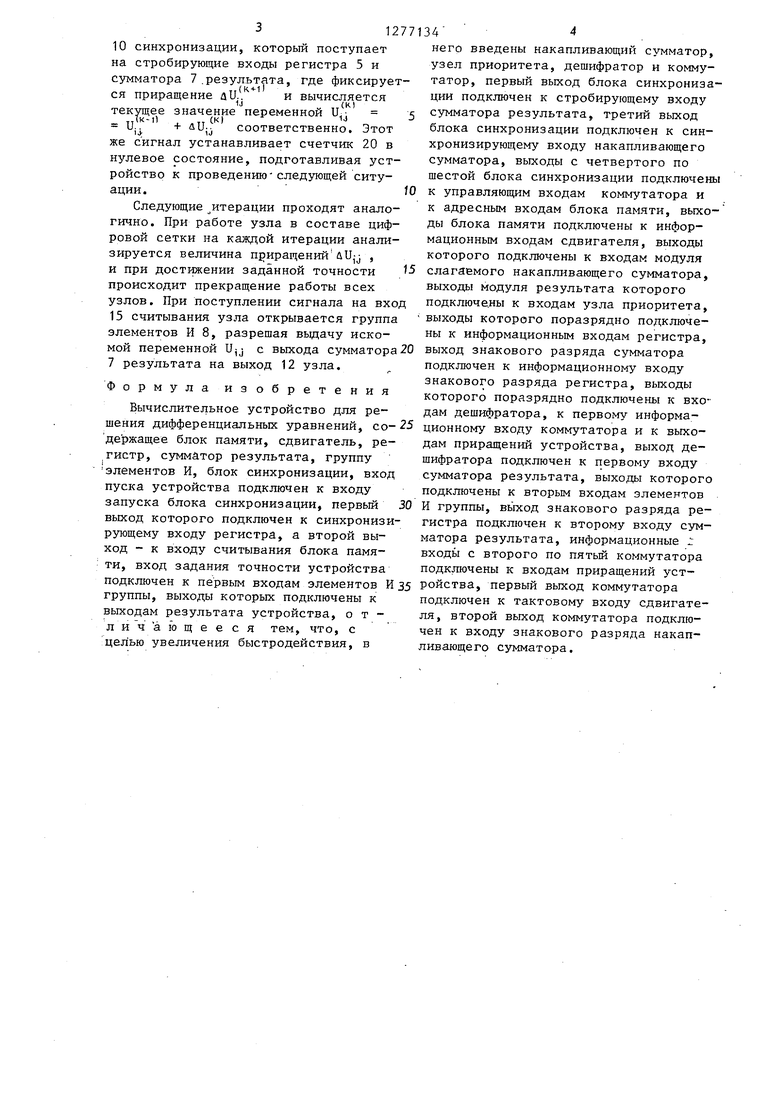

На фиг.1 приведена блок-схема уст- ройства)р на фиг „2 - схема блока синхронизации,,

Устройство содержит блок 1 памяти сдвигатель 2, накапливающий сумматор 3, узел 4 приоритета, регистр 5, дешифратор 6, сумматор 7 результата. Группу элементов И 8, коммутатор 9, блок 10 синхронизации, входы 11 приращений, выход 12 результата, вход 13 пуска устройства, выход -14 приращений, вход 15 задания точности.

Блок 20 синхронизации содержит де шифратор 16, элемент ИЛИ 17, элемент 18 задержки, генератор 19 и счетчик 20.

Алгоритм функционирования уала , описывается зависимость вида:

(К+1) .

Ui3 (К) CU U,-,j , де Uj

к)

а.. U; и

bJ

-bi.

и,

l + bJ

+ f.

и.

(к)

1±1,ч1 ±1

и

и

+ iij + i ijtl -и

-значение искомой функции,

формируемое на (k+l)-u итерации в су -таторе 7 результата

значения функции, сформированное на k-й итерации в соседних узлах

dj. - коэффициенты;

-значение правой части уравнения,

Устройство.работает следующим об- 40 разом.

Перед началом работы узла в блок 1 памяти записываются в последовательно расположенные ячейки коэффициенты ау , ., . J dj части f(j заносите в сумматор 3, а сумматор 7 результата обнуляется, Счетчик 20 блока 10 синхронизации также устанавливается в нулевое состояние. При этом узел 4 приоритета выделяет из кода значения ц старший значаш,ий разряд и формирует его номер, который фиксируется в регистре 5. В качестве узла приоритета может использоваться, например, микросхема j типа К500ИВ165 (кодирующий элемент с приоритетом). На входы 11 приращений данного узла подключаются вьшоды 14 приращений соседншс узлов,

IJ i,j-1 ij aij u+1 , a в последнем такте происходит вычитание прира- ш,ения, сформированного в данном узле AUy , Таким образом, в сумматоре 3 формируется приращение

(К. + 1)

uU U R.--. + а.-; AU;, ., + Ъ;-, X

X д Ui-i-r

R .:

и

+ с.&и,,

г:

1 j

и + d,-,uU.

id - i,il-H

где К.. t-- - 4U; является остатзначение правой 45 предыдущей итерации, из которого с

помощью узла 4 приоритета вы.- (+1) деляется приращение &L.j в вид

старшего аначащего разряда кода

- ( V 4 -} 1

uU.. и формируется номер позиции jQ этого разряда в регистре 5, знак приращения фиксируется в знаковом разряде регистра 5., которые затем ис пользуются в следующей итерации, при чем знак цриращения управляет работой сумматора 3., настраивая его по управ ляющему входу на выполнение операции сложения или вычитания.«

: Б шестом такте формируется сигнал на шестом вь1ходе дешифратора 16 блок

5

0

При поступлении сигнала на вход 13 узла запускается генератор 19 импульсов, с выхода которого импульсы поступают на вход счетчика 20, с выхода которого код используется в качестве адреса для блока 1 памяти коммутатора 9 и -разворачивается на выходах дешифратора 16, сигналы с выходов с Второго по шестой дешифратора 16 объединяются элементом ИЛИ 17 и синхронизируют считывание коэффициентов с блока 1 памяти, а, пройдя элемент 18 задержки, использзпотся в качестве стробирующих. сигналов для сумматора 3. В соответствии с этими управляющими сигналами производится последовательно подключение на управляющий вход сдвигателя 2 прираш;ений переменной AUj-j., jj. , поступающих от соседних узлов по входам 11, .и считывание из блок 1 памяти соответствующих им коэффициентов а,

Ч

d,-y ,

5

30

. . ,

в пятом такте подключается к управляющему входу сдвигателя 2 код номера старшего разряда в приращении данного узла iUy , а из блока 1 памяти считывается коэффициент -1, Сдвигатель 2 осуществляет сдвиг коэффициентов а|. , ,.., на число разрядов, равное номеру cTapuiero разряда соответствующего кода приргщения &U, j, тем самым осзадествл5гется умножение .этих коэффициентов па пгиращения переменной. В сумматоре 3 происходит г

5 накопление суммы а

+ С;.. uU;

U;

1,J i-i.J

- dq AU ii,

b,-.

и,и,о +

0

j

+

IJ i,j-1 ij aij u+1 , a в последнем такте происходит вычитание прира- ш,ения, сформированного в данном узле AUy , Таким образом, в сумматоре 3 формируется приращение

(К. + 1)

uU U R.--. + а.-; AU;, ., + Ъ;-, X

X д Ui-i-r

R .:

и

+ с.&и,,

г:

1 j

и + d,-,uU.

id - i,il-H

где К.. t-- - 4U; является остат45 предыдущей итерации, из которого с

предыдущей итерации, из которого с

помощью узла 4 приоритета вы.- (+1) деляется приращение &L.j в виде

старшего аначащего разряда кода

- ( V 4 -} 1

uU.. и формируется номер позиции этого разряда в регистре 5, знак приращения фиксируется в знаковом разряде регистра 5., которые затем используются в следующей итерации, причем знак цриращения управляет работой сумматора 3., настраивая его по управляющему входу на выполнение операции сложения или вычитания.«

Б шестом такте формируется сигнал на шестом вь1ходе дешифратора 16 блока

10 синхронизации, который поступает на стробирующие входы регистра 5 и сумматора 7 .результата, где фиксируется приращение all.. и вычисляется текущее значение переменной U,;

1К--11(к)и и.. + ли.., соответственно. Этот

1J-и

же сигнал устанавливает счетчик 20 в нулевое состояние, подготавливая устройство к проведению следующей ситуации.

Следующие итерации проходят аналогично. При работе узла в составе цифровой сетки на каждой итерации анализируется величина приращений , и при достижении заданной точности происходит прекращение работы всех узлов, При поступлении сигнала на вхо 15 считывания узла открывается группа элементов И 8, разрешая вьщачу искомой переменной Ujj с выхода сумматора 7 результата на выход 12 узла.

Формула изобретения

Вычислительное устройство для решения дифференциальных уравнений, со- держащее блок памяти, сдвигатель, регистр, сумматор результата, группу элементов И, блок синхронизации, вход пуска устройства подключен к входу запуска блока синхронизации, первый выход которого подключен к синхронизирующему входу регистра, а второй выход - к входу считывания блока памяти, вход задания точности устройства подключен к первым входам элементов И группы, выходы которых подключены к выходам результата устройства, о т - л и ч а ю щ е е с я тем, что, с цел ью увеличения быстродействия, в

него введены накапливающий сумматор, узел приоритета, дешифратор и коммутатор, первый выход блока синхронизации подключен к стробирующему входу сумматора результата, третий выход блока синхронизации подключен к синхронизирующему входу накапливающего сумматора, выходы с четвертого по шестой блока синхронизации подключены к управляющим входам коммутатора и к адресным входам блока памяти, выходы блока памяти подключены к информационным входам сдвигателя, выходы которого подключены к входам модуля слагаемого накапливающего сумматора, выходы модуля результата которого подключены к входам узла приоритета, выходы которого поразрядно подключены к информационным входам регистра, выход знакового разряда сумматора подключен к информационному входу знакового разряда регистра, выходы которого поразрядно подключены к входам дешифратора, к первому информационному входу коммутатора и к выходам приращений устройства, выход дешифратора подключен к первому входу сумматора результата, выходы которого подключены к вторым входам элементов И группы, вьгход знакового разряда регистра подключен к второму входу сумматора результата, информационные J: входы с второго по пятый коммутатора подключены к входам приращений устройства, первый выход коммутатора подключен к тактовому входу сдвигателя, второй выход коммутатора подключен к входу знакового разряда накапливающего сумматора.

ТЗ

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

Изобретение относится к области вычислительной техники и предназначено для решения диАференциальных нелинейных и квазилинейных уравнений в частных производных. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство содержит блоки памяти, сдвигатель, регистр, сумматор результата, блок синхронизации, группу элементов И, накапливающий сумматор, схему приоритета, дешифратор и коммутатор. Это обеспечивает совмещение во времени итерационного процесса поиска решения и формирования очередного разряда приращения переменной, при этом каждая итерация в устройстве выполняется за шесть тактов. 2 ил. i (Л С N9 00 4

Редактор И.Рыбченко

Составитель В.Смирнов

Техред И.Ходанич Корректор А.Обручар

Заказ 6669/44 . Тиралс 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д..4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, {

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных | 1975 |

|

SU546891A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения двумерных задач математической физики | 1975 |

|

SU610116A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-04-24—Подача