(Я

Од

vi

а

N9

4i)k

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода во временной интервал | 1990 |

|

SU1714811A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Преобразователь двоичного кода во временной интервал | 1987 |

|

SU1453597A1 |

| Устройство коррекции шкалы времени | 1988 |

|

SU1525932A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Преобразователь двоичного кода во временной интервал | 1990 |

|

SU1785077A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Формирователь временного интервала | 1988 |

|

SU1580540A2 |

| Устройство для преобразования двоичного кода во временной интервал | 1986 |

|

SU1363475A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

Изобретение относится к вычис- (ли-Рвльной технике, а именно к устройствам преобразования информации,. и может быть использовано в вычислительно-управляющих системах автоматики. Изобретение позволяет жестко привязать начало и конец формируемого временного интервала к срезу тактовых импульсов, чем обеспечивается повьшение точности преобразования. Преобразователь двоичного кода во временной интервал содержит два триггера 1 и 2, генератор 3 импульсов, блок 4 регистров, два счетчика 5 и 8 импульсову элемент И 6, элемент И-НЕ 7, два формирователя 9 и 10 импульсов и формирователь I1 кодовых последовательностей. 2 ил.

Фиг

Изобретение относится к вычислиельной технике, а именно к устройстам преобразования информации, и ожет быть использовано в вычисли- ельно-управляющих системах автомаики.

Целью изобретения является повышеие точности преобразования.

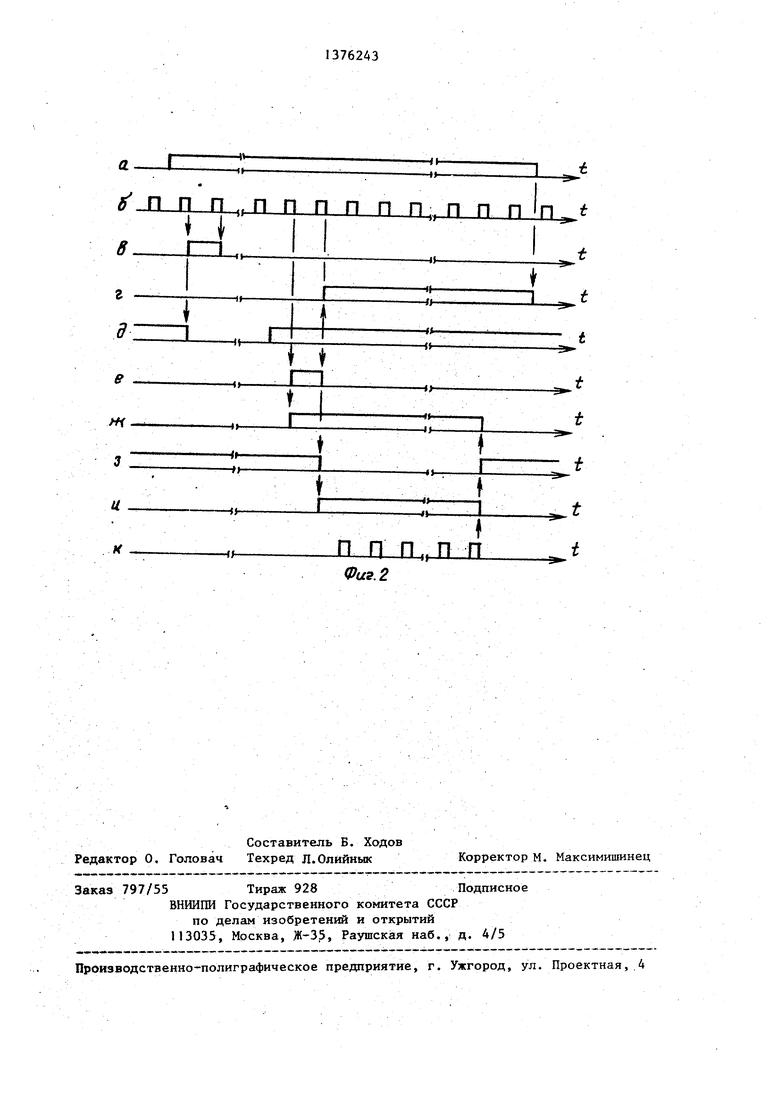

На фиг. I приведена структурная tO схема преобразователя двоичного кода во временной интервал; на фиг. 2 - ременные диаграммы, поясняющие раоту преобразователя.

Преобразователь двоичного кода 15 во временной интервал содержит первый 1 и второй 2 триггеры, генератор 3 импульсов, блок 4 регистров, первый счетчик 5 импульсов, элемент И 6, элемент И-НЕ 7, второй счетчик 8 им- 20 пульсов, первый 9 и второй 10 формирователи импульсов и формирователь I1 кодовых последовательностей. Преобразователь (фиг. 1) имеет управляющий 12 и информационный 13 входы и 25 выход- 14.

На фиг. 2 обозначено: а - сигнал на входе 12 преобразователя; б - сигнал на выходе генератора 3; в - сигнал на выходе формирователя 10; г - 30 сигнал на выходе триггера 2; д - сигнал на выходе счетчика 8; е - сигнал на выходе формирователя 9; ж - сигнал на выходе счетчика 5; з - сигнал на выходе элемента И-НЕ 7; и - с сигнал на выходе триггера 1 и выходе 14 преобразователя; к - сигнал на выходе элемента И 6.

Преобразователь двиочного кода во временной интервал работает еле- Q дующим образом.

На вход 12 опроса подается импульс, который поступает на вход установки триггера 2, разрешая измене -: ние состояния последнего-под воздёй- д ствием сигналов на входе синхронизации, и на вход формирователя 10.

На другой вход формирователя 10 поступают импульсы с выхода генератора 3. На выходе формирователя 10 мируется импульс, фронт которого совпадает со срезом первого импульса генератора 3, а срез - со срезом второго импульса генератора 3.

Импульс с выхода формирователя 10 подается на вход установки счетчика 8. При этом последний сбрасывается и на его выходе появляется логический О, Этот сигнал подается на

55

вход формирователя 9, подготавливая его к работе.

На вход 13 подается последовательный импульсный двоичный сод по двум линиям связи в виде прямого и инг версного кодов. Единице кода соответствует наличие импульса на линии связи прямого кода и отсутствие импульса на линии связи инверсного кода, а нулю кода - отсутствие импульса на линии связи прямого кода и наличие импульса на лини связи инверсного кода.

В формирователе 11 на первом выходе формируется серия импульсов, представляющих собой суммарную после- довательность импульсов прямого и. инверсного кодов, поступающих по двум линиям связи на вход 13, а на втором выходе формируется прямой код, причем длительность его импульсов расширена до периода повторения импульсов, сформированных на первом выходе формирователя М. Реализовать такой алгоритм формирования кодовых последовательностей можно, например, с помощью параллельно соединенных RS-триггера и элемента ИЛИ, к выходу которого подключен элемент задержки. Расширение длительности импульсов прямого кбда и задержки импульсов на первом выходе обеспечивает надежную запись кода в блок 4.

Счетчик 8 подсчитывает число импульсов на первом выходе формирователя 11, т.е. число пришедших разря-. дов кода. Как только на блок 4 поступает последний-разряд кода, на выходе счетчика 8 появляется логическая 1, которая несет информацию о том, что все разряды кода записались в блок 4. Этот сигнал подается на вход формирователя 9, на выходе которого, аналогично формирователю 10, формируется импульс причем фронт и срез этого импульса привязаны к срезу импульсов генератора 3.

Импульс с выхода формирователя 9 подается на вход записи счетчика 5, при этом параллельный код, сформированный на выходах блока 4, записывается в счетчик 5, на выходе которого появляется логическая, которая подается на R-вкод триггера 1 и на вход элемента И-НЕ 7.

Одновременно импульс с выхода формирователя 9 переворачивает по срезу триггер 2 и логическая 1 с

его выхода подается на вход элемент И-НЕ 7. Логический О с выхода элемента И-НЕ 7 подается на S-вход тригера 1 и переворачивает его, форми- руя фронт выходного временного интервала на выходе 14. Поскольку изменение состояния триггера 1 происходит по срезу импульса формирователя 9, который совпадает со срезом импульса генератора 3, фронт формируемого временного интервала оказывается жестко привязан к срезу им- пульса генератора 3.

Логическая 1 с выхода триггера I подается на вход элемента И 6, .рарешая прохождение импульсов генератора 3 через элементы И 6 ни вход вьгчитания счетчика 5, Код, записанный в счетчике 5, начинает считы- ваться. Как только код считается, на выходе реверсивного счетчика 5 появляется логический О, причем появление этого сигнала происходит по срезу импульса генератора 3, вы зывающего обнуление счетчика 5.

Логический О с выхода реверсивного счетчика 5 подается на R- Ъход триггера 1 и на вход элемента И-НЕ 7, На выходе последнего появ- ляется логическая 1. Триггер 1 переворачивается, и формируется срез выходного временного интервала на выходе 14. Поскольку изменение состояния триггера 1 привязано к срезу импульса генератора 3, вызывающего обнуление счетчика 5, то срез форми руемого временного интервала оказывается жестко привязанным к срезу импульса генератора 3.

. Таким образом, на выходе триггера 1, соединенном с выходом 14, формируется импульс, длительность которого определяется введенным кодом.

Логический О с выхода триггера 1 подается на элемент И 6, запрещая прохождение импульсов генератора 3 через элемент И 6 на вход вычитания

счетчика 5,

, ю

15 20 5

5

0

5

0

Формула изобретения Преобразователь двоичного кода во временной интервал, содержащий первый и второй триггеры, генератор импульсов, блок регистров, выходы которого соединены с информационными входами первого счетчика импульсов, выход которого соединен с первым входом первого триггера, выход которого , соединен с первым входом элемента И, отличающийся тем, что, с целью повышения точности преобразования, в преобразователь введены элементы И-НЕ, второй счетчик импульсов, формирователи импульсов, формироват тель кодовых последовательностей, первый выход которого соединен с пер- ,Bbw управлякнцим входом блока регистров и с первым входом второго счетчика импульсов, выход которого соединен с первым входом первого формирователя импульсов, выход которого соег динен с первьм управляющим входом первого счетчика импульсов и с первым входом второго триггера, выход генератора импульсов соединен с первым входом второго формирователя импульсов и с вторыми входами первого формирователя импульсов и элемента И, выход которого соединен с вторым управляющим входом первого счетчика импульсов, выход второго триггера соединен с первым входом элемента И-НЕ, выход которого соединен с вторым входом первого триггера, выход второго формирователя импульсов соединен с вторым входом второго счетчика импульсов, второй вход элемента И-НЕ подключен к выходу первого счетчика импульсов, второй выход форми- вателя кодовых последовательностей соединен с вторым входом блока регистров, вторые входы второго формирователя импульсов и второго триггера объединены и являются управляющим входом преобразователя, вход формирователя кодовых последовательностей и выход первого триггера являются соответственно информационным входом и выходом преобразователя.

Фиг. 2

| Преобразователь цифровой код-временнойиНТЕРВАл | 1974 |

|

SU843218A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Программируемый преобразователь код-временной интервал | 1983 |

|

SU1088114A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-23—Публикация

1986-08-11—Подача