00 4

L

00

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических схем | 1986 |

|

SU1365087A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для контроля логических блоков | 1990 |

|

SU1805471A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНО-ДИНАМИЧЕСКОГО КОНТРОЛЯ ЛОгаЧЕСКИХ СХЕМ, содержащее генератор тактов, счетчик и сигнатурный анализатор, причем выход генератора тактов соединен с входом синхронизации сигнатурного анализатора и со счетным входом счетчика, отличающееся тем, что, с целью повышения полноты контроля, в него введены элемент задержки, формирователь импульса, первый и второй регистры, причем выход генератора тактов соединен через элемент задержки с входом формирователя импульса, выход которого соединен с входами разрешения записи первого и второго регистров, выходы счетчика соединены соответственно с информационными входами первого регистра, выходы которого соединены с соо.тветствунлдими входами контролируемой логической схемы, выходы контролируемой логической схемы соединены с ИН формационными входами второго регистi Ut ра, выходы которого соединены с информационными входами сигнатурного анализатора, старт-стопный вход сигнатурного анализатора соединен с выходом старшего разряда счетчика. .

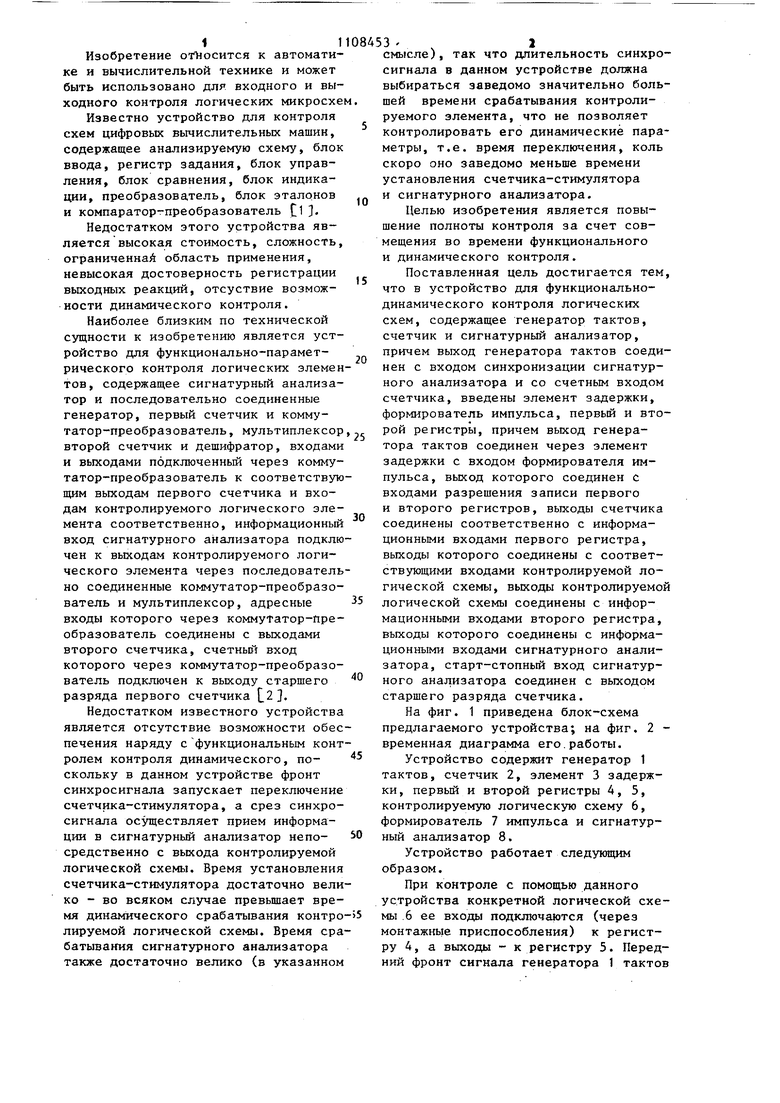

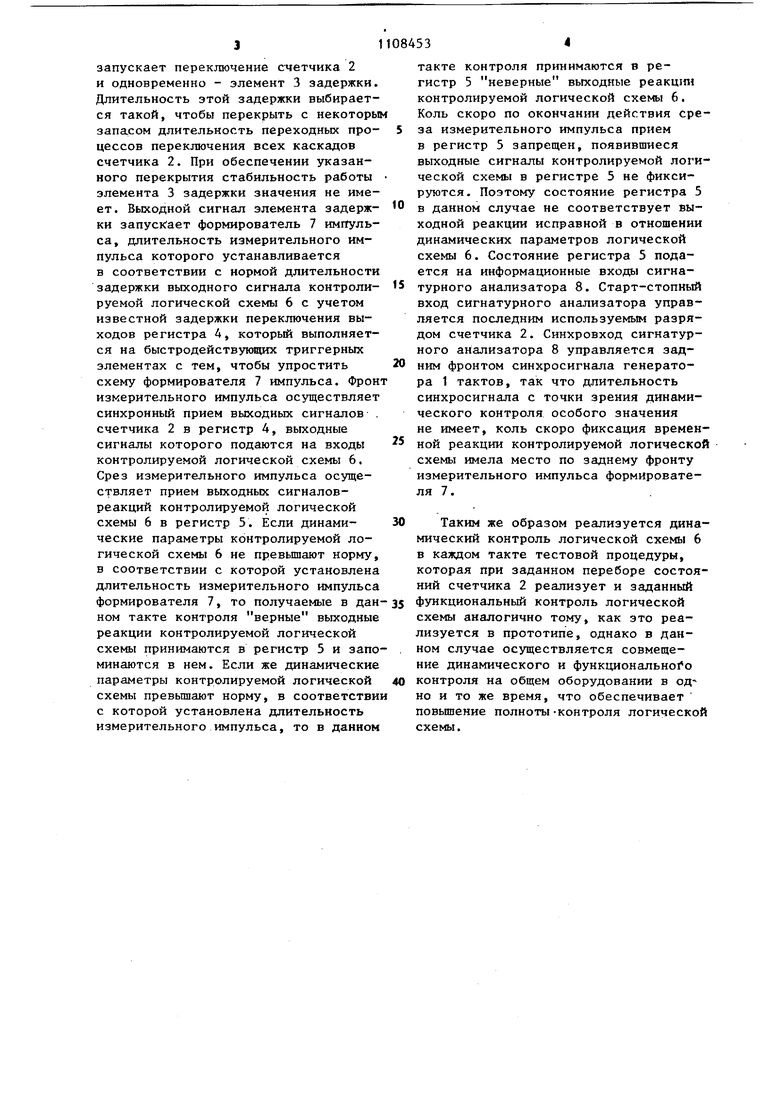

-i 11 Изобретение относится к автоматике и вычислительной технике и может быть использовано для входного и выходного контроля логических микросхе Известно устройство для контроля схем цифровых вычислительных машин, содержащее анализируемую схему, блок ввода, регистр задания, блок управления, блок сравнения, блок индикации, преобразователь, блок эталонов и компаратор-преобразователь Cl. Недостатком этого устройства является высокая стоимость, сложность, ограниченна область применения, невысокая достоверность регистрации выходных реакций, отсуствие возможности динамического контроля. Наиболее близким по технической сущности к изобретению является устройство для функционально-параметрического контроля логических элемен тов, содержащее сигнатурный анализатор и последовательно соединенные генератор, первый счетчик и коммутатор-преобразователь , мультиплексор второй счетчик и дешифратор, входами и выходами подключенный через коммутатор-преобразователь к соответствую щим выходам первого счетчика и входам контролируемого логического элемента соответственно, информационный вход сигнатурного анализатора подклю чен к выходам контролируемого логического элемента через последователь но соединенные коммутатор-преобразователь и мультиплексор, адресные входы которого через коммутатор-преобразователь соединены с выходами второго счетчика, счетньо вход которого через коммутатор-преобразователь подключен к выходу старшего разряда первого счетчика ,2, Недостатком известного устройства является отсутствие возможности обес печения наряду сфункциональным конт ролем контроля динамического, поскольку в данном устройстве фронт синхросигнала запускает переключение счетчика-стимулятора, а срез синхросигнала осуществляет прием информации в сигнатурный анализатор непосредственно с выхода контролируемой логической схемы. Время установления счетчика-стимулятора достаточно вели ко - во всяком случае превьшает время динамического срабатывания контро лируемой логической схемы. Время сра батывания сигнатурного анализатора также достаточно велико (в указанном 3 смысле), так что длительность синхросигнала в данном устройстве должна выбираться заведомо значительно большей времени срабатывания контролируемого элемента, что не позволяет контролировать его динамические параметры, т.е. время переключения, коль скоро оно заведомо меньше времени установления счетчика-стимулятора и сигнатурного анализатора. Целью изобретения является повышение полноты контроля за счет совмещения во времени функционального и динамического контроля. Поставленная цель достигается тем, что в устройство для функциональнодинамического контроля логических схем, содержащее генератор тактов, счетчик и сигнатурный анализатор, причем выход генератора тактов соединен с входом синхронизации сигнатурного анализатора и со счетньм входом счетчика, введены элемент задержки, формирователь импульса, первый и второй регистры, причем выход генератора тактов соединен через элемент задержки с входом формирователя импульса, выход которого соединен с входами разрешения записи первого и второго регистров, выходы счетчика соединены соответственно с информационными входами первого регистра, выходы которого соединены с соответствующими входами контролируемой логической схемы, выходы контролируемой логической схемы соединены с информационными входами второго регистра, выходы которого соединены с информационными входами сигнатурного анализатора, старт-стопный вход сигнатурного анализатора соединен с выходом старшего разряда счетчика. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 временная диаграмма его.работы. Устройство содержит генератор 1 тактов, счетчик 2, элемент 3 задержки, первый и второй регистры 4, 5, контролируемую логическую схему 6, формирователь 7 импульса и сигнатурный анализатор 8. Устройство работает следующим образом. При контроле с помощью данного устройства конкретной логической схемы 6 ее входы подключаются (через монтажные приспособления) к регистру 4, а выходы - к регистру 5. Передний фронт сигнала генератора 1 тактов

запускает переключение счетчика 2 и одновременно - элемент 3 задержки. Длительность этой задержки выбирается такой, чтобы перекрыть с некоторы запа,сом длительность переходных процессов переключения всех каскадов счетчика 2. При обеспечении указанного перекрытия стабильность работы элемента 3 задержки значения не имеет. Выходной сигнал элемента задержки запускает формирователь 7 импульса, длительность измерительного импульса которого устанавливается в соответствии с нормой длительности задержки выходного сигнала контролируемой логической схемы 6 с учетом известной задержки переключения выходов регистра А, который выполняется на быстродействующих триггерных элементах с тем, чтобы упростить схему формирователя 7 импульса. Фрон измерительного импульса осуществляет синхронный прием выходных сигналов . счетчика 2 в регистр 4, выходные сигналы которого подаются на входы контролируемой логической схемы 6. Срез измерительного импульса осуществляет прием выходных сигналовреакций контролируемой логической схемы 6 в регистр 5. Если динамические параметры контролируемой логической схемы 6 не превышают норму, в соответствии с которой установлена длительность измерительного импульса формирователя 7, то получаемые в данном такте контроля верные выходные реакции контролируемой логической схемы принимаются в регистр 5 и запоминаются в нем. Если же динамические параметры контролируемой логической схемы превышают норму, в соответствии с которой установлена длительность измерительного импульса, то в данном

такте контроля принимаются в регистр 5 неверные выходные реакшш контролируемой логической схемы 6. Коль скоро по окончании действия среза измерительного импульса прием в регистр 5 запрещен, появившиеся выходные сигналы контролируемой логической схемы в регистре 5 не фиксируются. Поэтому состояние регистра 5 в данном случае не соответствует выходной реакции исправной в отношении динамических параметров логической схемы 6. Состояние регистра 5 подается на информационные входы сигнатурного анализатора 8. Старт-стопный вход сигнатурного анализатора управляется последним используемым разрядом счетчика 2. Синхровход сигнатурного анализатора 8 управляется задним фронтом синхросигнала генератора 1 тактов, так что длительность синхросигнала с точки зрения динамического контроля особого значения не имеет, коль скоро фиксация временной реакции контролируемой логической схемы имела место по заднему фронту измерительного импульса формирователя 7.

Таким же образом реализуется динамический контроль логической схемы 6 в каждом такте тестовой процедуры, которая при заданном переборе состояний счетчика 2 реализует и заданный Функциональный контроль логической схемы аналогично тому, как это реализуется в прототипе, однако в данном случае осуществляется совмещение динамического и фyнкциoнaльнofo контроля на общем оборудовании в одно и то же время, что обеспечивает повышение полноты -контроля логической схемы. ГлавныйI синхросигнал 1 - Зпембитэаоержки j

//epSK mt eHueуv/

ci emvuKa 2 --,--ЛA

8 pe :irff if cocmo/iHu/i cvemtiuKOZ

opMupoS ir flb

7 ,

/fepeifflwi CHuc.-у ,.KOHfr flupyewu

исправной кон-X oiutj. g

tnpo/fupyeMoi)

/roiui. схемы I

. HfucnpaoHou I/JI pi/ем ff cuiHufrtyp S ано/tujfimotp 8 cocmo Hu регистра 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для КОНТРОЛЯ СХЕМ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 0 |

|

SU378852A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1983-04-01—Подача