Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1683016A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Устройство для умножения | 1985 |

|

SU1291975A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Накапливающий перемножитель | 1981 |

|

SU987618A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

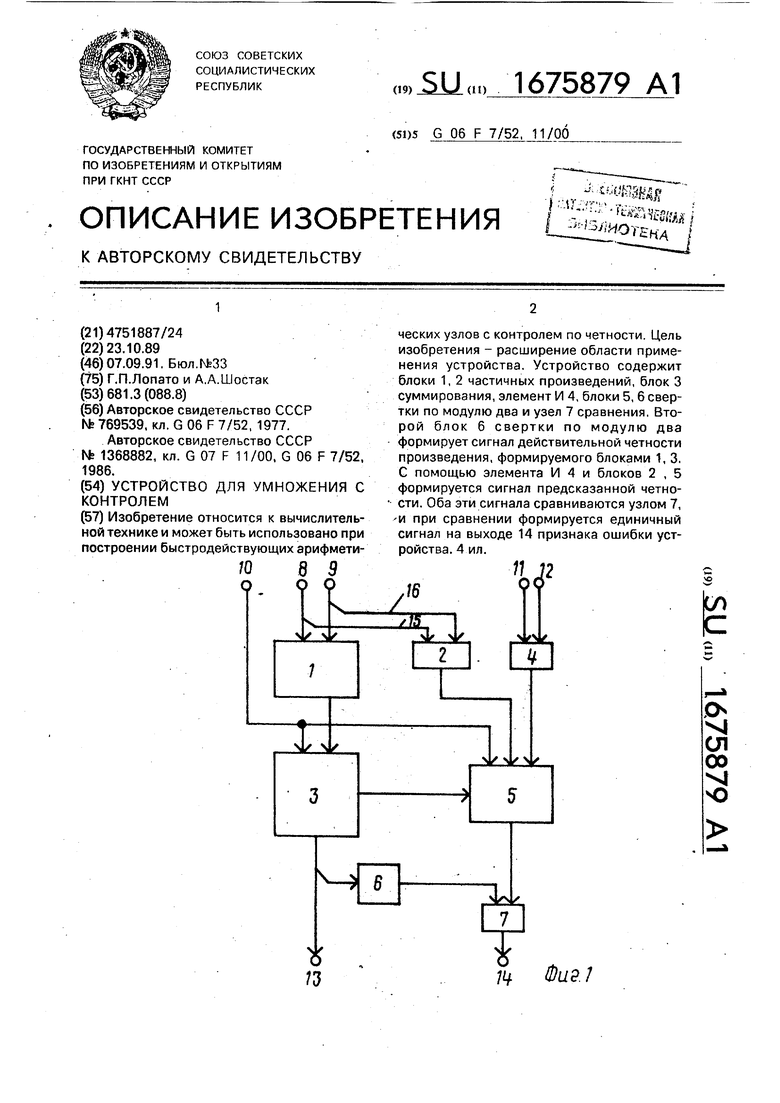

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих арифметических узлов с контролем по четности. Цель изобретения - расширение области применения устройства. Устройство содержит блоки 1, 2 частичных произведений, блок 3 суммирования, элемент И 4, блоки 5, 6 свертки по модулю два и узел 7 сравнения. Второй блок 6 свертки по модулю два формирует сигнал действительной четности произведения, формируемого блоками 1, 3. С помощью элемента И 4 и блоков 2 , 5 формируется сигнал предсказанной четности. Оба эти сигнала сравниваются узлом 7, -и при сравнении формируется единичный сигнал на выходе 14 признака ошибки устройства. 4 ил.

,с VJ

ел

00

1 ю

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих арифметических узлов с контролем по четности

Целью изобретения является расширение области применения устройства.

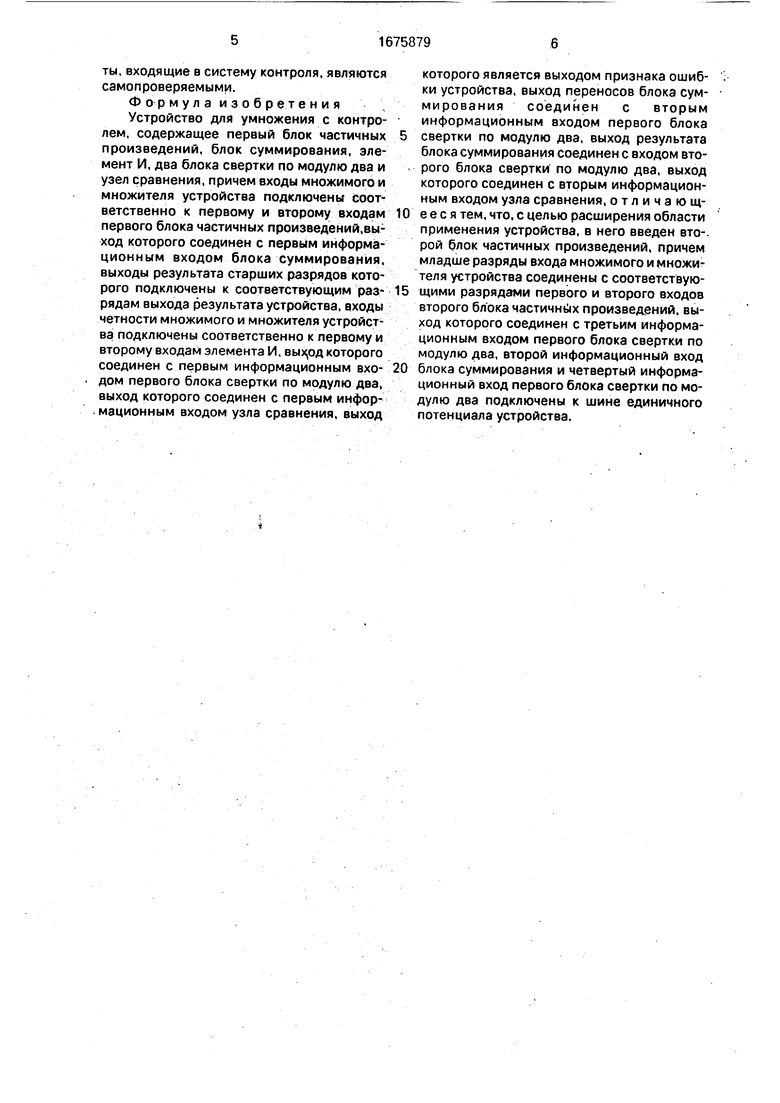

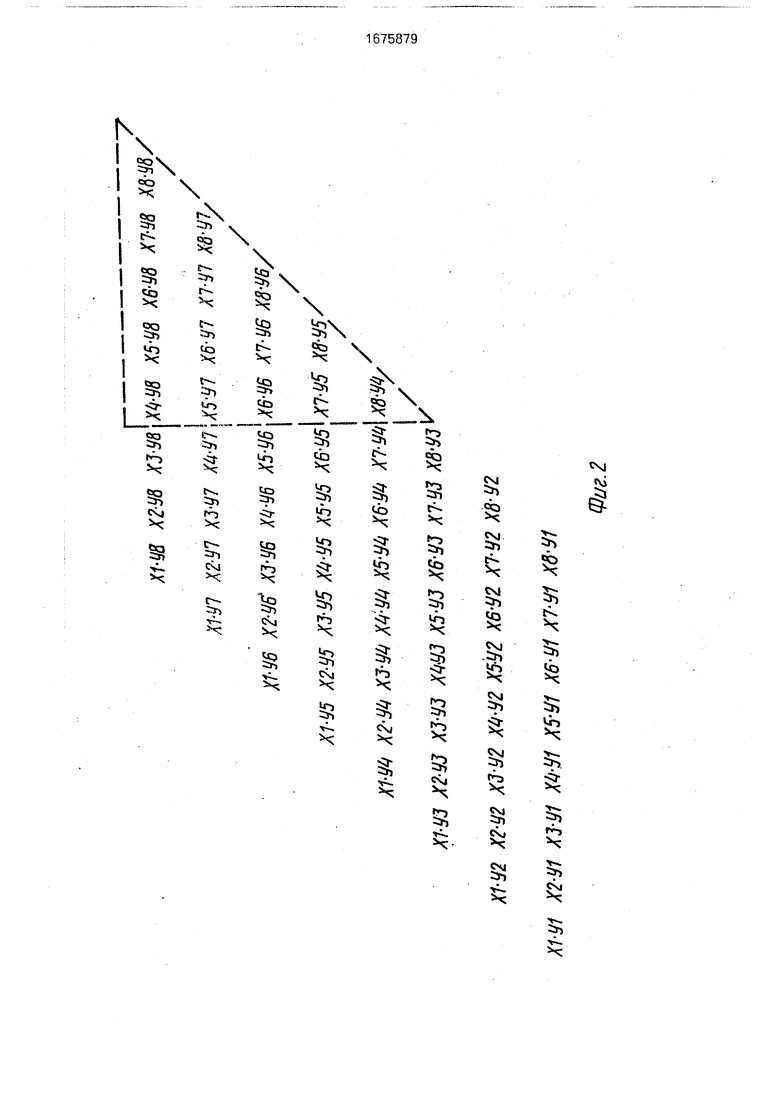

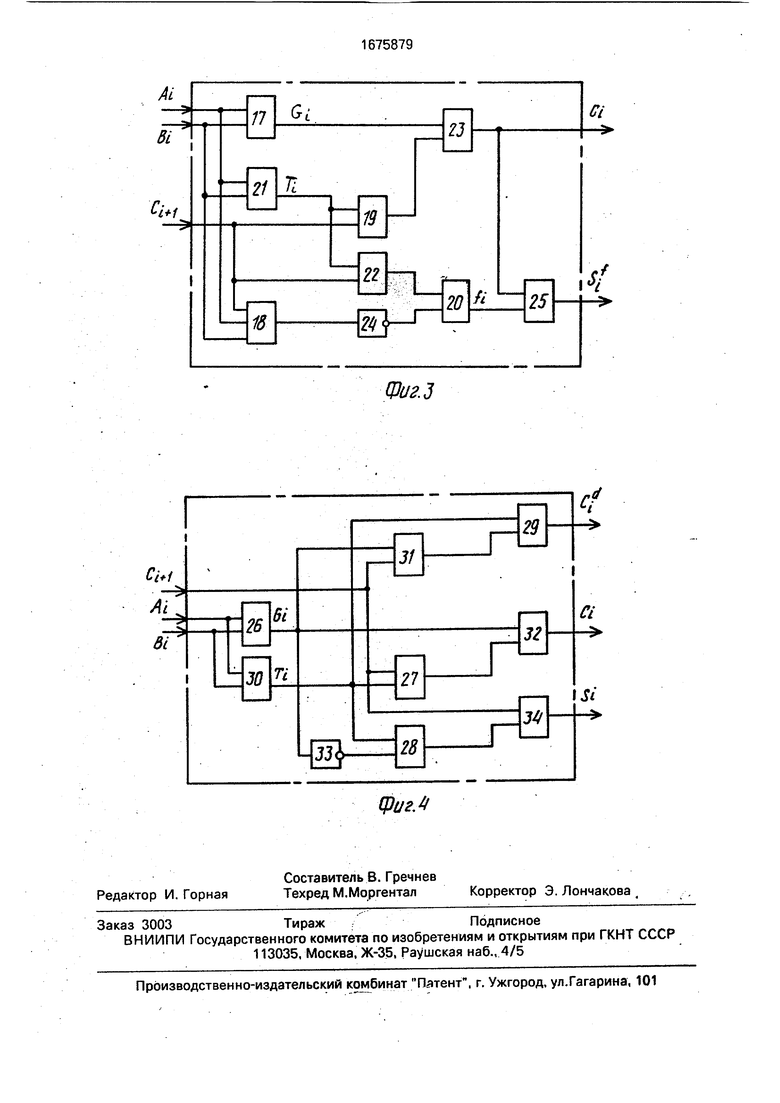

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - массив разрядных произведений для восьмиразрядных сомножителей; на фиг.З и 4 - функциональные схемы одноразрядных двоичных сумматоров с функциональной зависимостью суммы от переноса и с дублирующим переносом соответственно.

Устройство для умножения (фиг.1) содержит первый 1 и второй 2 блоки частичных произведений, блок 3 суммирования, элемент И 4, блоки 5 и 6 свертки по модулю два, узел 7 сравнения, входы множимого 8 и множителя 9 устройства, шину 10 единичного потенциала устройства, входы четности множимого 11 и множителя 12 устройства, выходы результата 13 признака ошибки 14 устройства, младшие разряды 15 и 16 входов множимого 8 и множителя 9 устройства соответственно

Сумматор (фиг.З) содержит элементы И 17-20, И Л VI 21 -23, НЕ 24 и узел 25 сложения по модулю два.

Сумматор, изображенный на фиг.4, содержит элементы И 26 - 29, ИЛИ 30 - 32, НЕ 33 и узел 34 сложения по модулю два.

В блоках 1 и 2 формируются п п-разряд- ных частичных произведений (п-разряд- ность сомножителей). На фиг.2 показан массив разрядных произведений, формируемых блоками 1 и 2. Обведенные на фиг.2- пунктиром разрядные произведения формируются в блоке 2, остальные - в блоке 1. В блоке 3 осуществляется суммирование с учетом весовых позиций частичных произведений, сформированных в блоке 1, а также единицы округления, поступающей с шины 10 единичного потенциала устройства. Блок 3 может быть построен на многоразрядных или одноразрядных двоичных сумматорах (ОДС) любым известным способом. Для повышения достоверности форми- руемых в устройстве результатов целесообразно использовать ОДС с функциональной зависимостью суммы от переноса или ОДС с дублирующим переносом (фиг.З и 4).

Если блок 3 суммирования построен на сумматорах с функциональной зависимостью суммы от переноса, то на его выход переносов подаются значения переносов, формируемых в блоке 3, если блок 3 построен на сумматорах с дублирующим переносом, то на его выход переносов подаются значения дублирующих переносов.

Элемент И 4 формирует логическое произведение четностей множимого и множи- теля.

В первом блоке 5 свертки по модулю два формируется предсказываемая четность произведения в соответствии с выражением

Рп РхРуФРсФРотФ1,

где Рх, Ру - соответственно четности множимого и множителя;

PC - четность формируемых в блоке 3 переносов (или дублирующих переносов, если блок 3 построен на сумматорах с дублирующим переносом);

Рот - четность отбрасываемых разрядов частичных произведений.

В блоке 6 свертки по модулю два формируется фактическая четность произведения. На вход блока 6 подаются все разряды суммы блока 3, а на выход 13 результата устройства поступают тол ько старшие п разрядов этой суммы.

На узле 7 происходит сравнение фактической и предсказываемой четностей произведения. При их несовпадении формируется признак ошибки устройства, который поступает на выход 14 устройства. Устройство работает следующим образом.

После подачи на входы 8 и 9 устройства значений множимого и множителя в блоке 1 формируются частичные произведения (некоторая их часть формируется без младших

разрядов), которые затем поступают в блок 3 суммирования через его первый вход. На второй вход блока 3 суммирования с шины 10 единичного потенциала устройства поступает сигнал логической единицы, который участвует в округлении произведения. В блоке 3 осуществляется суммирование частичных произведений и единицы округления с учетом занимаемых ими весовых позиций. Значения старших разрядов суммы, полученной в блоке 3, поступают на выход 13 результата устройства. Значения всех разрядов полученной в блоке 3 суммы подаются на вход второго блока 6 свертки по модулю два, на выходе которого формируется значение фактической четности произведения. Одновременно с работой блоков 1, 3 и 6 работают блоки 2 и 5 и элемент И 4, с помощью которых формируется значение предсказываемой четности произведения,

которое затем сравнивается узлом 7 со значением фактической четности. В результате этого сравнения на выходе 14 устройства вырабатывается или не вырабатывается сигнал ошибки работы устройства. Все элементы, входящие в систему контроля, являются самопроверяемыми.

Формула изобретения Устройство для умножения с контролем, содержащее первый блок частичных произведений, блок суммирования, элемент И. два блока свертки по модулю два и узел сравнения, причем входы множимого и множителя устройства подключены соответственно к первому и второму входам первого блока частичных произведений,выход которого соединен с первым информационным входом блока суммирования, выходы результата старших разрядов которого подключены к соответствующим разрядам выхода результата устройства, входы четности множимого и множителя устройства подключены соответственно к первому и второму входам элемента И, выход которого соединен с первым информационным входом первого блока свертки по модулю два, выход которого соединен с первым информационным входом узла сравнения, выход

которого является выходом признака ошибки устройства, выход переносов блока сум- мирования соединен с вторым информационным входом первого блока

свертки по модулю два, выход результата блока суммирования соединен с входом второго блока свертки по модулю два, выход которого соединен с вторым информационным входом узла сравнения, отличаю ще е с я тем, что, с целью расширения области применения устройства, в него введен второй блок частичных произведений, причем младше разряды входа множимого и множителя устройства соединены с соответствующими разрядами первого и второго входов второго блока частичных произведений, выход которого соединен с третьим информационным входом первого блока свертки по модулю два, второй информационный вход

блока суммирования и четвертый информационный вход первого блока свертки по модулю два подключены к шине единичного потенциала устройства.

Ч1

I

Ai

Gc

Bi

71

-t+1

16

23

а

ft

tf

V

}-Г-Ц

CPU2.3

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1986 |

|

SU1368882A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1991-09-07—Публикация

1989-10-23—Подача