со

О)

СП

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах коммутации и передачи данных.

Целью изобретения является упрощение устройства за счет уменьшения числа транзисторов в разрядной ячейке распределителя путем вьтолнення триггера каждой ячейки на МДП-транзисто- рах и непосредственного соединения стоков МДП-транзисторов разноименных плеч триггеров соседних ячеек.

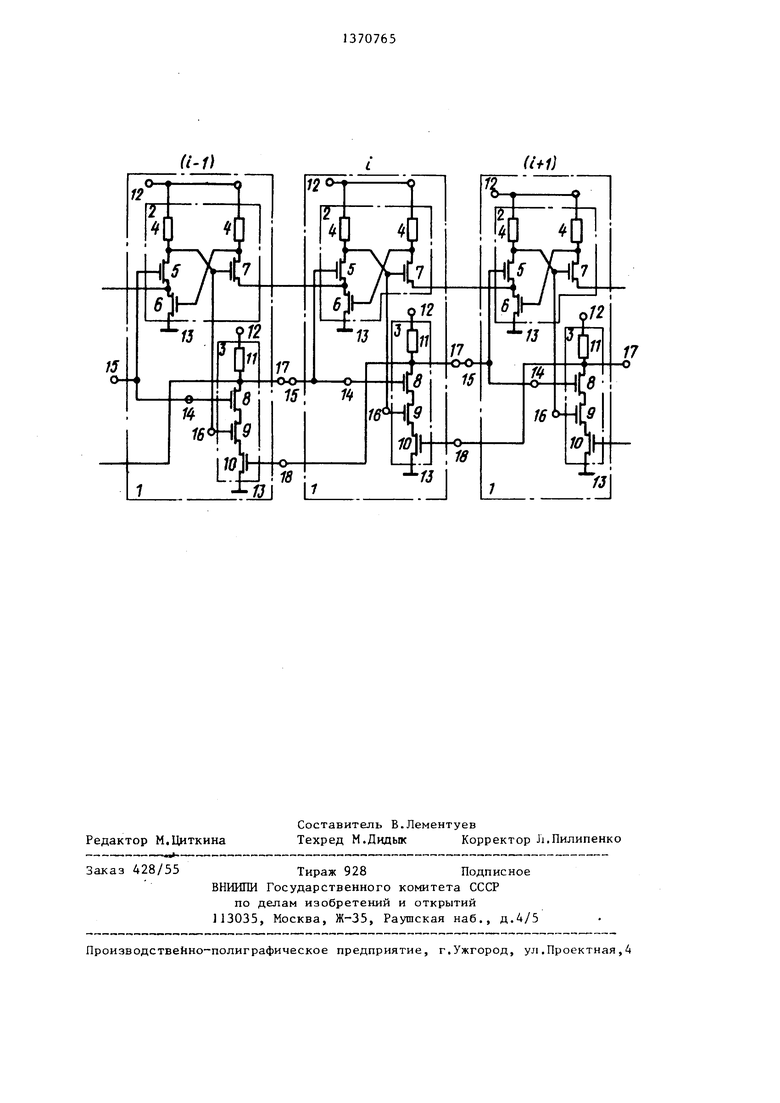

На чертеже приведена принципиальная схема асинхронного распределителя .

Устройство содержит ячейки 1 в каждом разряде, каждая из которых состоит из триггера 2 и элемента И-НЕЗ Триггер 2 содеряит два нагрузочных элемента 4 и три МДП-транзис- тора 5-7. Элемент И-НЕ 3 содержит три МДП-транзистора 8-10 и нагрузочный элемент 1J.

МДП-транзистора7 триггера 2 i-й ячейки 1 подключен к точке последовательного соединения первого 5 и второго 6 МДП- транзисторов триггера 2 последующей (i + 1)-й ячейки 1 .

Устройство работает следующим образом.

Установка ( i-1 ) производится подачей на ее шину 15 установки Нулевого логического уровня (низкого потенциала). При этом в триггер 2 этой ячейки записывается 1, т.е. МДП-транзисторы 5 и 8 закрываются, после чего открывается МДП-тран- зистор 7, и на затворе МДП-транзистора 6 появляется низкий потенциал, закрывающий этот транзистор, в результате чего на выходной шине 17

(1-)-й ячейки сохраняется высокий потенциал до тех пор, пока низкий потенциал сохраняется на ее шине установки 15.

После того как на шине J 5 уста

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный асинхронный регистр на МДП-транзисторах | 1988 |

|

SU1615807A1 |

| Асинхронный распределитель | 1987 |

|

SU1458968A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Регистр сдвига | 1987 |

|

SU1476535A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Статическая ячейка памяти на мдп- ТРАНзиСТОРАХ | 1979 |

|

SU799004A1 |

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах коммутации и передачи данных. Цель изобретения - упрощение устройства. Асинхронный распределитель импульсов (АРИ) содержит ячейки 1 в каждом разряде, каждая из которых состоит из триггера 2 и элемента И-НЕ 3. Триггер 2 содержит нагрузочные элементы (НЭ) 4 и МДП-тран- зисторы 5-7. Элемент И-НЕ 3 содержит МДП-транзисторы 8-10 и НЭ 11. АРИ содержит также шину 12 питания, общую шину 13, шину 15 установки, выходную щину 17. АРИ имеет простую электрическую схему. 1 ил.

Нагрузочные элементы 4 триггера 2 25 новки (1-1)-й ячейки J появится вывключены между шиной 12 питания и стоками соответственно первого 5 и третьего 7 МДП-транзисторов триггера 2.

Нагрузочные элементы 4 и 11 могут быть выполнены также в виде J1-транзисторов. Триггеры 2 и элементы И-НЕ 3 включены между шиной 12 питания и общей шиной 13. Первый 5 и второй 6 МДП-транзисторы триггера 2 соединены последовательно, причем исток второго МДП-транзистора 6 подключен к общей шине 13.

Затвор первого МДП-транзистора 5, являюш11Йся первым входом триггера, соединен с первым входом 14 элемента И-НЕ 3 и подключен к шине 15 установки соответствующей ячейки 1.

Затвор второго МДП-транзистора 6 триггера 2, являющейся вторым входом триггера 2, подключен к стоку третьего МДП-транзистора 7. Сток первого МДП-транзистора 5, являющийся первым выходом триггера 2, соединен с затвором третьего МДП-транзистора 7, являющимся третьим входом триггера 2, и подключен к второму входу 16 элемента И-НЕ 3. Выходная шина 17 i-й ячейки, являющаяся выходом элемента И-НЕ 3 этой ячейки, подключена к шине 1 5 установки последующей (i+1 ) ячейки 1 и к третьему входу 18 элемента И-НЕ 3 предыдущей (i-1 ) ячейки 1.Исток третьего

сокий потенциал, открьшающий МДП- транзистор 8, низкий потенциал установится на выходной шине J7 этой ячейки 1 и поступит на шину установ- ки 15 последующей i-й ячейки 1, в результате чего в триггер 2 этой ячейки также будет записана 1.

Далее произойдет установка (.1 + J )-й ячейки 1, процесс которой аналогичен рассмотренному. Существенно, что до тех пор, пока в триггере 2 1-й ячей

1

записана

Ч

в такой же триг

гер 2 (i-) ячейки 1 не может быть записана 1. Действительно, при этом на истоке МДП-транзистора 7 имеется высокий потенциал, который поддерживает высокий потенциал на стоке того же МДП-транзистора 6 триггера 2. Поэтому подача на шине J5 установки (i-l)-й ячейки 1 низкого

потенциала до того, как i-я ячейка перейдет в исходное состояние (т.е. в триггер 2 этой ячейки будет записан о) , вызовет лишь появление вы-

сокого потенциала на стоке МДП-транзистора 8.

Элементы И-НЕ 3 соседних ячеек J образуют триггер, поэтому выходные шины 17 этих элементов не могут одновременно обладать низким потенциалом, т.е. низкий потенциал.на выходной шине 17 i-й ячейки 1 поддерживает высокий потенциал на выходной щи

не 17 (i-l)-ft ячейки 1. Поэтому подача на шине 15 установки сигнала установки (i-l)-fl ячейки 1 не вызывает появления низкого потенциала на выходной шине 17 этой ячейки и изменения сигнала на выходной шине 17 (i-1)-й ячейки.

Таким образом, повторная установка (1-1)-й ячейки 1 осуществляется лишь после того, как i-я ячейка 1 окажется в исходном состоянии.

Следовательно, при повторной инициации работы асинхронного распределителя до того как завершится предыдущий цикл его работы, последующая волна установок ячеек не достигнет предыдущей, так как между ними всегда будет находиться по крайней мере одна ячейка в исходном состоянии,что обеспечивает правильное функционирование распределителя в мультимикро- программном режиме.

В предложенном асинхронном распределителе каждая ячейка требует для своей реализации девять МДП-транзисторов, тогда как в рапределителе-про тотипе - десять МДП-транзисторов. Таким образом, предложенное техническое решение дает экономию оборудования на 10%, чем достигается поставленная цель.

Формула изобретения

Асинхронный распределитель импульсов, содержащий в каждом разряде ячейки, каждая из которых состоит из

0

5

триггера и элемента И-НЕ, первый вход триггера соединен с первым входом элемента И-НЕ и подключен к шине уст тановки той же ячейки, первый выход триггера подключен к третьему входу триггера и второму входу элемента И-НЕ, а второй выход триггера соединен с вторым входом триггера, причем первый и второй входы триггера подключены по схеме И, выходная шина i-й ячейки, являющаяся выходом элемента И-НЕ, подключена к шине установки последующей (i+J)-й ячейки и третьему входу элемента И-НЕ предыдущей {1-1)-й ячейки, отличающийся тем, что, с целью упрощения, триггер каждой ячейки выполнен в виде двух нагрузочных элементов и трех ЩЦ1-транзисторов, причем затворы первого и второго МДП- транзисторов, которые соединены последовательно, являются соответственно первым и вторым входами триггера, а нагрузочные элементы включены между шиной питания и стоками соответственно первого и третьего МДП-транзисторов, являющимися соответственно первым и вторым выходами триггера, 0 затвор третьего МДП-транзистора является третьим входом триггера, исток подключен к точке последовательного соединения первого и второго МДП- транзисторов триггера последующей (1+1)-й ячейки, а исток второго МДП- транзистора триггера соединен с общей шиной.

0

5

5

(Ul)

| Асинхронный распределитель | 1982 |

|

SU1022309A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Асинхронный распределитель | 1982 |

|

SU1064461A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-30—Публикация

1986-06-17—Подача