Изобретение относится к вычислительной технике и может быть использовано в асинхронных устройствах хранения информации.

Цель изобретения - упрощение регистра.

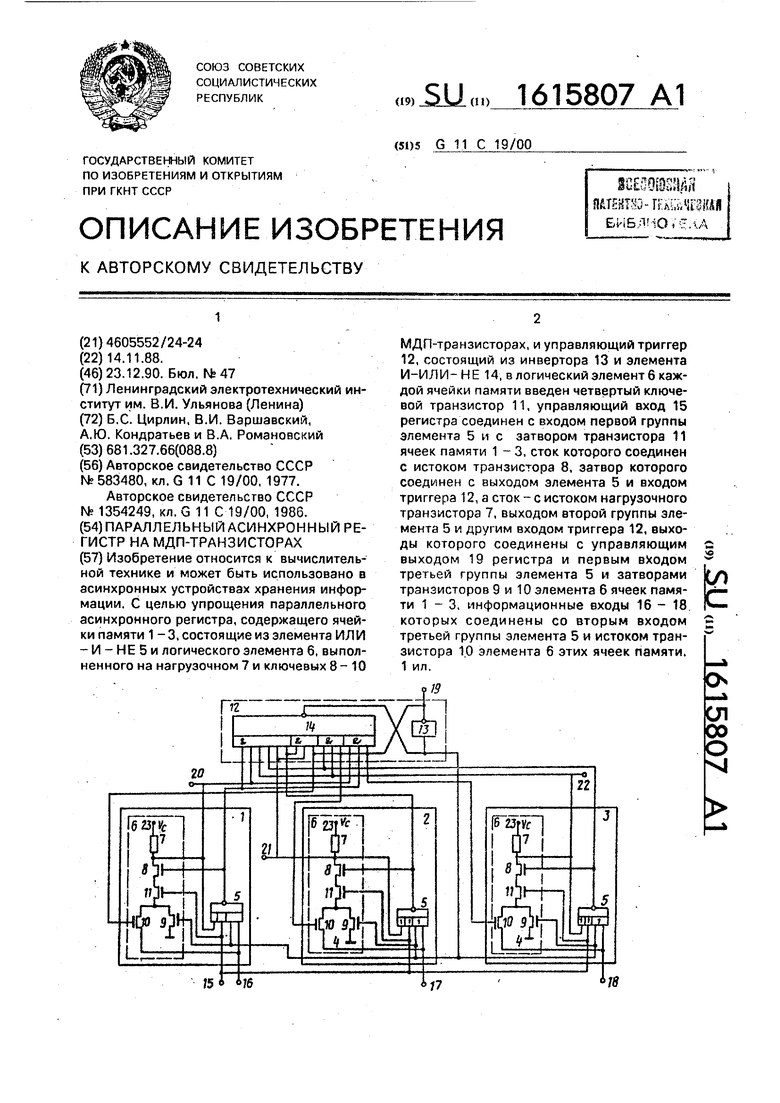

На чертеже приведена схема регистра.

Регистр содержит ячейки 1 - 3 памяти, шину нулевого потенциала. Каждая ячейка памяти состоит из элемента И/1И-И-НЕ 5 и логического элемента 6, выполненного на нагрузочном 7 и первом 8, втором 9, третьем 10 и четвертом 11 ключевых МДП-транзисторах, управляющий триггер 12, состоящий из инвертора 13 и элемента И-ИЛИ-НЕ 14. На чертеже показаны также вход 15 разрешения записи, информационные входы 16 - 18, выход 19 индикации записи, информационные выходы 20 - 22, шина 23 питания. Вход 15 и выход 19 являются управляющими.

Регистр работает следующим образом.

В исходном состоянии на управляющем входе 15 регистра имеется значение О, в результате чего на выходах элементов 5 и б всех ячеек 1-3 памяти имеются значения 1, на выходе элемента 14 управляющего триггера 12 - значение О, а на выходе инвертора 13, т.е. на управляющем выходе 19 регистра - значение 1,

После того как на информационных входах 16-18 ячеек 1-3 памяти установлены значения разрядов записываемого кода, на управляющий вход 15 регистра подается значение 1, разрешающее запись кода в регистр. При этом, если на каком-ямбо из информационных входов 16-18 имеется значение 1, то на выходе элемента 5 соответствующей из ячеек - 3 памяти появится значение О, а на выходе ее элемента 5 сохранится значение 1, если на данном информационном входе имеется значение О, то на выходе элемента 5 этой ячейки памяти сохранится значение 1, а на выходе ее элемента 6 появится значение О. Когда значения на выходах элементов 5 и 6 станут противоположными у всек ячеек 1 - 3 памяти, T.is. после того как во все ячейки 1 - 3 памяти регистра запишутся разряды кода, на выходе элемеита 14 управляющего триггера 12 появится значение 1, которое отсечет ячейки 1-3 памяти от информационных входов 16- 18. а затем на выходе инвертора 13 управляющего триггера 12, т.е. на управляющем выходе 19 регистра - значение О, что свидетельствует о зааер- шении процесса записи в регистр.

Сразу после этого можно начать изменение значений на информационных входах 16-18 регистра, подготавливая разряды

нового кода для записи. При этом, поскольку на затворы транзисторов 10 элементов 6 ячеек памяти 1 - 3 поступают значения О с управляющего выхода 19 регистра, эти 5 транзисторы закрыты и не препятствуют из- менению значений на информационных входах 16 - 18 ячеек 1 - 3 памяти (не пропускают на эти входы потенциал шины 23 регистра, к которой через открытые

0 транзисторы 9 этих элементов подключены стоки транзисторов 10).

Перед тем как осуществить очередную запись разрядов кода 5 регистр необходимо привести его в исходное состояние, для чего

5 на управляющий вход 15 регистра подается значение О. В результате на выходах элементов 5 и 6 всех ячеек 1 - 3 памяти появятся значения 1, после чего сначала на выходе элемента 14 управляющего триггера

0 12 появится значение О, которое снимет отсечку ячеек 1 - 3 памяти от информационных входов 16 - 18 (в частности, закроет транзисторы 9 глементов 6 этих ячеек памяти, что отключит стоки транзисторов 10 этих

5 элементов от шин 23 регистра), а затем на выходе инвертора 13 управляющего триггера 12, т.е. на управляющем выходе-19 реги- стрк - значение 1, свидетельствующее о завершении перехода регистра-в исходное

0 состояние.

В предлагаемом регистре, так же, как и в известном, при управлении процессом записи информации в регистр м его возвратом в исходное состояние с помощью сигнала на

5 управляющем выходе 19 регистра устраняется влияние разброса задержек элементов последнего на его работу.

Оценивая сложность параллельного асиихроннсго регистра числом МОПтраизи0 сторов, необходимых для его реализации, получают {14п + 4), где л - чясло ячеек памяти регистра. В известном регистре эта величина составляет (16п + 17), т.е. имеет место упрощение регистра для любого п.

5 Цикл работы составляет 6г, где т - задержка одного элемента регистра. Формула изобретения Параллельный асинхронный регистр на МДП-транзисторах, содержащий п ячеек па0 мяти, каждая из которых состоит из элемента ИЛИ-1/1-НЕ и логического элемента, выполненного на нагрузочном и трех ключевых транзисторах, причем сток нагрузочного транзистора соединен с шиной питания

5 регистра, а исток - со стоком первого 5слю- чевого транзисторг и с входогл первой группы 3ii8fv«eHTa ИЛИ - И - НЕ и йвлзется соответствукгщим информационным выходом регистра, затвор первого ключевого транзисторэ соединен с выходом элемента

ИЛИ-И-НЕ, вход второй группы которого является входом разрешения записи регистра, а первый вход третьей группы соединен с затвором второго ключевого транзистора логического элемента данной ячейки памяти и является соответствующим информационным входом регистра, исток второго ключевого транзистора логического элемента соединен с шиной нулевого потенциала регистра, а сток - со стоком третьего ключевого транзистора логического элемента данной ячейки памяти, и управляющий триггер, состоящий иэ элемента И-ИЛИ-НЕ и инвертора, вход которого соединен с выходом элемента И-ИЛИ-НЕ, а выход-с первыми входами п групп элемента Й-ИЛИ-НЕ, вторые и третьи входы которых соединены со стоками и затворами первых ключевых транзисторов логических элементов со- ответствующих ячеек памяти и с входами

(п + 1)-й группы элемента И-ИЛИ-НЕ управляющего триггера, отличающий- с я тем, что. с целью упрощения регистра, логический элемент каждой ячейки памяти содержит четвертый ключевой транзистор, исток и сток которого соединены соответственно со стоком третьего и истоком первого ключевых транзисторов данного логического элемента, а затвор - с входом второй группы элемента ИЛИ - И - НЕ данной ячейки памяти, первый вход третьей группы которого соединен с истоком третьего ключевого транзистора логического элемента данной ячейки памяти, затвор которого соединен с выходом инвертора управляющего триггера и является выходом индикации записи регистра, а вход инвертора управляющего триггера соединен с вторыми входами третьей группы элементов ИЛИ - И НЕ каждой ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| Параллельный асинхронный регистр | 1988 |

|

SU1607016A1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1989 |

|

SU1665405A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1494041A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2050600C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

Изобретение относится к вычилительной технике и может быть использовано в асинхронных устройствах хранения информации. С целью упрощения параллельного асинхронного регистра, содержащего ячейки памяти 1-3, состоящие из элемента ИЛИ-И-НЕ 5 и логического элемента 6, выполненного на нагрузочном 7 и ключевых 8-10 МДП-транзисторах, и управляющий триггер 12, состоящий из инвертора 13 и элемента И-ИЛИ-НЕ 14, в логический элемент 6 каждой ячейки памяти введен четвертый ключевой транзистор 11, управляющий вход 15 регистра соединен с входом первой группы элемента 5 и с затвором транзистора 11 ячеек памяти 1-3, сток которого соединен с истоком транзистора 8, затвор которого соединен с выходом элемента 5 и входом триггера 12, а сток - с истоком нагрузочного транзистора 7, входом второй группы элемента 5 и другим входом триггера 12, выходы которого соединены с управляющим выходом 19 регистра и первым входом третьей группы элемента 5 и затворами транзисторов 9 и 10 элемента 6 ячеек памяти 1-3, информационные входы 16-18 которых соединены со вторым входом третьей группы элемента 5 и истоком транзистора 10 элемента 6 этих ячеек памяти. 1 ил.

| Параллельный однофазный регистр | 1976 |

|

SU583480A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Параллельный асинхронный регистр | 1986 |

|

SU1354249A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-12-23—Публикация

1988-11-14—Подача