(54) СТАТИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ - НА МДПгТРАНЗИСТОРАХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| Интегральное запоминающее устройство | 1974 |

|

SU523455A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Элемент памяти | 1984 |

|

SU1274000A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

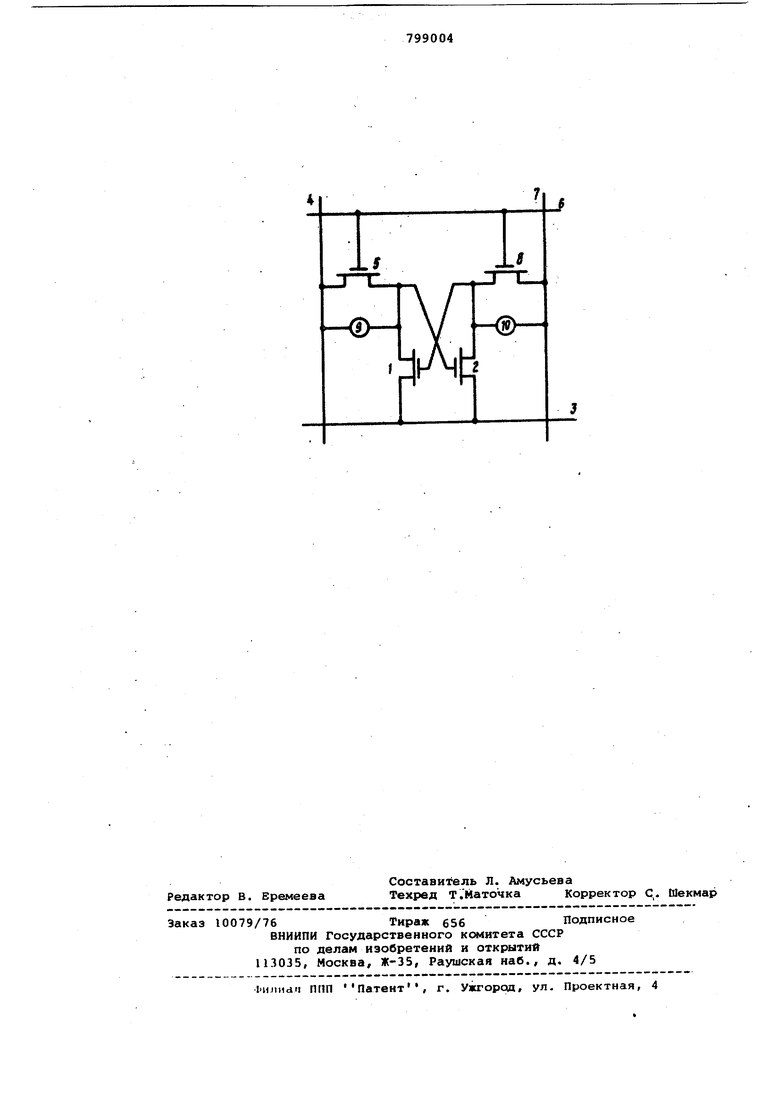

Изобретение относится к электронике и может быть использовано дл проектирования ЗУ на МДП-транзистора Известно устройство, содержащее статические ячейки памяти на шести- . транзисторах, одна из которых содержит две шины питания и три управлякяц шины 1 .,. Однако при проектирований БИС ЗУ большой емк.ости с использованием это ячейки памяти площадь матрицы накопи теля получается недопустимо большой для реализации ЗУ емкостью более 4 кбит. Даже уменьшение размеров МДПтранзисторов не позволяет уменьшить площадь ячейки из-за ограничений, связанных с наличием трех управляющих шин и двух шин питания. Наиболее близким по технической сущности к предлагаемому является статическая ячейка памяти, представляющая собой триггер на двух МДПтранзисторах и двух резисторах, которые одними выводами соединены с уз лами триггера, а другими - с шииой питания. Два других транзистора работают как двунаправленные вентили между узлами триггера и разрядными шинами. Затворы вентильных транзисторов подключены к словарной шине. Сопротивление нагрузочных транзисторов должно быть маньше сопротивления утечки стоков закЕилтых МДП-транзисторов в узле триггера, имеющем высокий логический уровень 2. такая статическая ячейка памяти наряду с минимальной п.лощадью занимаемой активными элементами, имеет низкую потреб.пяемук) мощность в режиме хранения, так как нетрудно получить резисторы из пленки поликристаллического кремния, имеющего удельное поверхностное сопротивление более 1 гОм/о, но и эта ячейка памя.ти на четырех МДП-транзисторах и двух резисторах имеет две шины питания и три управляющие шины, что не позволяет реализацию с применением этой ячейки матрицы накопления с высокой плотностью интеграции. Цель изобретения - упрсщение ячейки памяти и повышение ее надежности . поставленная цель достигается тем, JTO в статической ячейке памяти на МДП-транзисторах, содержащей первый л второй транзисторы, истоки которых соединены с шиной питания, затворы первого и второго транзисторов соеди нены, соответственно, со стоками второго и первого транзисторов, кото рые подключены, соответственно, -к истокам третьего и четвертого транзи сторов, стоки которых подключены к разрядным шинам, затворы третьего и четвертого транзисторов подключены к числовой шине j и нагрузочные элементы, одни из выводов которых подкл чены к стокам первого и второго тран зисторов, вторые выводы нагрузочных элементов подключены к разрядным шинам. На чертеже представлена принципиальная схема ячейки памяти. Устройство содержит истоки транзисторов 1 и 2, соединенные с шиной 3 питания. Затвор транзистора соединен со стоком транзистора 2, а затвор транзистора 2 соединен со стоке транзистора 1. Между стоком транзистора 1 и разрядной 4 шиной включён транзистор 5, затвор которого соединен счисловой шиной б. Межд стоком транзистора 2 и разрядной шиной 7 включен транзистор 8, затвор которого также соединен с числовой ШИНОЙ б. Между стоком транзистора 1 и разрядной шиной 4, и между стоком транзистора 2 и разрядной шиной 7 включены, соответственно, элементы и 10, сопротивление-утечки которых . меньше сопротивления утечки стока МДП-транзиСтора 1 или 2 в закрытом состоянии. В режиме хранения информации чис ловая шима б имеет потенциал ниже порогового напряжения транзисторов 5 и 8 (логический О). Если J сток транзистора 1 имеет потенциал выше порогового напряжения транзист ра 2 (логическая ), а сток тра зистора 2 имеет потенциал логическо то это состояние хранится неограниченно длительное время, есл разрядные шины имеют потенциал выше потенциала стока транзистора 1 и если ток утечки узла стока транзисто ра 1 не больше тока заряда этого уз ла от разрядной шины через элемент 9, а ток разряда узла стока траИзистЬра 2 не меньше тока заряда этого Узла от разрядной шины через элемен Аналогично происходит хранение логической 1 в узле стока транз стора. 2. Для записи в ячейку нужной инфор мации необходимо обеспечить пот.енци °/аш числовой шины не ниже,чем сумма напряжений логической i ячейки порогового напряжения транзистора 5 или 8. ТЗсли при зтом потенциал одной из разрядных шин уменьшить до уровня не выше логического О .ячейки, то В узле ячейки, подключенном к этой v разрядной шине через вентильный транзистор, установится состояние логического О, а в другом узле логической . При считывании потенциалы разрядных шин соответствуют режиму хранения, а потенциал на числовой шине - режиму записи. При этом на разрядной шине, подключенной через открытый вентильный транзистор к узлу ячейки находящемуся в состоянии логического О, появится считываемый сигнал в результате разряда шины через цепочку двух последовательно включенных открытых транзисторов 5-1 или 8 - 2. В матрице накопителя каждая пара разрядных шин является общей для ячеек. Чтобы при обращении к одной ячейке памяти информация в остальных ячейках, подключенных к данной паре разрядных шин,не разрушалась в процес се одного периода обращения и в процессе многократных обращений, необходимо, чтобы постоянная времени емкости узла хранения ячейки и сопротивления элемента утечки была на несколько порядков больше периода обращения, а период обращения, когда потенциал хотя бы на одной из разрядных шин меньше уровня его в режиме хранения. был е больше паузы. Оба эти условия легко выполнимы в БИС ОЗУ при сохранении высоких эксплуатационных и временных характеристик памяти. Формула изобретения Статическая ячейка памяти на МДПтранзисторах, содержащая первый и второй транзисторы, истоки которых соединены с шиной питания, затворы первого и второго транзисторов соединены, соответственно, со стоками второго и первого транзисторов, которые под ключёны, соответственно, к истокам третьего и четвертого транзисторов, стоки которых подключены к разрядным шинам, затворы третьего и четвертого транзисторов подключены к числовой шине, и нагрудочныг элементы, одни из выводов которых подключены к стокам первого и второго транзисторов/ отличающаяся тем, что, с целью упрощения ячейки памяти и повышения ее надежности, вторые выводы нагрузочных элементов подключены к разрядным шинам. Источники информации, принятые во внимание при экспертизе 1.Электроника, 1974, т. 47, W 5, с. 37-41. 2.Электроника, 1977, т. 50, 10, с. 38-44 (прототип).

Авторы

Даты

1981-01-23—Публикация

1979-03-30—Подача