Изобретение относится к цифровой вычислительной технике и может быть использовано для построения унифицированных блоков синхронизации запоминающих устройств (ЗУ) с плавной адаптацией к временным характеристикам накопителя.

Целью изобретения является повышение точности и сокращение времени настройки.

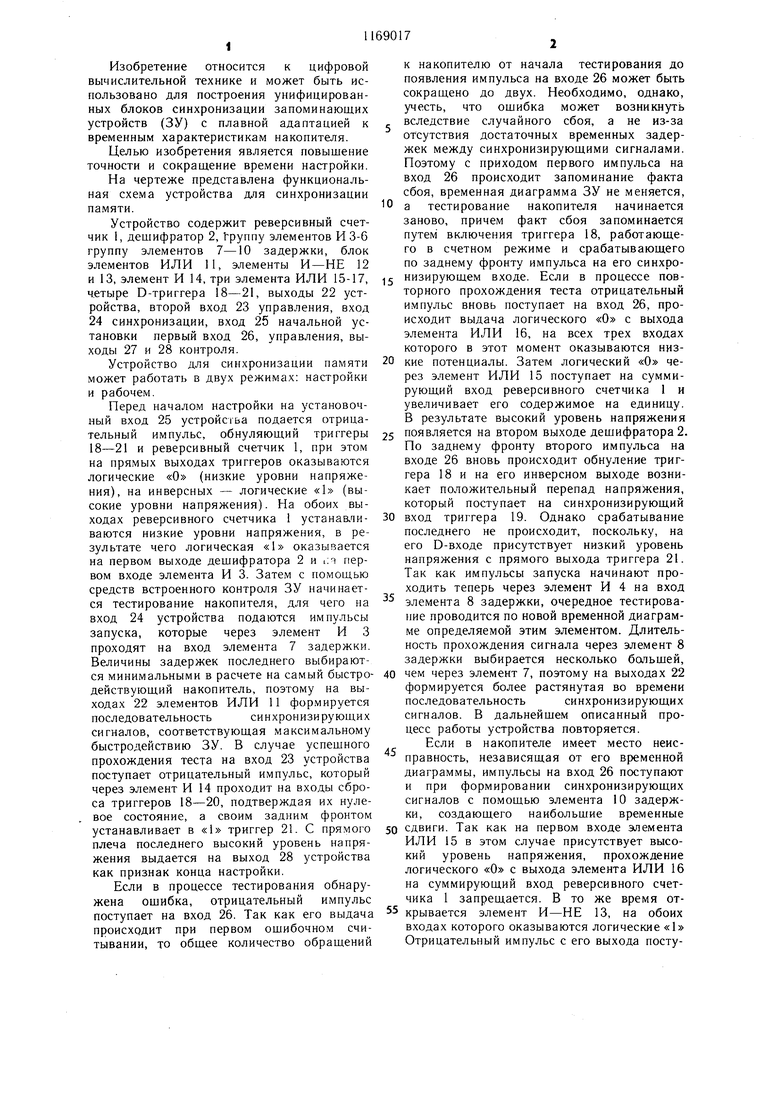

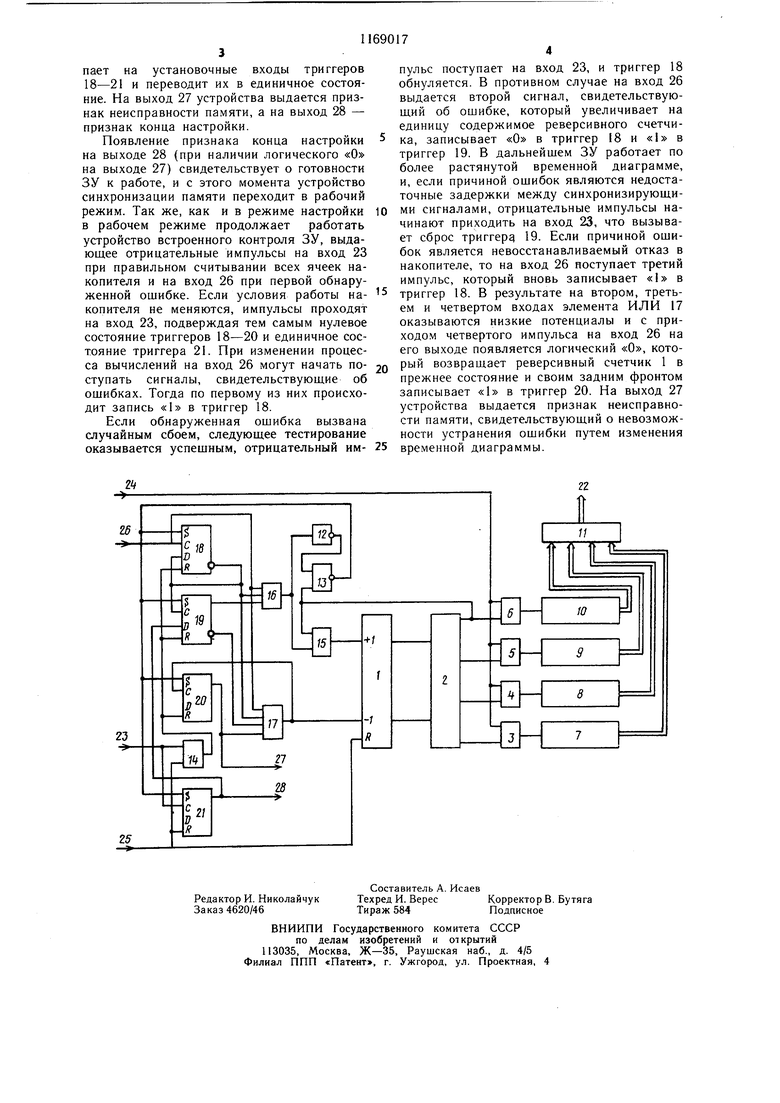

На чертеже представлена функциональная схема устройства для синхронизации памяти.

Устройство содержит реверсивный счетчик 1, дешифратор 2, Группу элементов И 3-6 группу элементов 7-10 задержки, блок элементов ИЛИ 11, элементы И-НЕ 12 и 13, элемент И 14, три элемента ИЛИ 15-17, четыре D-триггера 18-21, выходы 22 устройства, второй вход 23 управления, вход 24 синхронизации, вход 25 начальной установки первый вход 26, управления, выходы 27 и 28 контроля.

Устройство для синхронизации памяти может работать в двух режимах: настройки и рабочем.

Перед началом настройки на установочный вход 25 устройсгьа подается отрицательный импульс, обнуляющий триггеры 18-21 и реверсивный счетчик 1, при этом на пря.мых выходах триггеров оказываются логические «О (низкие уровни напряжения), на инверсных - логические «1 (высокие уровни напряжения). На обоих выходах реверсивного счетчика 1 устанавливаются низкие уровни напряжения, в результате чего логическая «1 оказывается на первом выходе дешифратора 2 и i:i первом входе элемента И 3. Затем с помощью средств встроенного контроля ЗУ начинается тестирование накопителя, для чего на вход 24 устройства подаются импульсы запуска, которые через элемент И 3 проходят на вход элемента 7 задержки. Величины задержек последнего выбираются минимальными в расчете на самый быстродействующий накопитель, поэтому на выходах 22 элементов ИЛИ 11 формируется последовательностьсинхронизирующих

сигналов, соответствующая максимальному быстродействию ЗУ. В случае успешного прохождения теста на вход 23 устройства поступает отрицательный импульс, который через элемент И 14 проходит на входы сброса триггеров 18-20, подтверждая их нулевое состояние, а своим задним фронтом устанавливает в «1 триггер 21. С прямого плеча последнего высокий уровень напряжения выдается на выход 28 устройства как признак конца настройки.

Если в процессе тестирования обнаружена ошибка, отрицательный импульс поступает на вход 26. Так как его выдача происходит при первом ошибочном считывании, то общее количество обращений

к накопителю от начала тестирования до появления импульса на входе 26 может быть сокращено до двух. Необходимо, однако, учесть, что ошибка может возникнуть вследствие случайного сбоя, а не из-за отсутствия достаточных временных задержек между синхронизирующими сигналами. Поэтому с приходом первого импульса на вход 26 происходит запоминание факта сбоя, временная диаграмма ЗУ не меняется,

а тестирование накопителя начинается заново, причем факт сбоя запоминается путем включения триггера 18, работающего в счетном режиме и срабатывающего по заднему фронту импульса на его синхронизирующем входе. Если в процессе повторного прохождения теста отрицательный импульс вновь поступает на вход 26, происходит выдача логического «О с выхода элемента ИЛИ 16, на всех трех входах которого в этот момент оказываются низкие потенциалы. Затем логический «О через элемент ИЛИ 15 поступает на суммирующий вход реверсивного счетчика 1 и увеличивает его содержимое на единицу. В результате высокий уровень напряжения

появляется на втором выходе дешифратора 2. По заднему фронту второго импульса на входе 26 вновь происходит обнуление триггера 18 и на его инверсном выходе возникает положительный перепад напряжения, который поступает на синхронизирующий

вход триггера 19. Однако срабатывание последнего не происходит, поскольку, на его D-входе присутствует низкий уровень напряжения с прямого выхода триггера 21. Так как импульсы запуска начинают проходить теперь через элемент И 4 на вход

элемента 8 задержки, очередное тестирование проводится по новой временной диаграмме определяемой этим элементом. Длительность прохождения сигнала через элемент 8 задержки выбирается несколько бапьшей,

чем через элемент 7, поэтому на выходах 22 формируется более растянутая во времени последовательностьсинхронизирующих

сигналов. В дальнейшем описанный процесс работы устройства повторяется.

Если в накопителе имеет место неисправность, независящая от его временной диаграммы, импульсы на вход 26 поступают и при формировании синхронизирующих сигналов с помощью элемента 10 задержки, создающего наибольшие временные

сдвиги. Так как на первом входе элемента ИЛИ 15 в этом случае присутствует высокий уровень напряжения, прохождение логического «О с выхода элемента ИЛИ 16 на суммирующий вход реверсивного счетчика 1 запрещается. В то же время открывается элемент И-НЕ 13, на обоих входах которого оказываются логические «1 Отрицательный импульс с его выхода поступает на установочные входы триггеров 18-21 и переводит их в единичное состояние. На выход 27 устройства выдается признак неисправности памяти, а на выход 28 - признак конца настройки.

Появление признака конца настройки на выходе 28 (при наличии логического «О на выходе 27) свидетельствует о готовности ЗУ к работе, и с этого момента устройство синхронизации памяти переходит в рабочий режим. Так же, как и в режиме настройки в рабочем режиме продолжает работать устройство встроенного контроля ЗУ, выдающее отрицательные импульсы на вход 23 при правильном считывании всех ячеек накопителя и на вход 26 при первой обнаруженной ошибке. Если условия работы накопителя не меняются, импульсы проходят на вход 23, подверждая тем самым нулевое состояние триггеров 18-20 и единичное состояние триггера 21. При изменении процесса вычислений на вход 26 могут начать поступать сигналы, свидетельствующие об ошибках. Тогда по первому из них происходит запись «1 в триггер 18.

Если обнаруженная ощибка вызвана случайным сбоем, следующее тестирование оказывается успещным, отрицательный импульс поступает на вход 23, и триггер 18 обнуляется. В противном случае на вход 26 выдается второй сигнал, свидетельствующий об ошибке, который увеличивает на единицу содержимое реверсивного счетчика, записывает «О в триггер 18 и «I в триггер 19. В дальнейшем ЗУ работает по более растянутой временной диаграмме, и, если причиной ошибок являются недостаточные задержки между синхронизирующими сигналами, отрицательные импульсы начинают приходить на вход 23, что вызывает сброс триггеру 19. Если причиной ошибок является невосстанавливаемый отказ в накопителе, то на вход 26 поступает третий импульс, который вновь записывает «1 в

триггер 18. В результате на втором, третьем и четвертом входах элемента ИЛИ 17 оказываются низкие потенциалы и с приходом четвертого импульса на вход 26 на его выходе появляется логический «О, который возвращает реверсивный счетчик 1 в прежнее состояние и своим задним фронтом записывает «1 в триггер 20. На выход 27 устройства выдается признак неисправности памяти, свидетельствующий о невозможности устранения ошибки путем изменения временной диаграммы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации памяти | 1982 |

|

SU1101805A1 |

| Устройство для регенерации информации в динамической памяти | 1981 |

|

SU1012346A1 |

| Устройство для синхронизации памяти | 1984 |

|

SU1247853A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Устройство для синхронизации блоков памяти | 1986 |

|

SU1439566A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Устройство для программного управления | 1981 |

|

SU976428A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Устройство для синхронизации памяти | 1988 |

|

SU1594516A1 |

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПАМЯТИ, содержащее реверсивный счетчик, вход прямого счета которого подключен к выходу первого элемента ИЛИ, выходы соединены с входами дешифратора, а вход начальной установки подключен к первому входу элемента И и является входом начальной установки устройства, причем выходы дефширатора соединены с входами первой группы блока элементов И, входы второй группы которого являются входом синхронизации устройства, а выходы соединены с соответствующими входами блоков формирования синхросигналов, выходы которых подключены к входам блока элементов ИЛИ, выходы блока элементов ИЛИ являются выходами синхронизации устройства, первый выход дешифратора соединен с первыми входами элемента И-НЕ и первого элемента ИЛИ, второй вход элемента И-НЕ подключен к выходу инвертора, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, оно содержит первый. второй, третий и четвертый триггеры, второй и третий элементы ИЛИ, S-входы первого, второго, третьего и четвертого триггеров подключены к выходу элемента И-НЕ, вход которого соединен с вторым входом первого э-лемента ИЛИ и выходом второго элемента ИЛИ, первый вход которого подключен к входу синхронизации первого триггера, первому в.чоду третьего элемента ИЛИ и является первым входом управ.чепия устройства, второй вход соединен с входом синхронизации второго триггера, с информационным входом и инверсным выходом первого триггера и вторым входом третьего элемента ИЛИ соответственно, а третий вход подключен к прямому выходу i второго триггера, инверсный выход которого соединен с третьим входом третьего (Л элемента ИЛИ, четвертый вход которого подключен к пря.мому выходу третьего триггера и является первым выходом контроля устройства, R-входы первого, второго и третьего триггеров соединены с выходом элемента И, R-вход четвертого триггера подключен к входу начальной установки реверсивного счетчика, вход обратного счета которого соединен с входом синхронизао: ции третьего триггера и с выходом третьесо го эле.:е11та ИЛИ, прямой выход четвертого триггера подключен к информадаонному входу второго триггера и является вторым выходом контроля ;й тройства, а вход синхронизации четвертого триггера соединен с вторым входом элемента И и яв,дяется вторым входом управления устройств.

| Устройство для управления оперативной памятью | 1978 |

|

SU752338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство синхронизации памяти | 1982 |

|

SU1101805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1983-12-30—Подача