4

сд

с ;о

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многоразрядных цифровых схема методом сигнатурного анализа.

Целью изобретения является повышение достоверности контроля при произвольном количестве информационных входов.

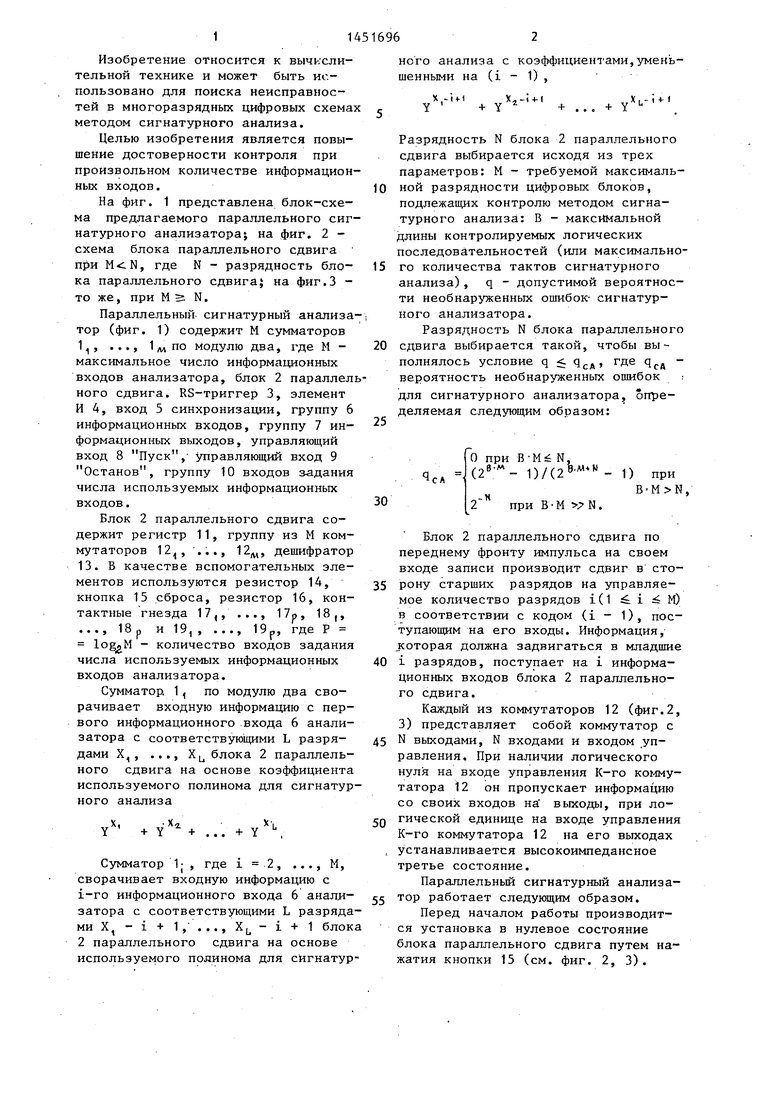

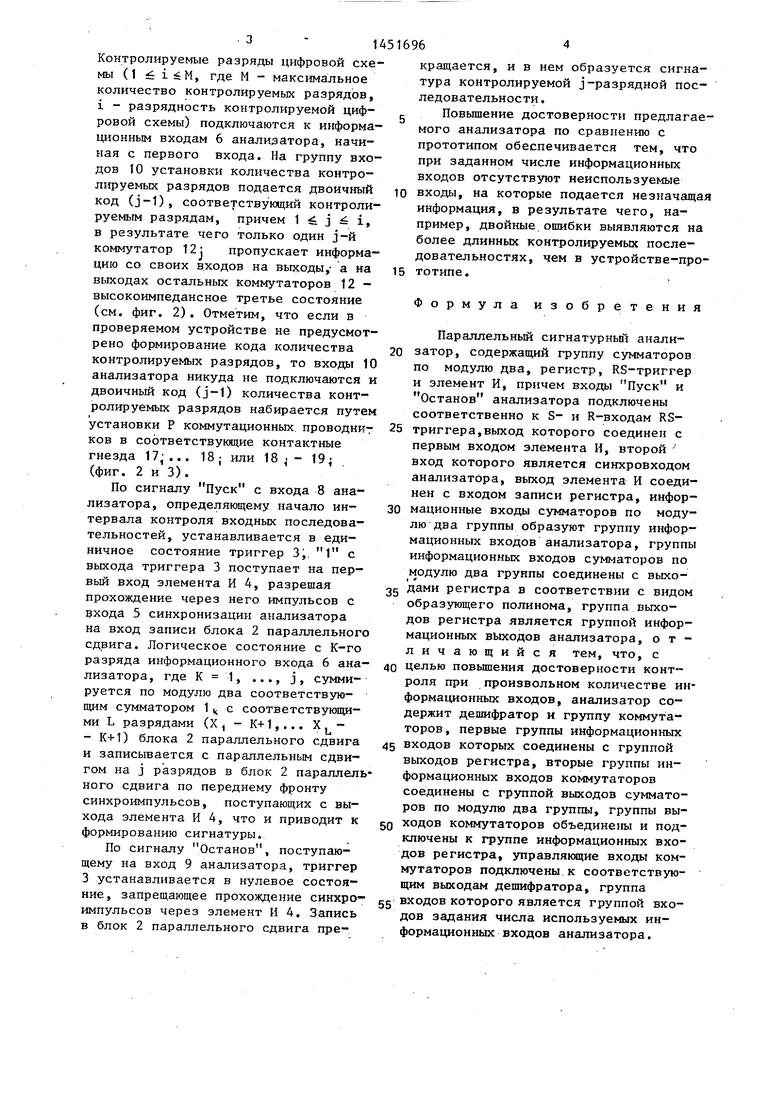

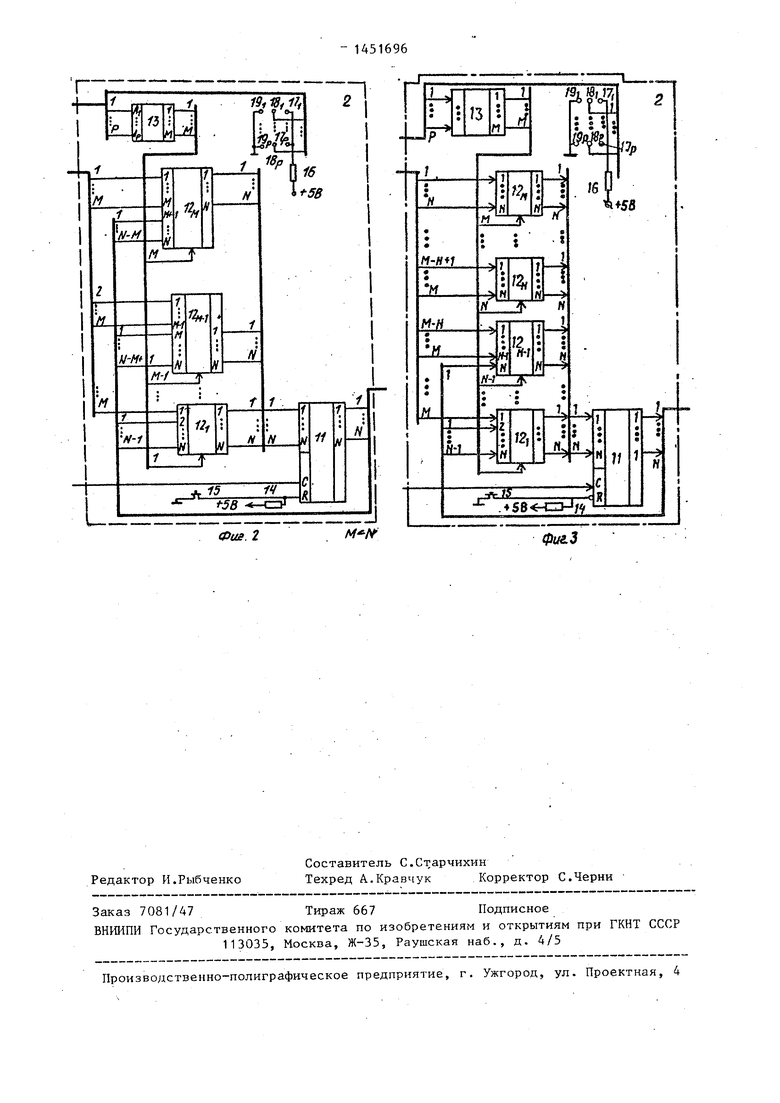

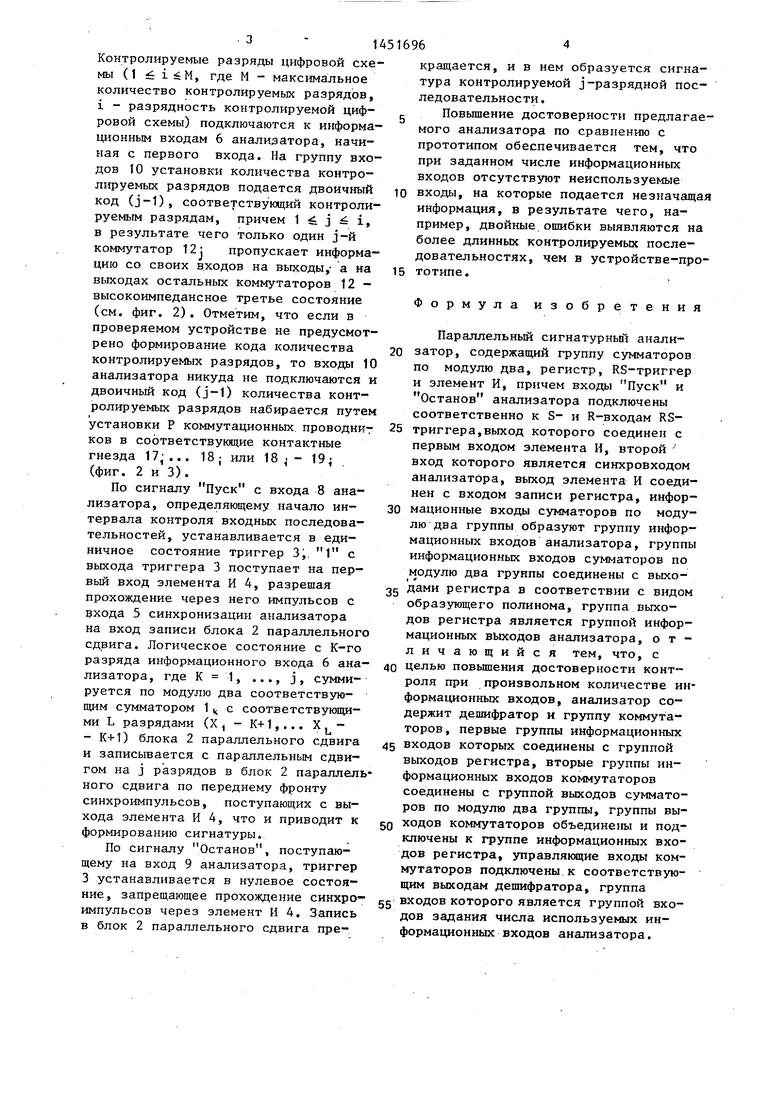

На фиг. 1 представлена блок-схема предлагаемого параллельного сигнатурного анализатора; на фиг. 2 - схема блока параллельного сдвига при , где N - разрядность блока параллельного сдвига; на фиг.З - то же, при М S N.

Параллельный сигнатурный анализа тор (фиг. 1) содержит М сумматоров 1, ..., 1/и по модулю два, где М - максимальное число информационных входов анализатора, блок 2 параллелного сдвига. RS-триггер 3, элемент И 4, вход 5 синхронизации, группу 6 информационных входов, группу 7 информационных выходов, управляющий вход 8 Пуск, управляющий вход 9 Останов, группу 10 входов задания числа используемых информационных входов.

Блок 2 параллельного сдвига содержит регистр 11, группу из М коммутаторов 12, ..., 12, дешифратор 13. В качестве вспомогательных элементов используются резистор 14, кнопка 15 сброса, резистор 16, контактные гнезда 17,, ..., 17р, 18,, ..., 18р и 19, , ..., 19р, где Р - количество входов задания числа используемых информационных входов анализатора.

Сумматор. 1 , по модулю два сворачивает входную информацию с первого информационного .входа 6 анализатора с соответствующими L разрядами Х , ..., XL, блока 2 параллельного сдвига на основе коэффициента используемого полинома для сигнатурного анализа

r il

Xi + Y +

+ Y

Сумматор 1j , где , ..., М, сворачивает входную информацию с i-ro информационного входа 6 аналл- затора с соответствующими L разрядами Х - i + 1 ,..., Х - i + 1 блока 2 параллельного сдвига на основе используемого полинома для сигнатурного анализа с коэффициентами,уменьшенными на (i - 1) ,

+ Y

X,-i+-t

+ + Y

«to i

I 4- (

Разрядность N блока 2 параллельного сдвига выбирается исходя из трех параметров: М - требуемой максимальной разрядности цифровых блоков, подлежащих контролю методом сигнатурного анализа: В - максимальной длины контролируемых логических последовательностей (или максимального количества тактов сигнатурного анализа), q - допустимой вероятности необнаруженных ошибок- сигнатурного анализатора.

Разрядность N блока параллельного

сдвига выбирается такой, чтобы выполнялось условие q . г-Дб ЧСА вероятность необнаруженных ошибок .

для сигнатурного анализатора, определяемая следующим образом:

ICA

О при В-Мй N, ( 1)7(

при В-М : N.

1) при

,

Блок 2 параллельного сдвига по переднему фронту импульса на своем входе записи производит сдвиг в сторону старших разрядов на управляемое количество разрядов i(1 i М) в соответствии с кодом (i - 1), поступающим на его входы. Информация, которая должна задвигаться в младшие

i разрядов, поступает на i информационных входов блока 2 параллельного сдвига.

Каждый из коммутаторов 12 (фиг.2, 3) представляет собой коммутатор с

N выходами, N входами и входом .управления. При наличии логического нуля на входе управления К-го коммутатора 12 он пропускает информацию со своих входов на выходы, при логической единице на входе управления

К-го коммутатора 12 на его выходах устанавливается высокоимпедансное третье состояние.

Параллельный сигнатурный анализатор работает следующим образом.

Перед началом работы производится установка в нулевое состояние блока параллельного сдвига путем нажатия кнопки 15 (см. фиг. 2, 3).

10

15

Контролируемые разряды цифровой схемы (1 i ёМ, где М - максимальное количество контролируемых разрядов, i - разрядность контролируемой цифровой схемы) подключаются к информа- ционным входам 6 анализатора, начиная с первого входа. На группу входов 10 установки количества контро- Л1фуемых разрядов подается двоичный код (J-1), соответству ющий контролируемым разрядам, причем 1 j i, в результате чего только один j-й коммутатор 12j пропускает информацию со своих входов на выходы,- а на выходах остальных коммутаторов 12 - высокоимпедансное третье состояние (см. фиг. 2). Отметим, что если в проверяемом устройстве не предусмотрено формирование кода количества контролируемых разрядов, то входы 10 анализатора никуда не подключаются и двоичный код (J-1) количества контролируемых разрядов набирается путем установки Р коммутационных, проводников в соответствующие контактные гнезда 17... 18; или 18.- 19 (фиг. 2 и 3).

По сигналу Пуск с входа 8 анализатора, определяющему начало интервала контроля входных последовательностей, устанавливается в единичное состояние триггер 3. 1 с выхода триггера 3 поступает на первый вход элемента И 4, разрешая прохождение через него импульсов с эхода 5 синхронизации анализатора на вход записи блока 2 параллельного сдвига. Логическое состояние с К-го

кращается, и в нем образуется сиг тура контролируемой j-разрядной п ледовательности .

Повьшение достоверности предлаг мого анализатора по сравнению с прототипом обеспечивается тем, чт при заданном числе информационных входов отсутствуют неиспользуемые входы, на которые подается незнача информация, в результате чего, например, двойные.ошибки выявляются более длинных контролируемых после довательностях, чем в устройстве-п тотипе.

Ф

ормула изобретени

20

Параллельный сигнатурньпЧ анализатор, содержащий группу сумматоро по модулю два, регистр, RS-тригге и элемент И, причем входы Пуск и Останов анализатора подключены соответственно к S- и R-входам RS- 25 триггера,выход которого соединен с первым входом элемента И, второй вход которого является синхровходом анализатора, выход элемента И соеди нен с входом записи регистра, инфор 30 мационные входы сумматоров по моду лю два группы образуют группу инфор мационных входов анализатора, групп информационных входов сумматоров по модулю два группы соединены с выхо- 35 дами регистра в соответствии с видо образующего полинома, группа выходов регистра является группой инфор мационных выходов анализатора, от личающийся тем, что, с

- aiui4 inv;n тем. что. с

разряда информационного входа 6 ана- 40 Целью повьшения достоверности контTTtTQ Я Р Пга Г гт/ ы-

лизатора, где К 1, ..., j, суммируется по модулю два соответствующим сумматором 1 ,( с соответствующими L разрядами (X , - К+1,... X j - - К+1) блока 2 параллельного сдвига и записывается с параллельным сдвигом на j разрядов в блок 2 параллель ного сдвига по переднему фронту синхроимпульсов, поступающих с выхода элемента И 4, что и приводит к формирова}шю сигнатуры.

По сигналу Останов, поступающему на вход 9 анализатора, триггер 3 устанавливается в нулевое состояроля при произвольном количестве и формационных входов, анализатор содержит дешифратор и группу коммутаторов, первые группы информационных

45 входов которых соединены с группой выходов регистра, вторые группы информационных входов коммутаторов соединены с группой выходов сумматоров по модулю два группы, группы вы50 оцов коммутаторов объединены и подключены к группе информационных входов регистра, управлякяцие входы коммутаторов подключены к соответствующим выходам дешифратора, группа

50 оцов коммутаторов объединены и подключены к группе информационных входов регистра, управлякяцие входы коммутаторов подключены к соответствующим выходам дешифратора, группа

,Г- ГТ- --«ff «- vj-j J 1 k TllllO.

ние, запрещающее проховдение синхро- вхокоз которого является группой вхоИМПУЛЬСОВ чепрч ЧПРМРНТ Н А J lrTTio .

импульсов через элемент И 4. Запись в блок 2 параллельного сдвига предов задания числа используемых информационных входов анализатора.

1451696

кращается, и в нем образуется сигнатура контролируемой j-разрядной последовательности .

Повьшение достоверности предлагаемого анализатора по сравнению с прототипом обеспечивается тем, что при заданном числе информационных входов отсутствуют неиспользуемые входы, на которые подается незначащая информация, в результате чего, например, двойные.ошибки выявляются на более длинных контролируемых последовательностях, чем в устройстве-прототипе.

Ф

ормула изобретения

20

Параллельный сигнатурньпЧ анализатор, содержащий группу сумматоров по модулю два, регистр, RS-триггер и элемент И, причем входы Пуск и Останов анализатора подключены соответственно к S- и R-входам RS- 5 триггера,выход которого соединен с первым входом элемента И, второй вход которого является синхровходом анализатора, выход элемента И соединен с входом записи регистра, инфор- 0 мационные входы сумматоров по модулю два группы образуют группу информационных входов анализатора, группы информационных входов сумматоров по модулю два группы соединены с выхо- 5 дами регистра в соответствии с видом образующего полинома, группа выходов регистра является группой информационных выходов анализатора, отличающийся тем, что, с

- aiui4 inv;n тем. что. с

0 Целью повьшения достоверности контроля при произвольном количестве информационных входов, анализатор содержит дешифратор и группу коммутаторов, первые группы информационных

входов которых соединены с группой выходов регистра, вторые группы информационных входов коммутаторов соединены с группой выходов сумматоров по модулю два группы, группы коммутаторов объединены и подключены к группе информационных входов регистра, управлякяцие входы коммутаторов подключены к соответствующим выходам дешифратора, группа

,Г- ГТ- --«ff «- vj-j J 1 k TllllO.

хокоз которого является группой вхо

дов задания числа используемых информационных входов анализатора.

P

M.

l

M

fo

N

16 i-5B

Л

H-M

fi

M

H-H

M-/

n

fi

N-1

N

N

11

45

14

I 1-5 В

Фиг. 2

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1416997A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Сигнатурный анализатор с перестраиваемой структурой | 1983 |

|

SU1120334A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Устройство для контроля цифровых узлов | 1988 |

|

SU1695310A1 |

| Многоканальный сигнатурный анализатор для микропроцессорной системы | 1986 |

|

SU1374226A1 |

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей в многоразрядных цифровых схемах методом сигнатурного анализа. Целью изобретения является повышение достоверности контроля при произвольном количестве информационных входов. Параллельный сигнатурный анализатор содержит группу сумматоров по модулю два , блок 2 параллельного сдвига, RS-триггер 3 и элемент И4. Блок 2 параллельного сдвига, в свою очередь, содержит регистр, группу коммутаторов и дешифратор. Сущность изобретения заключается в том, что с помощью дешифратора и коммутатора осуществляется реконфигурация структуры анализатора в зависимости от количества требуемых информационных входов. Таким образом, при контроле мноноразрядйых цифровых схем в анализаторе отсутствуют неиспользуемые информационные входы, результатом чего является повышение достоверности контроля. 3 ил. а (С (Л

| Сигнатурный анализатор | 1983 |

|

SU1180896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ярмолис В.Н., Демиденко С.Н | |||

| Генерирование и применение псевдослучайных сигналов в системах испытаний и контроля | |||

| Минск: Наука и техника, 1986, с | |||

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

Авторы

Даты

1989-01-15—Публикация

1986-12-16—Подача