канала. Целью изобретения является расширение функциональных возможнос- ;тей за счет изменения длительности времени ожидания микропроцессора. Поставленная цель достигается за

Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве устройства управления.

Целью изобретения является расши- рение функциональных возможностей за счет изменения длительности времени ожидания микропроцессора.

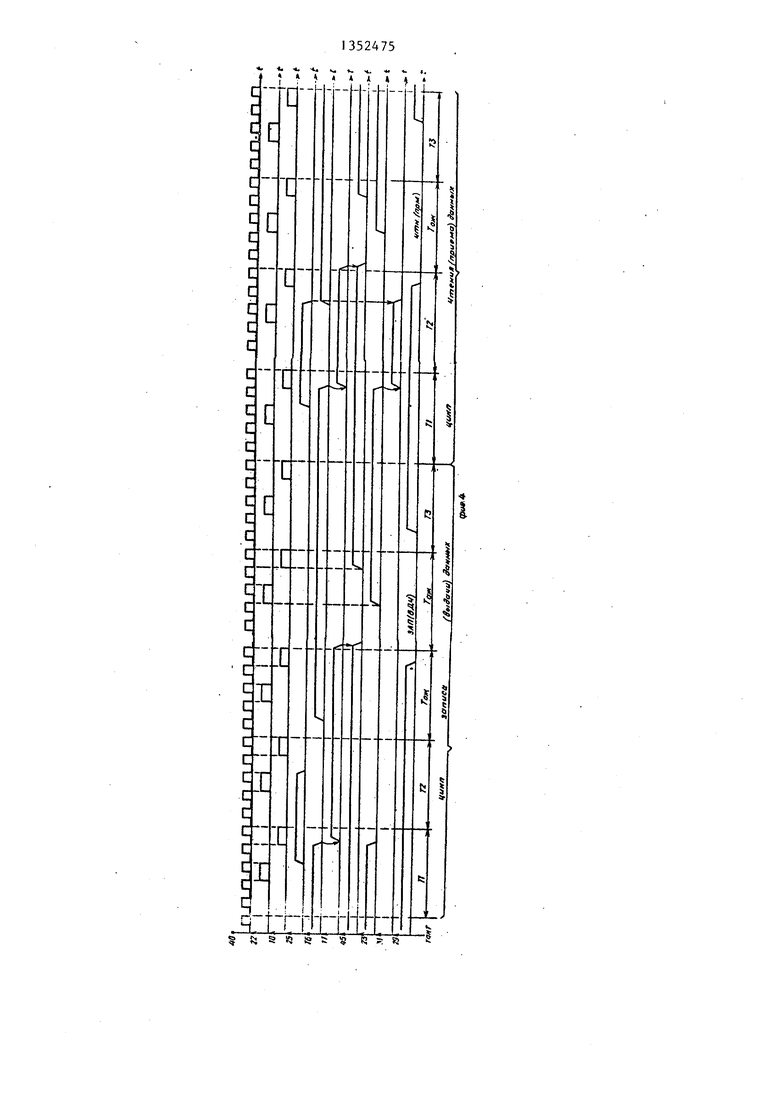

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функцио нальная схема блока синхронизации; на фиг.З - временная диаграмма функционирования блока синхронизации; на фиг.4 - временная диаграмма функционирования устройства; на фиг.5 - схема коммутатора; на фиг.6-8 - схема мажоритарного элемента.

Устройство содержит первый 1.1, второй 1.2 и третий 1.3 каналы, имею щи.е идентичную структуру, включающую регистр 2, счетчик 3, триггеры 4-7 блок В синхронизации, коммутатор 9, дешифратор 10, мажоритарный элемент 11, элементы И 12 - 14, элементы И-НЕ 15, 16, элементы ИЛИ-НЕ 17, выходы 18-23 блока 8, группу 24 входа задания интервала ожидания, управляющие входы 25, 27 - 32 каждого канала, элемент НЕ 26, вхоДы 33, 34 первой группы 35 входов разрешения ожидания канала, входы 36, 37 второй группы 38 разрешения ожидания канала тактовые входы 39 канала, выходы 40, 41 группы тактовых выходов канала, выходы 42, 43 группы 44 выходов разрешения ожидания канала, выход 45 триггера 7, входы 46 задания интервала ожидания канала, группу 47 управляющих входов канала, выход 48 окон- чания ожидания устройства, группу 49 выходов готовности микропроцессора устройства, группу 50 тактовых выходов каналов, группу 51 выходов разрешения ожидания канала.

счет введения регистра 2, элемента И 13, элементов И-НЕ 15, 16, блока 8 синхронизации, дешифратора 10, коммутатора 9. 8 ил.

5

0 5

5

. Блок 8 синхронизации содержит регистр 52 сдвига, мажоритарные элементы 53, 54, элемент И-НЕ 55, элемент НЕ-ИЛИ 56, элемент НЕ 57, кварцевый резонатор 58, резисторы 59, 60, тактовые входы 61, 62.

Коммутатор 9 содержит: селекто р 63, генератор 64 логической единицы.

Мажоритарный элемент 11 содержит мажоритарный элемент 65, селектор 66.

На фиг.З, 4 обозначение осей ординат соответствует нумерации элементов и выходов, используемой на фиг.1 и 2..

На фиг.4 приведен пример временной диаграммы функционирования устройства в режимах (циклах) записи (выдачи) и чтения (приема) данных без задания дополнительных тактов ожидания (два такта ожидания в режиме записи (выдачи) и один такт в режиме чтения (приема), т.к. при необходимости более длительного ожидания устройство функционирует аналогично, но с большим числом тактов ожидания. Через Т1, Т2, ТЗ и Т,. обозначены такты работы микропроцессора.

Рассмотрим функционирование устройства.

Вначале все элементы памяти находятся в нулевом состоянии. При включении устройства сигналом с входа 30 сбрасываются регистр 2 и триггер 6 и блок 8 синхронизации начинает формирование тактовых импульсов в соответствии с временной диаграммой, приведенной на фиг.З.

Запись интервала ожидания в регистр 2 осуществляется в цикле выдачи (фиг.4) по сигналу с входа 27 при наличии сигнала с выхода мажоритарного элемента 11 по окончании интервала времени дополнительного ожидания. Если в регистре 2 записан код 0000, то это соответствует вьшолнению обмена без дополнительного интервала ожидания (фиг.4).

При отсутствии сигнала на входе 28 канала код, записанный в регистр 2, через коммутатор 9 поступает на информационные входы счетчика 3. Если же сигнал на входе 28 канала присутствует, то на выходах коммутатора формируется код, соответствующий максимальной длительности интервала ожи- Дания.

Управление занесением кода в счетчик 3 осуществляется по импульсу низкого уровня с прямого выхода триггера 6, передний фронт которого формирует- ся по сигналу с выхода элемента И 12, срабатывающего при наличии сигналов с входа 25 и выхода 18 блока 8, синхронизании, а задний фронт - при

установке микропроцессором сигнала на входе 29 (триггер 6 устанавливается в единичное состояние).

После записи кода в счетчик 3 сигнал на его выходе переполнения принимает нулевое значение. При этом открывается элемент И 12, вследствие чего перекрывающиеся тактовые импульсы с выходов 18 и 40 блока 8 синхронизации начинают поступать на счетный вход счетчика 3.

За один такт микропроцессора (фиг.4) на счетный вход счетчика 3 поступает один импульс с выхода эле- .мента И 12.

Период ожидания продолжается до тех пор, пока по очередному импульсу с выхода элемента И 12 не произойдет переполнение счетчика 3. В этом случае элемент И 12 закрывается и подача импульсов на счетчик 3 прекращает ся.

Сигнал переноса в качестве сигнала - признака окончания ожидания дан ного канала поступает на выход 42 канала и далее через группу 51 выхо- дов на соответствующие входы соседних каналов. Одновременно сигнал переноса поступает на вход Д мажоритарного элемента 11. Со входов 33 и 36 канала на входы Д2 и ДЗ мажоритар- ного элемента 11 поступают аналогичные сигналы от соседних каналов.

В мажоритарном режиме работы при отсутствии сигнала с входа 32 канала на элементе 11 происходит мажоритарная обработка указанных сигналов. В режиме независимой работы под действием сигнала с входа 32 на выходы элемента 11 транслируется сигнал пе

реполнения канала.

только счетчика 3 своего

5 0

30

35

20

40

. 45 0

Сигнал низкого уровня с инверсного выхода элемента 11 поступает на информационный вход триггера 5, подготавливая его к установке в нулевое состояние, в которое триггер 5 устанавливается по TaKTOBONry импульсу с выхода 22 блока 8 синхронизации.

. Одновременно сигнал переполнения с прямого выхода элемента II поступает на синхровход триггера 1 который под его действием устанавливается в нулевое состояние (фиг.5). Сигнал с выхода 45 триггера 7 используется в системе для фиксации приема данных.

С приходом первого после описанного момента времени импульса с выхода 18 блока 8 триггер 7 устанавливается в единичное состояние.

Сигнал начала чтения кода команды с входа 31 канала стробируется сигна- 25 лом с инверсного выхода триггера 6, который устанавливается в нулевое состояние при возбуждении входа 25 канала и выхода 18 блока 8, и поступает на третий вход дешифратора 10 и на выход 44 канала для передачи на соответствующие входы соседних каналов.

Депшфратор 10 срабатывает по первому выходу, если только свой канал установил признак чтения кода команды по входу 31. В этом случае триггер 4 по единичному входу устанавли-- вается в .единичное состояние. Если признак чтения кода команды установлен хотя бы одним из соседних каналов по входам 34 и (или) 37, то дешифратор 10 по тактовому импульсу с выхода 22 генератора 8 срабатьшает по второму выходу и устанавливает триггер 4 по синхровходу в нулевое состояние.

Триггер 5 всегда устанавливается в единичное состояние по единичным выходным сигналам элемента И I2.

Если триггер 4 был установлен в нулевое состояние сигналом второго выхода дешифратора 10, то на единичном входе триггера 5 до прихода очередного импульса с выхода элемента И 12 сохраняется сигнал высокого уровня. Поэтому триггер 5 сигналом с инверсного выхода элемента 11 устанавливается в нулевое состояние по синхроимпульсу с выхода 22 генерато-г

5

51

pa 8 и фор трует тем самым сигнал вьг сокого уровня на выходе из канала.

Если же триггер 4 был установлен в единичное состояние сигналом с пер вого выхода дешифратора 10 в результате установки признака начала чтения кода команды с входа 31 только своим каналом, то с единичного выхода этого триггера через элемент ИЛИ-НК 17 выдается сигнал, блокирующий установку триггера 5 в нулевое состояние по входу Д1, и триггер 5 останется в единичном состоянии.

По окончании очередного периода ожидания устройство функционирует аналогично описанному выше.

Формула изобретения

Трехканальное устройство для управления синхронизацией микропроцессорной системы, содержащее в каждом канале два элемента И, четьфе тригге ра, мажоритарный элемент, счетчик, элемент ИЛИ-НЕ, элемент НЕ, отличающееся тем, что, с целью расширения функциональных возможностей за счет изменения длительности времени ожидания микропроцессора, в каждый канал устройства введен регистр, коммутатор, два элемента И-НЕ блок синхронизации, дешифратор- и эле мент И, причем группа входов задания интервала ожидания устройства соединена с входами задания интервала ожи Дания каждого канала устройства, группа управляющих входов каждого ка нала устройства является группой вхо дов устройства для подключения к управляющей шине микропроцессорной сие темы, выходы окончания ожидания каждого канала являются выходами окончания ожидания устройства, группа тактовых входов каждого канала соеди нена соответственно с первой и второй группами тактовых входов остальных каналов, группа выходов разрешения ожидания каждого канала соединена соответственно с первой и второй группами входов разрешения ожидания остальных каналов, причем в каждом канапе первьй вход группы управл.яю- П1их входов канала соединен с первым входом первого элемента И, второй вход группы управляющих входов канала соединен с первым входом первого элемента И-НЕ, третий вход группы управляющих входов канала соединен с управляющим входом коммутатора.

20

25

52475 .6

четвертый вход группы управляющих входов канала соединен с единичным входом первого триггера, нулевой вход которого является пятым управляющим 5 входом группы канала и соединен с входом сброса регистра, шестой управляющий вход канала соединен с первым входом второго элемента И, седьмой управляющий вход группы канала соединен с управляющим входом мажоритарного элемента, с первым информационным входом дешифратора, с нулевым входом второго триггера и с входом

начальной установки блока синхрониза- ции, выход первого элемента И-НЕ соединен с входом разрешения записи регистра, группа информационных входов которого является группой входов задания интервала ожидания канала, группа выходов регистра соединена с группой информационных входов коммутатора, выходы коммутатора соединены с информационными входами счетчика, выход переполнения которого соединен с входом элемента НЕ и с первым информационным входом мажоритарного элемента, второй и третий информационные входы которого являются соответственно первыми входами первой и второй групп входов разрешения ожидания канала, прямой выход мажоритарного элемента соединен с вторым входом первого элемента И-НЕ и с синхровхо- дом третьего триггера, выход которого является выходом окончания ожидания канала, инверсный выход мажоритарного элемента соединен с информационным входом четвертого триггера, единичный вход которого соединен с

40 выходом элемента ИЛИ-НЕ, первый вход которого соединен с выходом первого элемента И и с синхровходом первого триггера, информационный вход которого соединен с информационным входом второго триггера, с информационным входом третьего триггера и с шиной нулевого потенциала устройства, первый выход блока синхронизации соединен с первым входом второго элемента 50 И-НЕ, с п ервым входом третьего элемента И, с вторым входом первого элемента И и является первым выходом группы тактовых выходов канала, второй выход блока синхронизации соединен с вторьм входом второго элемента И-НЕ, с вторым входом третьего элемента И и является вторым выходом группы тактовых выходов канала, третий и четвертьй выходы блока синхро30

35

45

55

низации являются первым и вторым вы-, ходами устройства для подключения к входам готовности микропроцессора, выход ч-етвертого триггера является третьим выходом устройства для подключения к входу готовности микропроцессора, инверсный выход первого триггера соединен с вторым входом второго элемента И, выход которого соединен с вторым информационным входом дешифратора и является первым выходом группы выходов разрешения ожидания канала устройства, пятый выход блока синхронизации соединен с синхровходом четвертого триггера и с

третьим информационным входом дешифратора, четвертый и пятый информационные входы которого являются соответственно первыми входами первой и второй групп входов разрешения ожидания канала, первый выход дешифратора соединен с единичным входом второго триггера, синхровход которого соединен с вторым выходом дешифратора, выход второго триггера соединен с вторым входом элемента ИЛИ-НЕ, выход которого соединен с единичным входом третьего триггера, выход третьего

элемента И соединен со счетным входом счетчика.

фиг. 2

.Ч. {:;aKJ :S

Составитель Н. Торопова Редактор М. Циткина Техред М.Ходанич Корректор С. Шекмар

Заказ 5566/48

Тираж 671Подписное

ВНИИПИ Государствениого комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская- н,аб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

наСТЗ

фиг. S

фиё.в

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в качестве устройства управления. Отличительной особенностью устройства является то, что оно позволяет варьировать длительность интервала времени ожидания при взаимодействии микропроцессора и внешнего устройства, а также формировать синхронный на все каналы сигнал готовности микропроцессора либо сигнал готовности только для одного W 3 (Л оо СП Фиг

| Ноффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

| Многоканальное устройство для управления пуском и рестартом при сбоях микропроцессорной системы | 1985 |

|

SU1247869A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1987-11-15—Публикация

1985-02-22—Подача