Изобретение относится к запоминающим устройствам и может быть использовано при создании больших интегральных схем на МДП-транзисторах, в частности запоминающих устройств динамического типа.

Цель изобретения - повышение быстродействия и надежности срабатывания адресного формирователя.

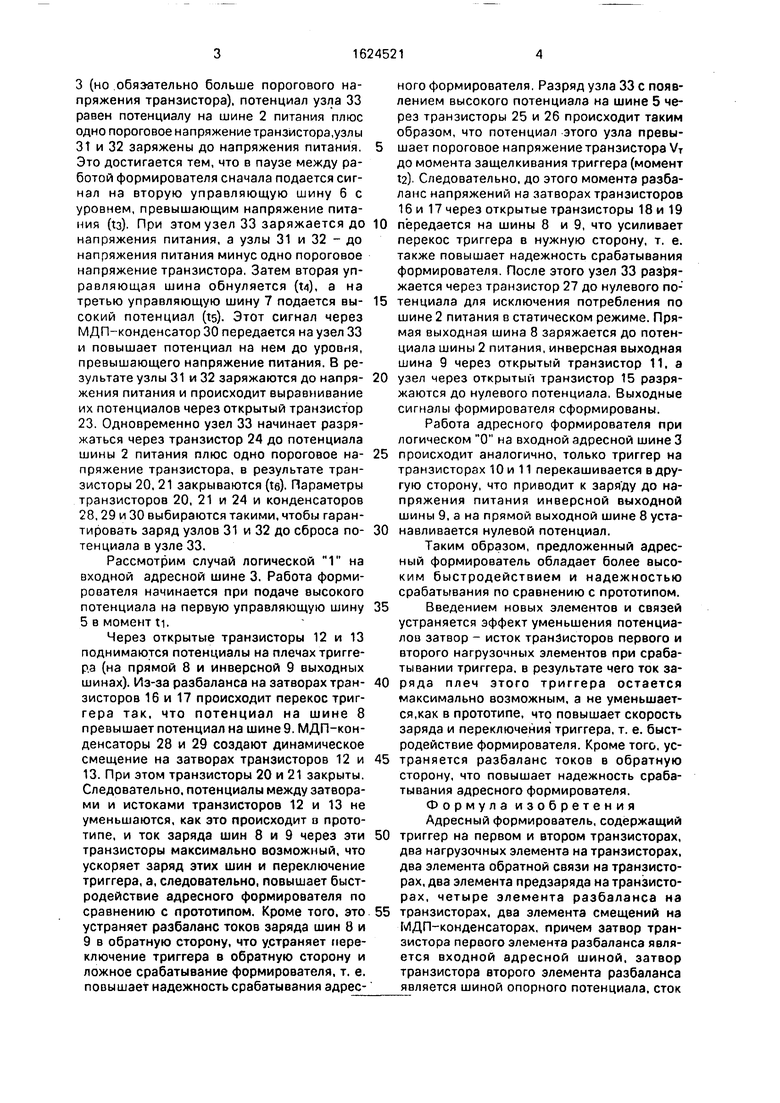

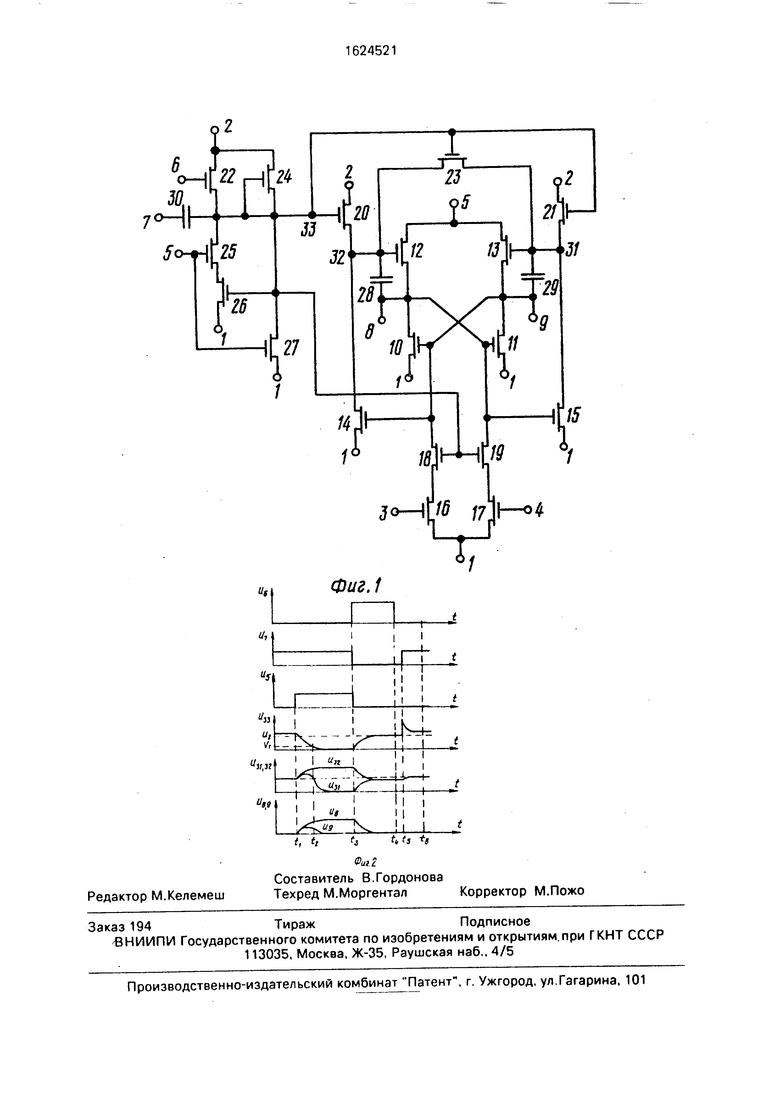

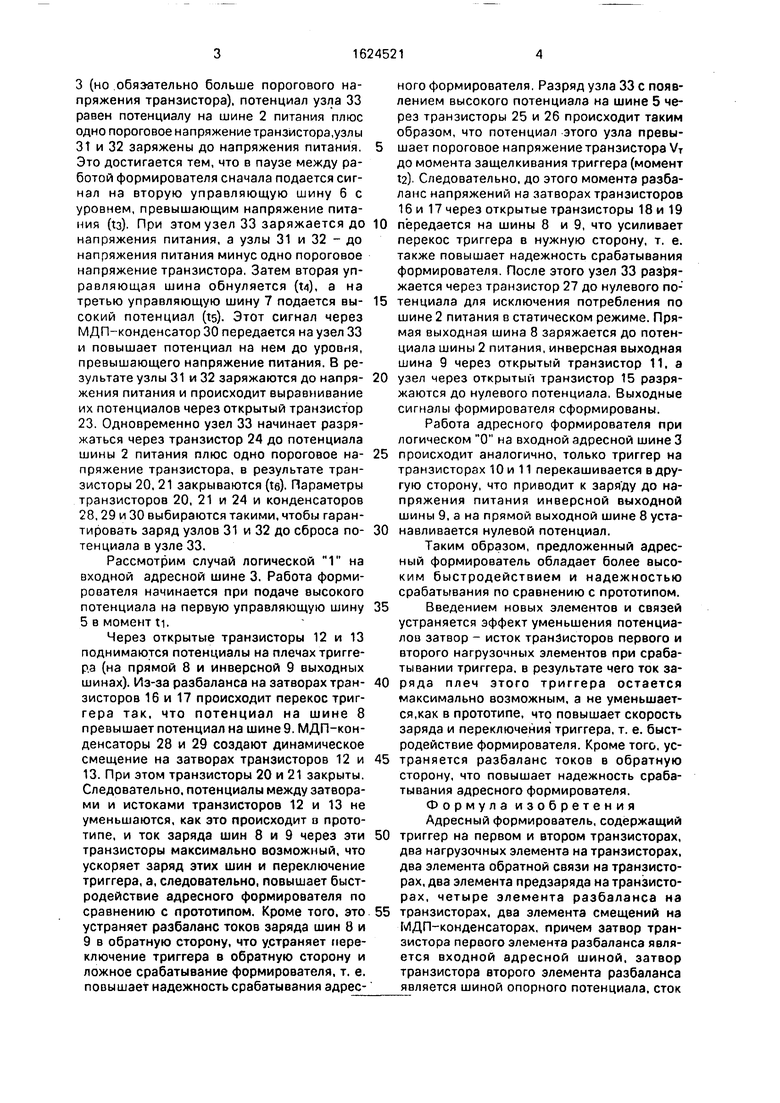

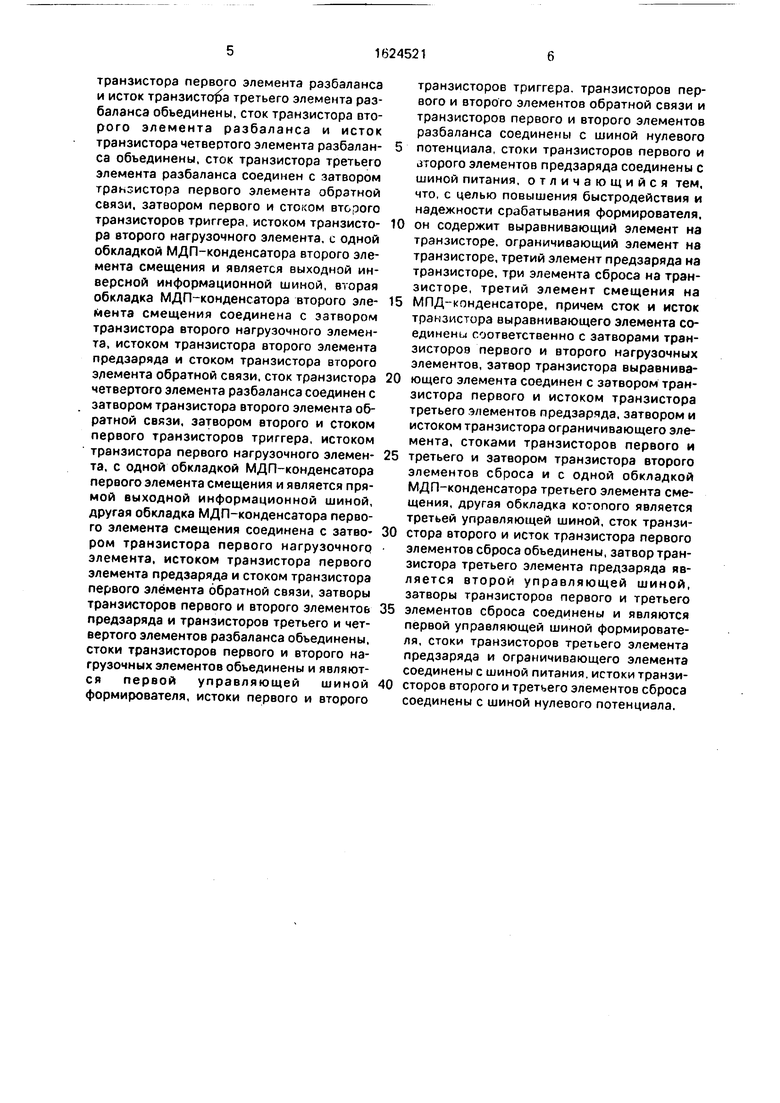

На фиг. 1 представлена принципиальная схема предложенного адресного формирователя; на фиг. 2 - временная диаграмма его работы.

Адресный формирователь содержит шину 1 нулевого потенциала, шину 2 питания, входную адресную шину 3, шину 4 опорного потенциала, первую 5, вторую б и третью 7 управляющие шины, прямую 8 и инверсную 9 выходные шины, триггер на первом 10 и втором 11 транзисторах, первый 12 и второй 13 нагрузочные элементы на транзисторах.

первый 14 и второй 15 элементы обратной связи на транзисторах, первый 16, второй 17, третий 18 и четвертый 19 элементы разбаланса на транзисторах, первый 20, второй 21 и третий 22 элементы предзаряда на транзисторах, выравнивающий элемент 23 на транзисторе, ограничивающий элемент 24 на транзисторе, первый 25, второй 26 и третий 27 элементы сброса на транзисторах, первый 28, второй 29 и третий 30 элементы счмешения на МДП-конденсаторах, узлы 31, 32 и 33.

Адресный формирователь работает следующим образом.

В исходном состоянии (момент ti на фиг. 2) на первой 5 и второй 6 управляющих шинах - нулевой потенциал, на третьей управляющей шине 7 - высокий потенциал, на шине опорного потенциала 4 - напряжение, ровное полусумме логических уровней О и 1, подаваемых на входную адресную шину

О

ю

СП

ю

3 (но обязательно больше порогового напряжения транзистора), потенциал узла 33 равен потенциалу на шине 2 питания плюс одно пороговое напряжение транзистора.узлы 31 и 32 заряжены до напряжения питания. Это достигается тем, что в паузе между работой формирователя сначала подается сигнал на вторую управляющую шину б с уровнем, превышающим напряжение питания (гз). При этом узел 33 заряжается до напряжения питания, а узлы 31 и 32 - до напряжения питания минус одно пороговое напряжение транзистора, Затем вторая управляющая шина обнуляется (м), а на третью управляющую шину 7 подается высокий потенциал (ts). Этот сигнал через МДП-конденсатор 30 передается на узел 33 и повышает потенциал на нем до уровня, превышающего напряжение питания. В результате узлы 31 и 32 заряжаются до напряжения питания и происходит выравнивание их потенциалов через открытый транзистор 23. Одновременно узел 33 начинает разряжаться через транзистор 24 до потенциала шины 2 питания плюс одно пороговое напряжение транзистора, в результате транзисторы 20, 21 закрываются (te). Параметры транзисторов 20, 21 и 24 и конденсаторов 28,29 и 30 выбираются такими, чтобы гарантировать заряд узлов 31 и 32 до сброса потенциала в узле 33.

Рассмотрим случай логической 1 на входной адресной шине 3. Работа формирователя начинается при подаче высокого потенциала на первую управляющую шину 5 в момент ti.

Через открытые транзисторы 12 и 13 поднимаются потенциалы на плечах триггера (на прямой 8 и инверсной 9 выходных шинах). Из-за разбаланса на затворах транзисторов 16 и 17 происходит перекос триггера так, что потенциал на шине 8 превышает потенциал на шине 9. МДП-кон- денсаторы 28 и 29 создают динамическое смещение на затворах транзисторов 12 и 13. При этом транзисторы 20 и 21 закрыты. Следовательно, потенциалы между затворами и истоками транзисторов 12 и 13 не уменьшаются, как это происходит и прототипе, и ток заряда шин 8 и 9 через эти транзисторы максимально возможный, что ускоряет заряд этих шин и переключение триггера, а, следовательно, повышает быстродействие адресного формирователя по сравнению с прототипом. Кроме того, это устраняет разбаланс токов заряда шин 8 и 9 в обратную сторону, что устраняет переключение триггера в обратную сторону и ложное срабатывание формирователя, т. е. повышает надежность срабатывания адресного формирователя. Разряд узла 33 с появлением высокого потенциала на шине 5 через транзисторы 25 и 26 происходит таким образом, что потенциал этого узла превышает пороговое напряжение транзистора VT до момента защелкивания триггера (момент t2). Следовательно, до этого момента разбаланс напряжений на затворах транзисторов 16 и 17 через открытые транзисторы 18 и 19

0 передается на шины 8 и 9, что усиливает перекос триггера в нужную сторону, т. е. также повышает надежность срабатывания формирователя. После этого узел 33 разряжается через транзистор 27 до нулевого по5 тенциала для исключения потребления по шине 2 питания в статическом режиме. Прямая выходная шина 8 заряжается до потенциала шины 2 питания, инверсная выходная шина 9 через открытый транзистор 11, а

0 узел через открытый транзистор 15 разряжаются до нулевого потенциала. Выходные сигналы формирователя сформированы.

Работа адресного формирователя при логическом О на входной адресной шине 3

5 происходит аналогично, только триггер на транзисторах 10 и 11 перекашивается в другую сторону, что приводит к заряду до напряжения питания инверсной выходной шины 9, а на прямой выходной шине 8 уста0 навливается нулевой потенциал.

Таким образом, предложенный адресный формирователь обладает более высоким быстродействием и надежностью срабатывания по сравнению с прототипом.

5Введением новых элементов и связей

устраняется эффект уменьшения потенциалов затвор - исток транзисторов первого и второго нагрузочных элементов при срабатывании триггера, в результате чего ток за0 ряда плеч этого триггера остается максимально возможным, а не уменьшается,как в прототипе, что повышает скорость заряда и переключения триггера, т. е. быстродействие формирователя. Кроме того, ус5 траняется разбаланс токов в обратную сторону, что повышает надежность срабатывания адресного формирователя. Формула изобретения Адресный формирователь, содержащий

0 триггер на первом и втором транзисторах, два нагрузочных элемента на транзисторах, два элемента обратной связи на транзисторах, два элемента предзаряда на транзисторах, четыре элемента разбаланса на

5 транзисторах, два элемента смещений на МДП-конденсаторах, причем затвор транзистора первого элемента разбаланса является входной адресной шиной, затвор транзистора второго элемента разбаланса является шиной опорного потенциала, сток

транзистора первого элемента разбаланса и исток транзистора третьего элемента разбаланса объединены, сток транзистора второго элемента разбаланса и исток транзистора четвертого элемента разбаланса объединены, сток транзистора третьего элемента разбаланса соединен с затвором транзистора первого элемента обратной связи, затвором первого и стоком второго транзисторов триггера, истоком транзистора второго нагрузочного элемента, с одной обкладкой МДП-конденсатора второго элемента смещения и является выходной инверсной информационной шиной, вторая обкладка МДП-конденсатора второго элемента смещения соединена с затвором транзистора второго нагрузочного элемента, истоком транзистора второго элемента предзаряда и стоком транзистора второго элемента обратной связи, сток транзистора четвертого элемента разбаланса соединен с затвором транзистора второго элемента обратной связи, затвором второго и стоком первого транзисторов триггера, истоком транзистора первого нагрузочного элемента, с одной обкладкой МДП-конденсатора первого элемента смещения и является прямой выходной информационной шиной, другая обкладка МДП-конденсатора первого элемента смещения соединена с затвором транзистора первого нагрузочного элемента, истоком транзистора первого элемента предзаряда и стоком транзистора первого элемента обратной связи, затворы транзисторов первого и второго элементов предзаряда и транзисторов третьего и четвертого элементов разбаланса объединены, стоки транзисторов первого и второго нагрузочных элементов объединены и являются первой управляющей шиной формирователя, истоки первого и второго

транзисторов триггера, транзисторов первого и второго элементов обратной связи и транзисторов первого и второго элементов разбаланса соединены с шиной нулевого 5 потенциала, стоки транзисторов первого и аторого элементов предзэряда соединены с шиной питания, отличающийся тем, что, с целью повышения быстродействия и надежности срабатывания формирователя.

0 он содержит выравнивающий элемент на транзисторе, ограничивающий элемент на транзисторе, третий элемент предзаряда на транзисторе, три элемента сброса на транзисторе, третий элемент смещения на

5 МПД-конденсаторе, причем сток и исток транзистора выравнивающего элемента соединены соответственно с затворами транзисторов первого и второго нагрузочных элементов, затвор транзистора выравнива0 ющего элемента соединен с затвором транзистора первого и истоком транзистора третьего элементов предзаряда, затвором и истоком транзистора ограничивающего элемента, стоками транзисторов первого и

5 третьего и затвором транзистора второго элементов сброса и с одной обкладкой МДП-конденсатора третьего элемента смещения, другая обкладка котопого является третьей управляющей шиной, сток транзи0 стора второго и исток транзистора первого элементов сброса объединены, затвор транзистора третьего элемента предзаряда является второй управляющей шиной, затворы транзисторов первого и третьего

5 элементов сброса соединены и являются первой управляющей шиной формирователя, стоки транзисторов третьего элемента предзаряда и ограничивающего элемента соединены с шиной питания, истоки транзи0 сторов второго и третьего элементов сброса соединены с шиной нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Дешифратор | 1989 |

|

SU1644222A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

Изобретение относится к запоминающим устройствам и может быть использовано при создании больших интегральных схем на МДП-транзисторах. Цель изобретения - повышение быстродействия и надеж- ности срабатывания адресного формирователя. Поставленная цель достигается введением выравнивающего элемента, ограничивающего элемента, третьего элемента предзаряда, трех элементов сброса, третьего элемента смещения. Это позволяет устранить эффект уменьшения потенциалов затвор - исток транзисторов первого и второго нагрузочных элементов при срабатывании триггера, в результатече- го ток заряда и переключения триггера остается максимально возможным, а не уменьшается, что повышает скорость заряда и переключения триггера, т. е. быстродействие формирователя. Кроме того, устраняется разбаланс токов в обратную сторону, что повышает надежность срабатывания формирователя. 2 ил. сл С

jo-Hf/0 /7JI-°4

| Электроника | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-01-30—Публикация

1988-07-12—Подача