СО

Од

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для ввода информации в системы регистрации и обработки информации..

Цель изобретения - повьшение производительности ЭВМ за счет уменьшения избыточности передаваемой информации .10

В данном устройстве в процессе выполнения текущего опроса информационных каналов производится подсчет существенных выборок (отличающихся от выборок предьщущего цикла опроса) с 15 учетом их идентификаторов (номеров каналов). После обработки данных всех информационных каналов производится выбор режима вьщачи выходной информации, а именно: выдача существенных 20 выборок данного цикла с их идентифи- . каторами или вьщача выборок всех информационных каналов данного цикла без идентификаторов. Выбор режима выУстройство имеет два режима работы, а именно-: запись информации с проведением предварительного сокращения избыточности и чтение информагщи. Перед проведением каждого цикла записи в блоке 1 памяти .по адресам, однозначно соответствующим идентификаторам информационных каналов, хранятся данные их предыдущего цикла опроса.

В режиме записи, который определяется высоким уровнем сигнала на выходе триггера 20, т.е. на выходе 16 устройства, запис ьшаемые данные по входу 3 устройства поступают на информационные входы блока 1 памяти и один из входов блока 5 сравнения. На другие входы блока 5 сравнения подаются данные информационного канала предьщущего цикла опроса, считываемые из блока 1 памяти. Через время, достаточное для срабатьтания блока 5 сравнения, на вход 13 устройства посдачи производится по минимуму объема 25 тупает сигнал сопровождения принимаевыходной информации и осуществляется с учетом разрядности информационной части сообщения и разрядности кода идентификатора, которая определяется количеством идентификаторов.

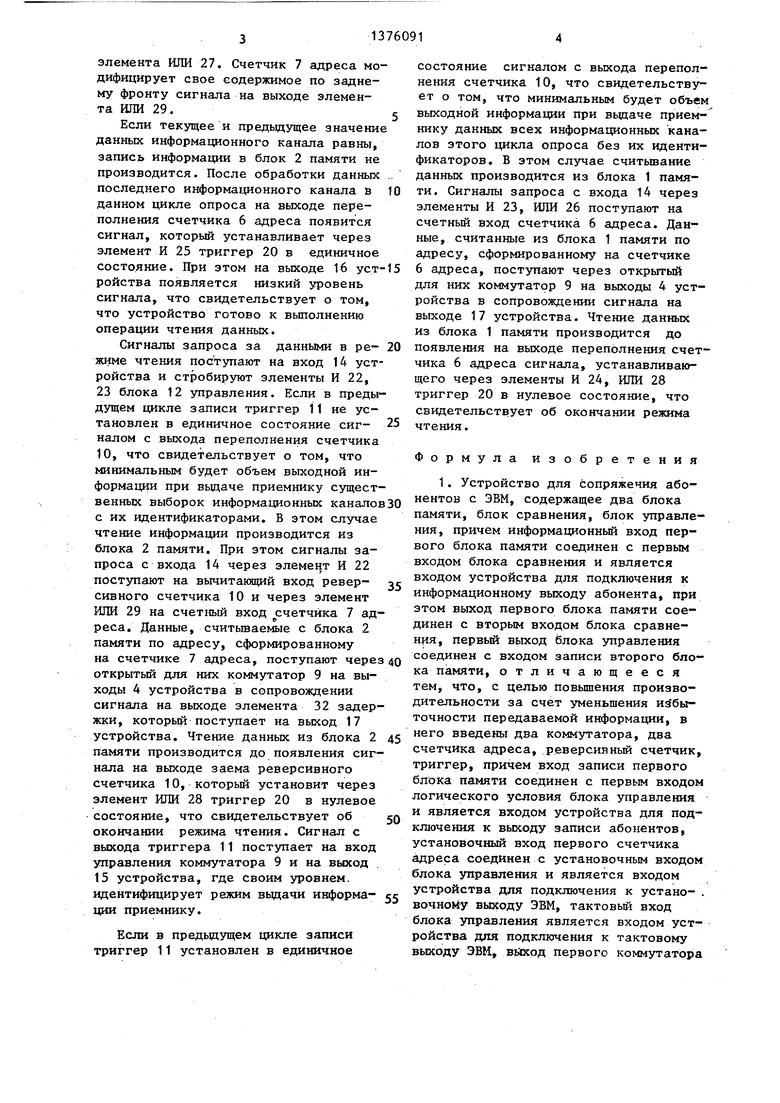

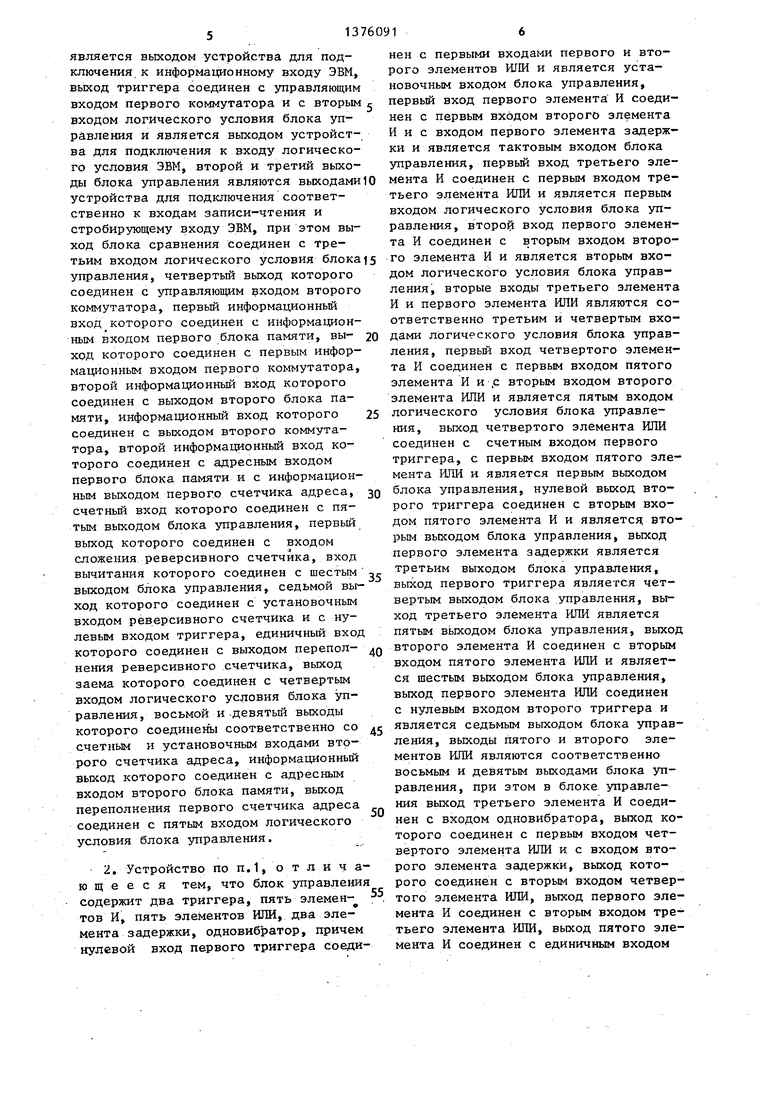

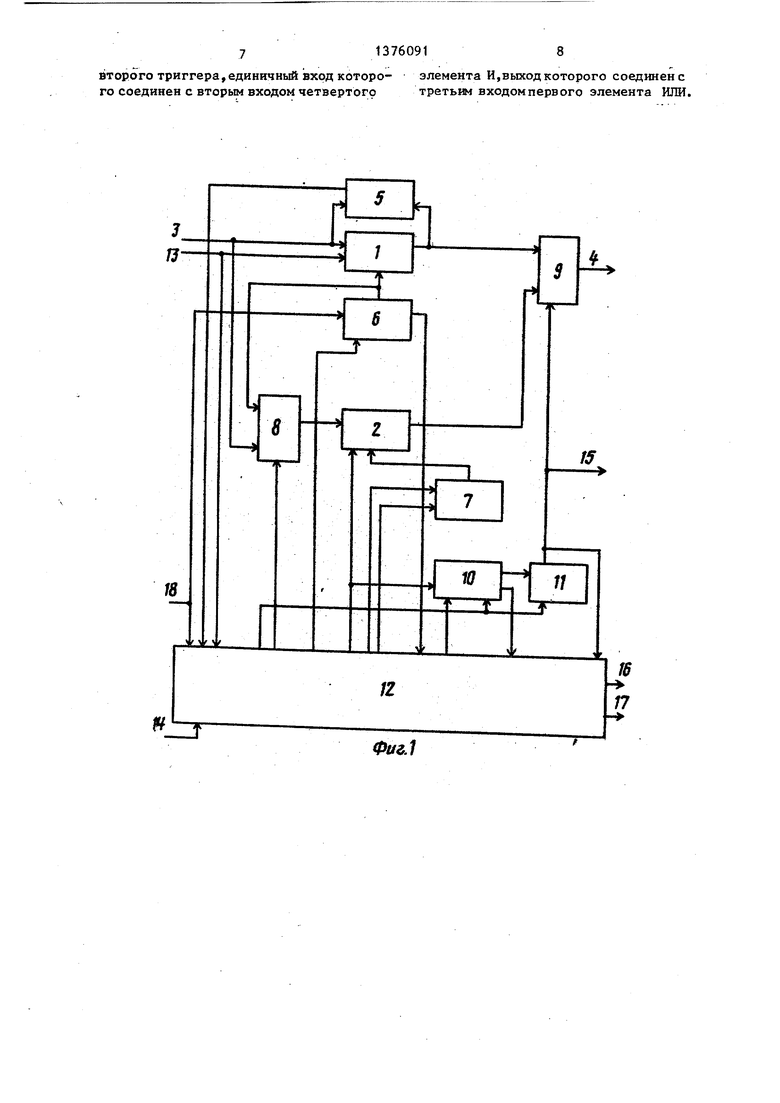

На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема блока управления.

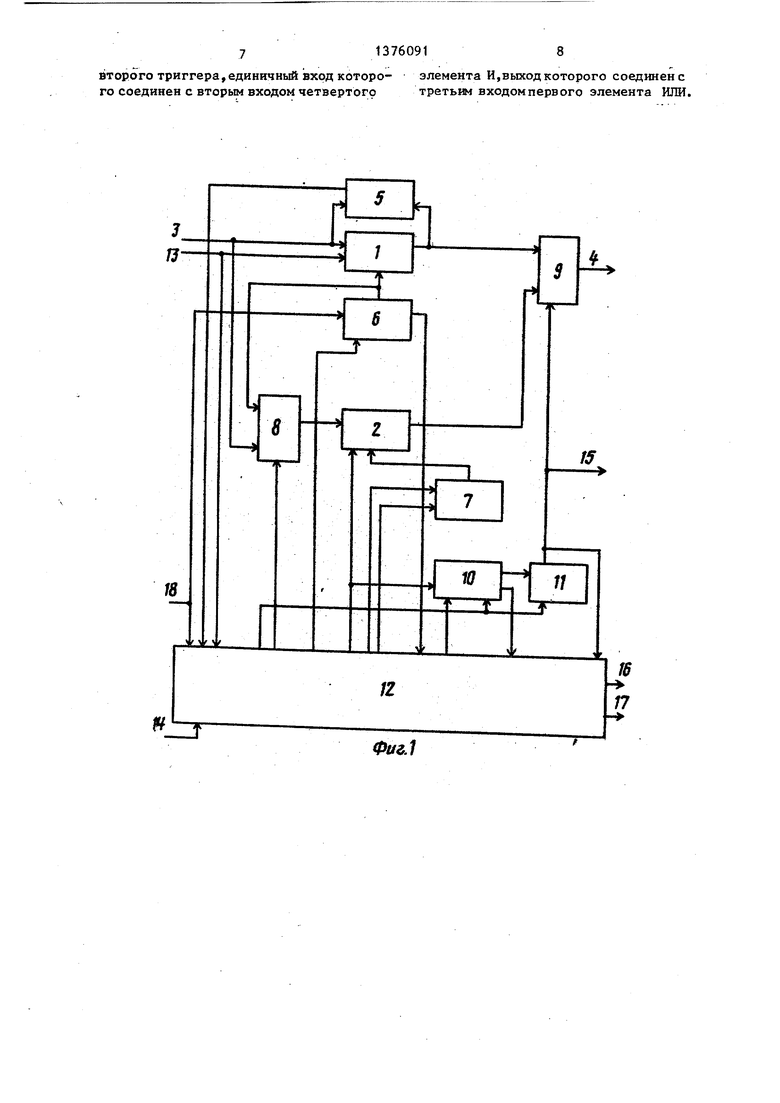

На фиг.2 приведена одна из возможных реализаций блока управления, ко- торая подразумевает, что разрядность кода идентификатора информационного канала не превышает разрядности ин- -формационной части сообщения

Устройство содержит блоки 1 и 2 памяти, информаи юнные входы 3 и выходы 4, блок 5 сравнения, счетчики 6 и 7 адреса, коммутаторы 8 и 9, реверсивный счетчик 10, триггер 11, блок 12 управления, входы 13, 14 управле- ния, выходы 15-17 управления, вход 18 установки.

Блок 12 управления содержит триггеры 19 и 20, элементы И 21-25, элементы ИЛИ 26-29, элемент ИЛИ 30, элементы 31 и 32 задержки, одновибра - тор 33.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 18 триггеры 11, 19 20 и счетчики 6, 7, 10 устанавливаются в нулевое -состояние.

Устройство имеет два режима работы, а именно-: запись информации с проведением предварительного сокращения избыточности и чтение информагщи. Перед проведением каждого цикла записи в блоке 1 памяти .по адресам, однозначно соответствующим идентификаторам информационных каналов, хранятся данные их предыдущего цикла опроса.

В режиме записи, который определяется высоким уровнем сигнала на выходе триггера 20, т.е. на выходе 16 устройства, запис ьшаемые данные по входу 3 устройства поступают на информационные входы блока 1 памяти и один из входов блока 5 сравнения. На другие входы блока 5 сравнения подаются данные информационного канала предьщущего цикла опроса, считываемые из блока 1 памяти. Через время, достаточное для срабатьтания блока 5 сравнения, на вход 13 устройства посмых данных, который опрашивает элемент И 21 блока 12 управления и осуществляет запись данных с входа 3 устройства в блок 1 памяти по адресу сформированному на счетчике 6 адреса При неравенстве текущего и предЬщу- щего значений информационного канала на выходе блока 5 сравнения присутствует высокий уровень сигнала, и сигнал с входа 13 устройства через элемент И 21 поступает на вход од- новибратора 33, выходной сигнал которого через элемент ИЛИ 27 осуществляет запись в блок 2 памяти идентификатора данного канала (кода содержимого счетчика 6 адреса) через откры- тьш для него коммутатор 8. Запись в блок 2 памяти осуществляется по адресу, сформированному на счетчике 7 адреса. После записи в блок 2 памяти идентификатора, в него сигналом с выхода элемента 31 задержки записывается код нового значения информационного канала через открытый для него коммутатор 8. Управление коммутатором 8 осуществляется счетным триггером 19, который изменяет свое состояние на противоположное по заднему фронту сигнала на выходе элемента ИЛИ 27. Подсчет записанных в блок 2 памяти информационных слов осуществляется реверсивным счетчиком 10, который модифицирует свое содержимое по заднему фронту сигнала на выходе

элемента ИЛИ 27. Счетчик 7 адреса модифицирует свое содержимое по заднему фронту сигнала на выходе элемента ИЛИ 29.

Если текущее и предьщущее значение данных информационного канала равны, запись информации в блок 2 памяти не производится. После обработки данных последнего информационного канала в данном цикле опроса на выходе переполнения счетчика 6 адреса появится сигнал, который устанавливает через элемент И 25 триггер 20 в единичное состояние. При этом на выходе 16 устройства появляется низкий уровень сигнала, что свидетельствует о том, что устройство готово к выполнению операции чтения данньк.

Сигналы запроса за данными в ре- жиме чтения поступают на вход 14 устройства и стробируют элементы И 22, 23 блока 12 управления. Если в предыдущем цикле записи триггер 11 не установлен в единичное состояние сиг- налом с выхода переполнения счетчика 10, что свидетельствует о том, что минимальным будет объем выходной информации при вьщаче приемнику существенных выборок информационных каналов с их идентификаторами. В этом случае чтение информации производится из блока 2 памяти. При этом сигналы запроса с входа 14 через элемент И 22 поступают на вычитаняций вход ревер- сивного счетчика 10 и через элемент ИЛИ 29 на счетный вход счетчика 7 адР

реса. Данные, считьтаемые с блока 2 памяти по адресу, сформированному на счетчике 7 адреса, поступают через открытый для них коммутатор 9 на выходы 4 устройства в сопровождении сигнала на выходе элемента 32 задержки, который поступает на выход 17 устройства. Чтение данных из блока 2 памяти производится до появления сигнала на выходе заема реверсивного счетчика 10, который установит через элемент ИЛИ 28 триггер 20 в нулевое состояние, что свидетельствует об окончании режима чтения. Сигнал с выхода триггера 11 поступает на вход управления коммутатора 9 и на выход 15 устройства, где Своим уровнем, идентифицирует режим вьщачи информа- ции приемнику.

Если в предьщущем цикле записи триггер 11 установлен в единичное

состояние сигналом с выхода переполнения счетчика 10, что свидетельствует о том, что минимальным будет объем выходной информации при вьщаче приемнику данных всех информационных каналов этого цикла опроса без их идентификаторов. В этом случае считьтание данных производится из блока 1 памяти. Сигналы запроса с входа 14 через элементы И 23, ИЛИ 26 поступают на счетный вход счетчика б адреса. Данные, считанные из блока 1 памяти по адресу, сформированному на счетчике 6 адреса, поступают через открытый для них коммутатор 9 на выходы 4 устройства в сопровождении сигнала на выходе 17 устройства. Чтение данных из блока 1 памяти производится до появления на выходе переполнения счетчика 6 адреса сигнала, устанавливающего через элементы И 24, ИЛИ 28 триггер 20 в нулевое состояние, что свидетельствует об окончании режима чтения.

Формула изобретения

1. Устройство для сопряжения абонентов с ЭВМ, содержащее два блока памяти, блок сравнения, блок управления, причем информационный вход первого блока памяти соединен с первым входом блока сравнения и является входом устройства для подключения к информационному выходу абонента, при этом выход первого блока памяти соединен с вторым входом блока сравнения, первый выход блока управления соединен с входом записи второго блока памяти, отличающееся тем, что, с целью повышения производительности за счет уменьшения из бы- точности передаваемой информации, в него введены два коммутатора, два счетчика адреса, реверсивный счетчик, триггер, причем вход записи первого блока памяти соединен с первым входом логического условия блока управления и является входом устройства для подключения к выходу записи абонентов, установочный вход первого счетчика адреса соединен с установочным входом блока управления и является входом устройства для подключения к устано- ночному выходу ЭВМ, тактовьй вход блока управления является входом устройства для подключения к тактовому выходу ЭВМ, выход первого коммутатора

является выходом устройства для подключения к информационному входу ЭВМ, выход триггера соединен с управляющим входом первого коммутатора и с вторым входом логического условия блока управления и является выходом устройства для подключения к входу логического условия ЭВМ, второй и третий выходы блока управления являются выходами устройства для подключения соответственно к входам записи-чтения и стробирующему входу ЭВМ, при этом выход блока сравнения соединен с третьим входом логического условия блока управления, четвертый выход которого соединен с управляющим уходом второго коммутатора, первьй информационный вход которого соединен с информационным входом первого блока памяти, вы- ход которого соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом второго блока памяти, информационный вход которого соединен с выходом второго коммутатора, второй информационный вход которого соединен с адресным входом первого блока памяти и с информационным выходом первого счетчика адреса, счетньш вход которого соединен с пятым выходом блока управления, первый выход которого соединен с входом сложения реверсивного счетчика, вход вычитания которого соединен с шестым выходом блока управления, седьмой выход которого соединен с установочным входом рев.ерсивного счетчика и с ну- левьм входом триггера, единичный вход которого соединен с выходом перепол- нения реверсивного счетчика, выход заема которого соединен с четвертым входом логического условия блока управления, восьмой и .девятый выходы которого соединены соответственно со счетным и установочным входами второго счетчика адреса, информационный выход которого соединен с адресным входом второго блока памяти, выход переполнения первого счетчика адреса соединен с пятым входом логического условия блока управления.

2. Устройство по П.1, о т л и ч а- ю щ е е с я тем, что блок управления содержит два триггера, пять элемен- тов И, пять элементов ИЛИ, два элемента задержки, одновибратор, причем нулевой вход первого триггера соединен с первыми входами первого и второго элементов ШШ и является установочным входом блока управления, первый вход первого элемента И соединен с первым входом второго элемента И и с входом первого элемента задержки и является тактовым входом блока управления, первьй вход третьего элемента И соединен с первым входом третьего элемента ИЛИ и является первым входом логического условия блока управления, второй вход первого элемента И соединен с вторым входом второго элемента И и является вторым входом логического условия блока управления, вторые входы третьего элемента И и первого элемента ИЛИ являются соответственно третьим и четвертым входами логического условия блока управления, первьй вход четвертого элемента И соединен с первым входом пятого элемента И и ,с вторым входом второго элемента ИЛИ и является пятым входом логического условия блока управления, выход четвертого элемента ИЛИ соединен с счетным входом первого триггера, с первым входом пятого элемента ИЛИ и является первым выходом блока управления, нулевой выход второго триггера соединен с вторым входом пятого элемента И и является, вторым выходом блока управления, выход первого элемента задержки является третьим выходом блока управления, выход первого триггера является четвертым выходом блока управления, выход третьего элемента ИЛИ является пятым вьпсодом блока управления, выход второго элемента И соединен с вторым входом пятого элемента ИЛИ и является шестым выходом блока управления, выход первого элемента ИЛИ соединен с нулевым входом второго триггера и является седьмым выходом блока управления, выходы пятого и второго элементов ШШ являются соответственно восьмым и девятым выходами блока управления, при этом в блоке управления выход третьего элемента И соединен с входом одновибратора, выход которого соединен с первым входом четвертого элемента ШШ и с входом второго элемента задержки, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход первого элемента И соединен с вторым входом третьего элемента ИЛИ, выход пятого элемента И соединен с единичным входом

13760918

„О.ОГО .р„гг.ра.«,ня,.ь« i.o« котор - .... ГО соединен с вторьм входом четвертоготретьим вх м

| название | год | авторы | номер документа |

|---|---|---|---|

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1987 |

|

SU1515165A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

Изобретение относится к вьгаисли- тельной технике и может быть использовано в качестве устройства для ввода информации в системы регистрации и обработки информации. Цель изобретения - повышение производительности ЭВМ за счет уменьшения избыточности передаваемой информации. Устройство содержит два блока памяти, блок сравнения, блок управления, два коммутатора, два счетчика адреса, реверсивный счетчик, триггер. 1 з.п. ф-лы, 2 ил.

//d/

Фиг.2

| Еремеев И.С | |||

| Устройства сжатия информации | |||

| М.: Энергия, 1980, с«125 | |||

| Устройство для ввода информации | 1983 |

|

SU1144101A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-06-10—Подача