оэ

О)

tsD

СП 00

Изобретение относится к т,ехннке электросвязи и может быть использовано в цифровых системах передачи, применяющих многоуровневые блочные балансные коды с избыточностью.

Цель изобретения - повьшение помехоустойчивости блочной синхронизаЦРШ.

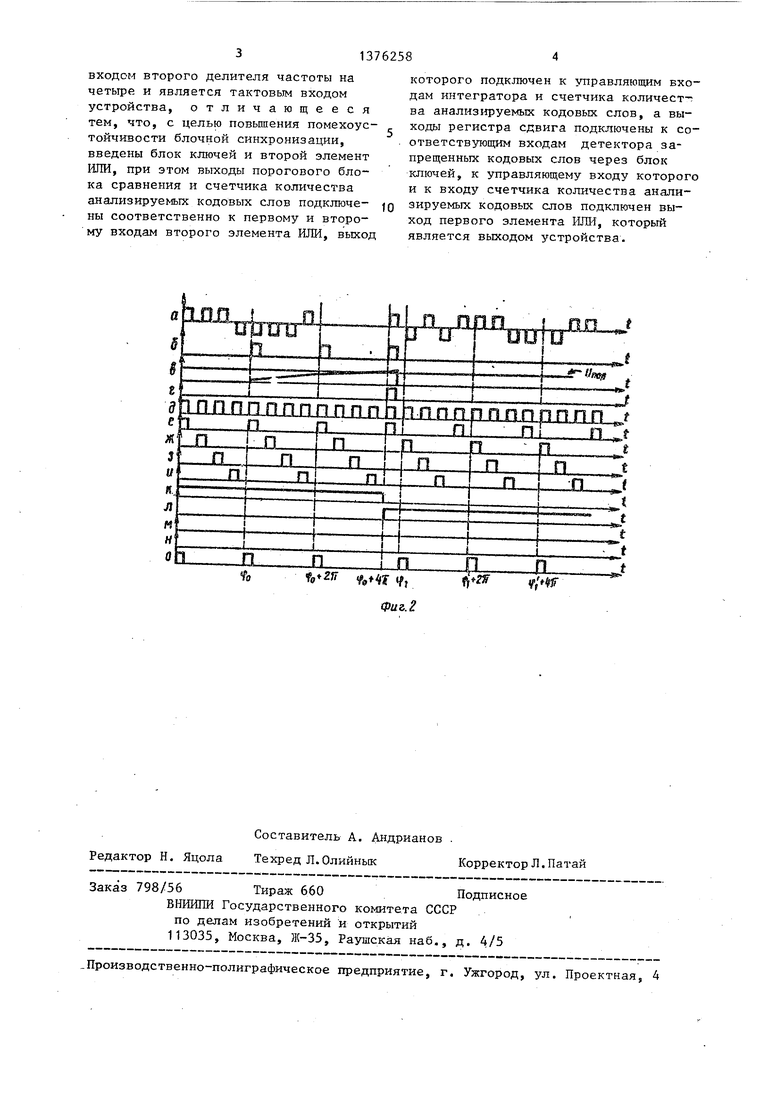

На фиг. 1 представлена структурная электрическая схема устройства для блочной синхронизации цифровой системы передачи; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство для блочной синхронизации цифровой системы передачи содержит регистр 1 сдвига, блок ключей 2, детектор 3 запрещенных кодовых слов, интегратор , пороговый блок 5 сравнения, первьо и второй делители 6 и 7 частоты на четыре, первый, второй третий и четвертый элементы И 8 - 11, первый и второй элементы ИЛИ 12 и 13 и счетчик 14 количества анализируе- мых кодовых слов.

Устройство для блочной синхронизации цифровой системы передачи работает следующим образом.

Принимаемые сигналы троичного линейного кода (фиг. 2а) с тактовой частотой (фиг. 2д) через регистр 1 поступают на соответствующие входы блока ключей 2, с выходов которого

сигналы поступают на соответствуюп ие входы детектора 3, Сигнал, поступающий на управляющий вход блока ключей 2, задает начальную фазу (фиг. 26) сигнала блочной синхронизации. В детекторе 3 осуществляется поиск запре щенных кодовых слов. При обнаружении запрещенного кодового слова на выходе детектора 3 формируется импульс (фиг. 26). Порядок работы детектора 3 определяется кодовой таблицей используемого кода. С выхода детектора 3 импульсы поступа от на интегратор 4 (фиг. 2в), на управляющий вход которого с выхода второго элемента ИЛИ 13 поступают импульсы, которые устанавливают интегратор- 4 в начальное состояние. С выхода интегратора 4 сигнал поступает на вход порогового блока 5, в котором он сравнивается с пороговым напряжением Up (фиг. 2в). В случае превьппения порога U на выходе порогового блока 5 формируется импульс (фиг. 2г), который постуг пает на первый вход второго элемента

10

15

, 5

20

30

35

45

40 г

0

РШИ 13 и на вход первого делителя 6 частоты. При поступлении на вход первого делителя 6 частоты импульса (фиг. 2г) сигнал логической еди1шцы переходит во второй разряд (фиг.2л), а выходы остальных разрядов устанавливаются в нулевое состояние (фиг.2к, м, и н) и т.д. Одновременно сигналы тактовой частоты (фиг. 2д) поступают на вход второго делителя 7 частоты. При поступлении на вход второго делителя 7 частоты сигнала логической единицы (фиг. 2д) импульс появляется только на выходе первого разряда (фиг. 2е). Каждый последующий импульс, поступающий на вход второго делителя 7 частоты, вызывает переход выходного сигнала в соседний разряд (фиг. 2ж, 3.и и).

Таким образом, в начальный момент вхождения в синхронизм совместная работа первого и второго делителей 6 и 7 частоты, первого, второго, третьего и четвертого элементов И 8 - 11 и первого элемента ИЛИ 12 обеспечивает установку начальной фазы синхросигнала (фиг. 2о) . При этом в интеграторе 4 начинается отсчет заданного количества запрещенных кодовых слов, а в счетчике 14 начинается отсчет заданного интервала из N кодовых слов. Интервал времени Т, определяемый количеством анализируемых кодовых слов N, зависит от задаваемого времени вхождения в синхронизм путем установки счетчика 14 в режим счета на N..

Формула изобретения

Устройство для блочной синхронизации цифровой системы передачи, содержащее регистр сдвига, последовательно соединенные детектор запрещенных кодовых слов, интегратор, пороговый блок сравнения и первый делитель частоты на четьфе, выходы которого подключены к первым входам . первого, второго, третьего и четвертого элементов И, к вторым входам которых подключены соответствующие выходы второго делителя частоты на четыре, выходы первого, второго, третьего и четвертого элементов И подключены к соответствующим входам первого элемента ИЛИ, счетчик количества анализируемых кодовых слов, тактовый вход регистра сдвига объединен с

входом второго делителя частоты на четыре и является тактовым входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости блочной синхронизации, введены блок ключей и второй элемент ИЛИ, при этом выходы порогового блока сравнения и счетчика количества анализируемых кодовых слов подключе- ны соответственно к первому и второму входам второго элемента ИЛИ, выход

которого подключен к управляющим входам интегратора и счетчика количест- ва анализируемых кодовых слов, а выходы регистра сдвига подключены к соответствующим входам детектора запрещенных кодовых слов через блок ключей, к управляющему входу которого и к входу счетчика количества анализируемых кодовых слов подключен выход первого элемента 1ШИ, который является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для блочной синхронизации цифровой системы передачи | 1984 |

|

SU1197119A2 |

| Устройство для блочной синхронизации цифровой системы передачи | 1983 |

|

SU1124438A1 |

| Устройство цикловой синхронизации блочных кодов | 1989 |

|

SU1688434A1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Устройство блочной синхронизации циклических кодов | 1980 |

|

SU919127A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1985 |

|

SU1376257A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи, применяющих многоуровневые блочные балансные коды с избыточностью. Цель изобретения - повьппение помехоустойчивости блочной синхронизации. Сигналы троичного линейного кода через регистр 1 сдвига и блок ключей 2 поступают на детектор 3 запрещенных кодовых слов. При обнаружении запрещенного кодового слова детектор 3 формирует импульс, который поступает на интегратор 4. При превышении напряжением интегратора 4 определенного порога пороговый блок 5 сравнения формирует импульс, по которому осуществляется сброс интегратора 4 через элемент ИЛИ 13, а в делителе частоты 6 на четыре происходит переход сигнала логической единицы в другой разряд. Делители частоты 6,7 на четыре, элементы И 8-11, ИЛИ 12 обеспечивают установку начальной фазы синхросигнала в начальный момент вхождения в синхронизм. Счетчик 14 количества анализируемых кодовых слов задает интервал времени. 2 ил.

| Устройство для блочной синхронизации цифровой системы передачи | 1983 |

|

SU1124438A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1984 |

|

SU1197119A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-23—Публикация

1985-11-10—Подача