Изобретение относится к технике электрической связи, может быть использовано в цифровых системах передачи, применяющих многоуровневые блочные балансные коды с избыточностью, И является усовершенствованием изобретения по авт.св. №1124438.. , Цель изобретения - уменьшение времени вхождения в синхронизм без уменьшения среднего, времени выхода из синхронизма.

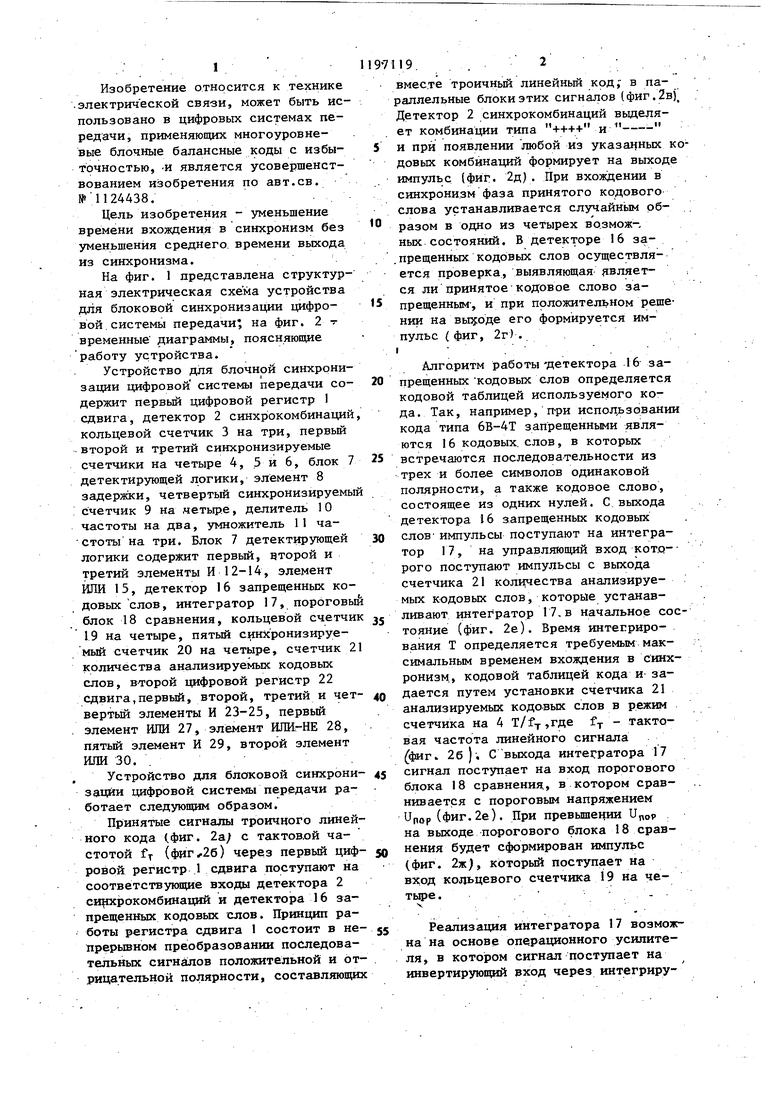

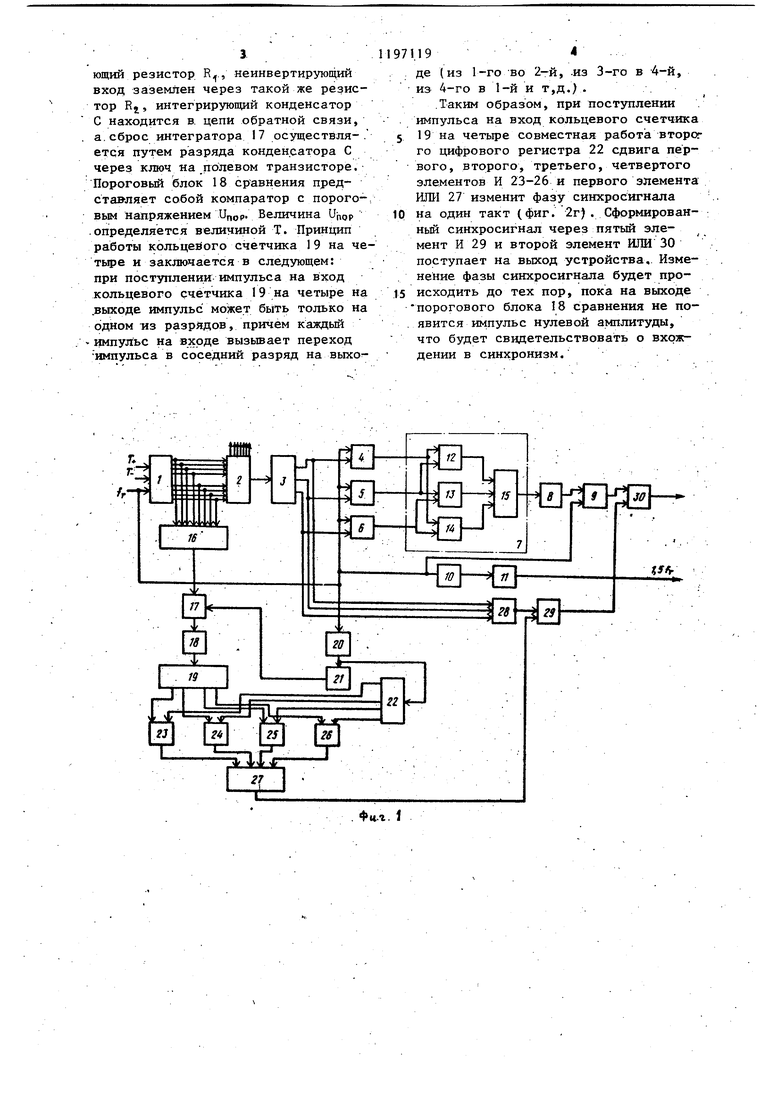

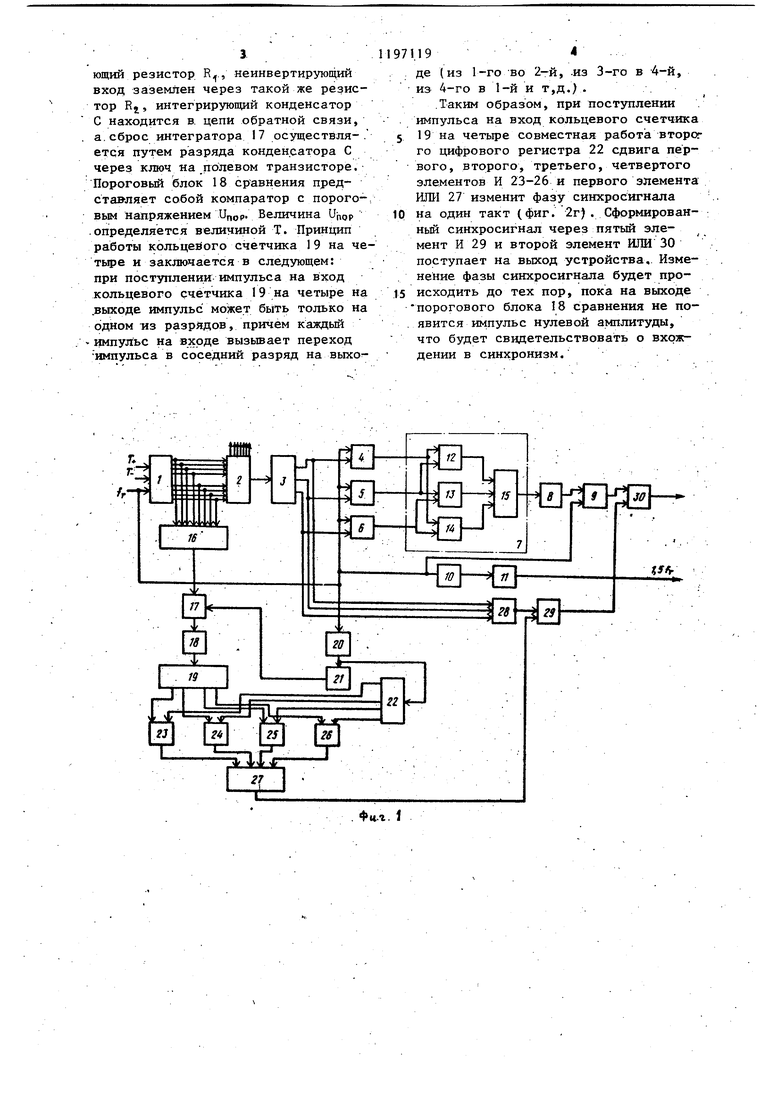

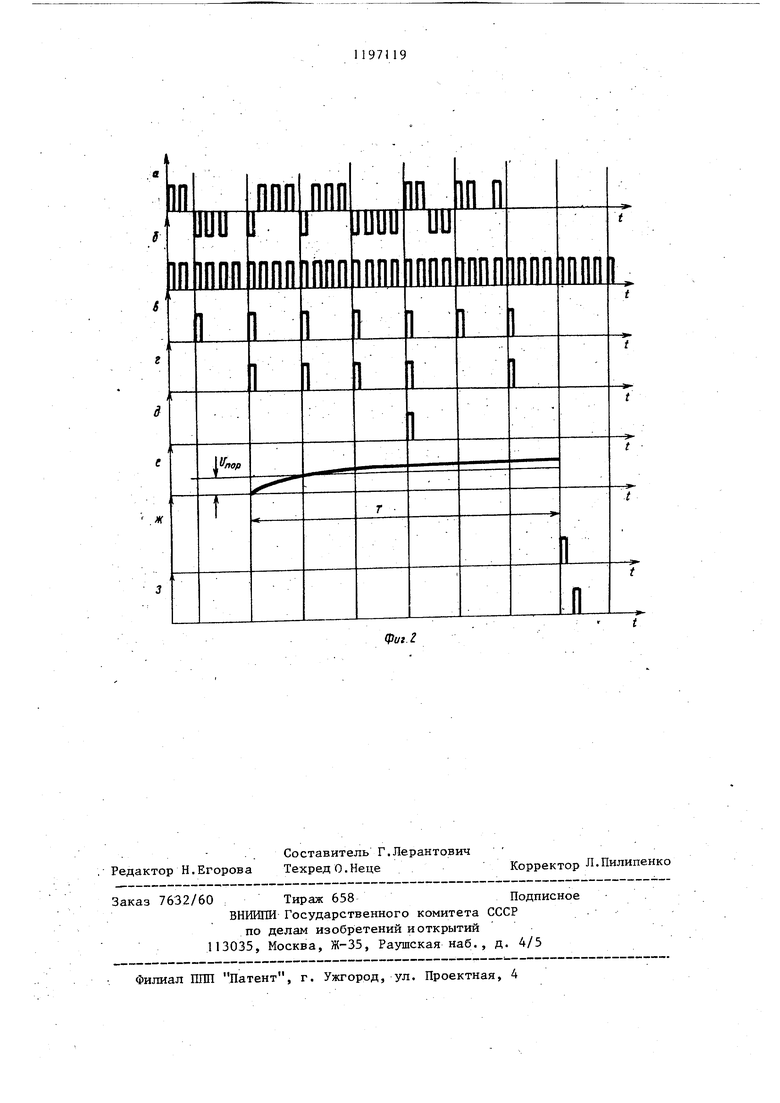

На фиг. 1 представлена структурная электрическая схема устройства для блоковой синхронизации цифровой.системы передачи на фиг. 2 т временные диаграммы, поясняющие работу устройства.

Устройство для блочной синхронизации цифровой системы передачи содержит первый цифровой регистр 1 сдвига, детектор 2 синхрокомбинаций кольцевой счетчик 3 на три, первьм второй и третий синхронизируемые счетчики на четыре 4, .5 и 6, блок 7 детектирующей логики, элемент 8 задержки, четвертый синхронизируемый Ьчетчик 9 На нетыре, делитель 10 частоты на два, умножитель 11 частоты на три. Блок 7 детектирующей логики содержит первый, второй и третий элементы И 12-14, элемент ИЛИ 15, детектор 16 запрещенных кодовых слов, интегратор 17, пороговый блок 18 сравнения, кольцевой счетчик 19 на четыре, пятый синхронизируемый счетчик 20 на четыре, счетчик 2 количества анализируемых кодовых слов, второй цифровой регистр 22 сдвига,первый, второй, третий и четвертый элементы И 23-25, первый элемент ИЛИ 27, элемент ИЛИ-НЕ 28, пятый элемент И 29, второй элемент ИЛИ 30. .

Устройство для блоковой синхронизации цифровой системы передачи работает следующим образом.

Принятые сигналы троичного линейного кода (фиг. 2а/ с тактов.ой частотой tf (фигЛб) через первый цифровой регистр 1 сдвига поступают на соответствующие входы детектора 2 сщ1хрокомбинаций и детектора 16 запрещенных кодовых слов. Принцип работы регистра сдвига 1 состоит в непрерывном преобразовании последовательных сигналов положительной и отрицательной полярности, составляющих

вмес.те троичный линейный код,- в параллельные блоки этих сигналов (фиг.2 Детектор 2 синхрокомбинаций вьщеляет комбинации типа ++++ и -

и при появлении любой из указанных довых комбйнагщй формирует на выход импульс (фиг. 2д). При вхождении в синхронизм фаза принятого кодового слова устанавливается случайном образом в одно из четырех возмож-, ных состояний. В детекторе 16 за.прещенных кодовых слов осуществляется проверка, выявляющая является ли принятое кодовое слово запрещенным-, и при положительном решении на вьщоде его формируется импульс (фиг, 2г) .

Алгоритм работы детектора 16 запрещенных КОДОВЫХ слов определяется кодовой таблицей используемого кода. Так, например, При использовани кода типа 6В-4Т запрещенными являются 16 кодовых, слов, в которых встречаются последовательности из трех и более символов одинаковой полярности, а также кодовое слово, состоящее из одних нулей. С выхода детектора 16 запрещенных кодовых СЛОВ импульсы поступают на интегратор 17, на управляющий вход KOT.Qрого поступают импульсы с выхода счетчика 21 количества анализируемых кодовых слов, которые устанавливают интегратор 17. в начальное сотояние (фиг. 2е). Время интегрирования Т определяется требуемым максимальным временем вхождения в синхронизм., кодовой таблицей кода и задается путем установки счетчика 21 анализируемых кодовых слов в режим счетчика на 4 Т/Гт-,где f-f - тактовая частота линейного сигнала (фиг. 2б), С выхода интегратора 17 сигнал поступает на вход порогового блока 18 сравнения., в котором сравнивается с пороговым напряжением ирор(фиг.2е). При превышении и„ор . на выходе порогового блока 18 сравнения будет сформирован импульс (фиг. 2ж), который поступает на вход кольцевого счетчика 19 на четыре .. V . -

Реализация интегратора 17 возмоясиа на основе операционного усилителя, в котором сигнал поступает на инвертирующий вход через интегрирующий резистор. R, неинвертирующий вход заземлен через такой же резистор Rj, интегрирующий конденсатор С находится в. цепи обратной связи, а. сброс интегратора 17 осуществля-. ется путем разряда конден.еатора С через ключ на полевом транзисторе. Пороговый блок 18 ср авнения представляет собой компаратор с пороговым напряжением Unoр. Величина Uhop определяется величиной Т. Принцип работы кольцевого счетчика 19 на четьфе и заключается в следующем: при поступлении импульса на вход кольцевого счетчика 19 на четыре на .выходе импульс может быть только на одном из разрядов, причем каждый импульс на входе вызьшает переход импульса в соседний разряд на выхо 1971,19

де (из 1-го -во 2-й, .из 3-го в -А-й, иэ 4-го в 1-й и т,д.).

.Таким образом, при постзшлении импульса на вход кольцевого счетчика 5 19 на четыре совместная работа второг го цифрового регистра 22 сдвига первого, второго, третьего, четвертого элементов И 23-26 и первого элемента ИЛИ 27 изменит фазу синхросигнала 10 на один такт (фиг.2г). Сформированньй синхросигнал через пятый элемент И 29 и второй элемент ИЛИ 30 поступает на выход устройства. Изменение фазы синхросигнала будет происходить до тех пор, пока на выходе порогового блока 18 сравнения не по. явится импульс нулевой амплитуды, что будет свидетельствовать о вхождении в синхронизм..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для блочной синхронизации цифровой системы передачи | 1985 |

|

SU1376258A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1983 |

|

SU1124438A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Устройство для обнаружения сбоя синхронизма декодирования при воспроизведении с носителя записи | 1984 |

|

SU1190415A1 |

| Устройство цикловой синхронизации блочных кодов | 1989 |

|

SU1688434A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

УСТРОЙСТВО ДЛЯ БЛОЧНОЙ СИНХРОНИЗАЦИИ ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ по авт.св. № 1124438,. о тличающееся тем, что, с целью уменьшения времени вхождения в синхронизм без уменьшения среднего времени выхода из синхронйзма, в него введены пятый.синхронизируемый счетчик импульсов на четыре, второй цифровой регистр сдвига, счетчик количества анализируемых кодовых слов, пять элементов И, элемент ИЛИ-НЕ, два элемента ИЛИ и последовательно .соединенные детектор запрещенных кодовых слов, интегратор, пороговьй блок сравнения и кольцевой счетчик на четыре, выходы которого подключены к первым.входам первого, второго, третьего и четвертого элементов И, к. вторым входам которых подключены вькоды второго цифрового, регистра сдвига, выходы первого, второго, третьего и четвертого элементов И через первый элемент ИЛИ подключены к первому входу пятого элемента И, к вто-. рому входу которого через элемент ИЛИ-НЕ подключены выходы кольцевого счетчика на три, выход пятого элемента И подключен к первому входу., второго элемента ИЛИ, выход которо- го является выходом устройства, а к второму входу второго элемента ИЛИ подключен выход четвертого синх(Л ронизируемого счетчика импульсов на четыре, при этом выходы первого цифрового регистра сдвига подключены к входам детектора запрещенных кодовых слов, а третий вход устройства объединен с входом пятого синхронизируемого счетчика импульсов на че тыре, выход которого подключен к входу второго цифрового регистра .сдвига непосредственно и через счетчик количества анализируемых кодо вых слов к управляющему входу интегратора..

Т

ШШ lIUHLUinn

ш

i

1Ш

ШШ

1Ш1

ша

JK

| Способ сматывания нити с паковки и устройство для его осуществления | 1988 |

|

SU1564085A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для блочной синхронизации цифровой системы передачи | 1983 |

|

SU1124438A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-12-07—Публикация

1984-10-15—Подача