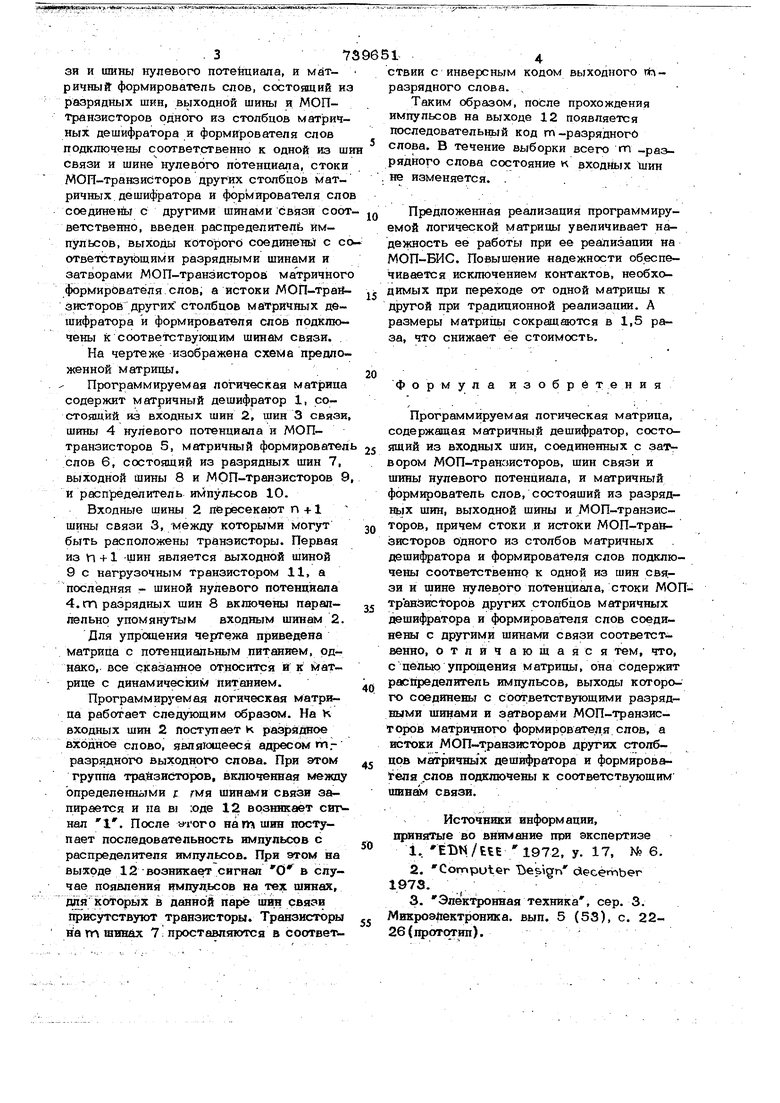

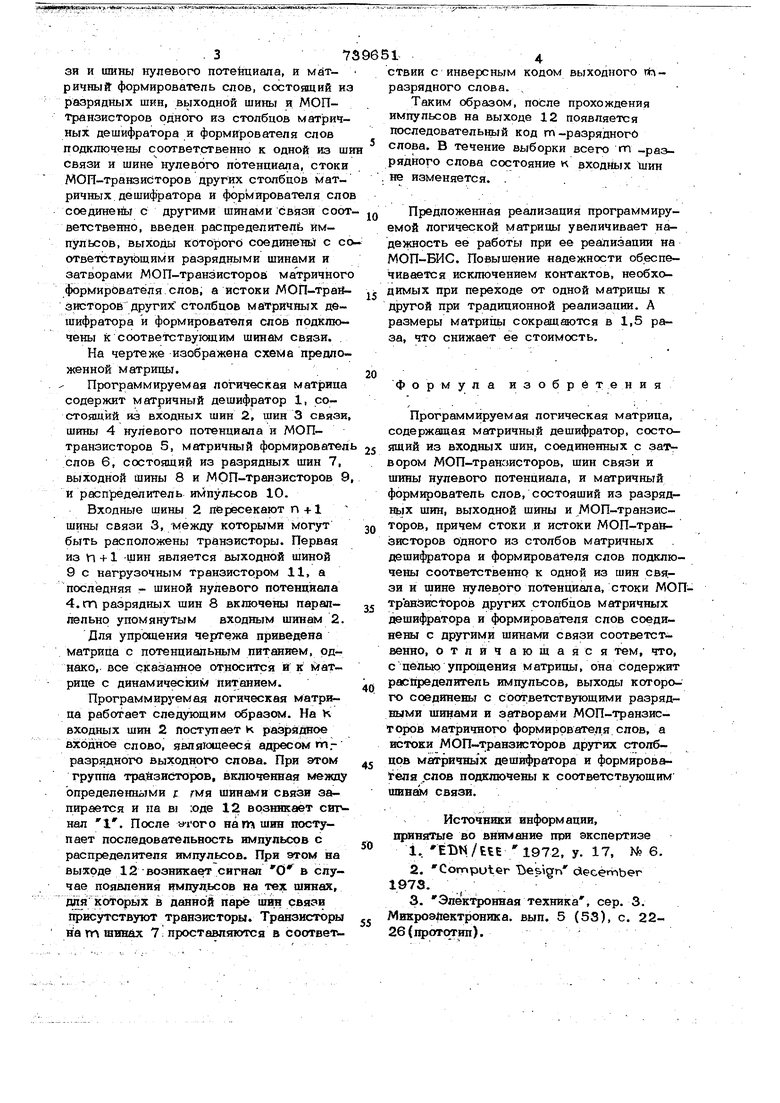

ч , Изобретение отнсюится к области авто1у)атики и вычиспитепьной техники и может найти применение при разработке программируемых логических матриц для управления imcKfieTHbjми устройствами. Известны программируемь1е логические ма1рицываМ(ЭТ-транзисторах flj к f 2, состоящие иа дауХ взаимно перпендикупярны мвтрйп. Первая матрица предстайляет собой дешифратор k-разрядного входного ело ба, имеющий п выходов, а - поле памяти rv -разрядных выходных Слов. Констр уктйвно матрицы построены из пар1алnenbiao;расположенных диффузионных П1нн, Мбнсду ксйгбралми мотут быть включейь ТранзнсТрфы Межау камщымн двумя вы ходиьтмв щвиакги рйспопозкена общая (эемпяная) шина, что приводит к увеличению гшбщади, заНйм аемрй программируемой по тйческой матрицей при ее реализаций на большой интёгр альн6й схеме (БИС)(площадь БИС- основной фактор, влияющий на ее стоимостьУ. Наиболее близким по технической сущности к изобретению является программируемая логическая матрица 3 , построенная на МОП-транзисторах и состоящая из двух взаимно перпендикулярных матриц. Она содержит входных и гп выходных сигнальных щин. Между каждыми двумя входными шинами расположена общая земляная шира. Недостатки известных матриц связаны с их размерами, требования к которым гфи реализации их на БИСах являются очень ясесткиМй. Наличие значительного числа KOHl-siKTbB, необходимых при переходе от одной матрицы к другой, снижает надеядаость матрицы. Целью избёретёния является упрощение матрицы за счёт уменьшения ее размеров при интегральном исполнении. Поставленная цель достигается тем, что в программируемую логическую матрицу, содержащую матричный дешифратор, состоящий из входных шин, соепинеш1ых с зепгвор1ами МОП-транзисторов,шин сея73зи и ишны нулевого потейциапа, и матричныйг формирователь слов, состоящий из разрядных шин, выходной шины и МОПтрйнзисторов однотч} из столбцов матричных дешифратора и формирователя слов подключены соответственно к одной из шин связи и шине нулевого потенциала, стоки МОП-транзисторов других столбцов матричных, дешифратора и формирователя слов соединены с другими шинами связи соответственно, введен распределитель ймпульсов, выходы которого соедине№1 с ccw ответствуйщими разрядными шинами и затворами МОП-транзисторов матричного формирОв атёл я с лов, а исток и М О П-тр айзисторов другихстолбцов матричных дешифратора и формирователя слов подключены к соответствующим шинам связи. На чертеже изображена схема предложенной матрицы. Программируемая логическая матрица содержит матричный дешифратор 1, состоящий из входных шин 2, шин 3 связи, шины 4 нулевого потенциала и МОП- транзисторов 5, матричный формировате слов 6, состоящий из разрядных шин 7, выходной шины 8 и МОП-транзисторов и расп эеделитель и тпу-льсов 10. Входные шины 2 пересекают п +1 шины связи 3, между которыми могут быть расположены транзисторы. Первая из п +1 шин является выходной шиной 9 с нагрузочным транзистором 11, а последняя - шиной нулевого потенциала 4. па разрядных шин 8 включены параллельно упомянутым входным шинам 2 Для упрсхцения чертежа приведена матрица с потенциальным питанием, однако, все сказанное относится я к матрице с динамическим питанием. Программируемая логическая матрица работает следующим образом. На К входных шин 2 поступает k разрядное входное слово, являющееся адресом т.разрядного выходного слова. При этом группа трайзисторов, включенная между определенными jc гмя шинами связи запирается и на BI :оде 12 возникает свр нал 1. После учого нат шин поступает последовательность импульсов с распределителя импульсов. При этом на выходе 12 возникает сигнал 0 в случае появления импудьсов на тех шннах, шя которых в данной паре шин связи присутствуют транзисторы. Транзисторы на m шинах 7 проставляются в соответ14ствии с инверсным кодом выходного Пглразрядного слова. . Таким образом, после прохождения импульсов на выходе 12 появляется последовательш 1й код т-разрядногй слова. В течение выборки всего пп -разрядного слова состояние « входных шин не изменяется. . Предложенная реализация программируемой логической матрицы увеличивает наде5кность ее работы при ее реализации на МОП-БИС. Повышение надежности обеспечивается исключением контактов, необходимых при переходе от одной матрицы к другой при традиционной реализации. А размеры матрицы сокращаются в 1,5 раза, что снижает ее стоимость. Формула изобретения Программируемая логическая матрица, содержащая матричный дешифратор, состо- ящий из входных шин, соединенных с заТг вором МОП-транзисторов, шин связи и шины нулевого потенциала, и матричный формирователь слов, состояший из разрядHtiix шин, выходной шины и МОП-транзисторов, причем стоки и истоки МОП-траНэисторов одного из столбов матричных дешифратора и формирователя слов подключены соответственно к одной из шин связи и шине нулевого потенциала, стоки МОПтранзисторов других столбцов матричных дешифратора и формирователя слов соединены с другими шинами связи соответственно, отличающаяся тем, что, с целью упрощения матрицы, она содержит расttpeделитель имнульсов, выходы которого соединены с соответствующими разрядными шинами и затворами МОП-транзисторов матричного формирователя слов, а истоки МОП-транзисторов других столбцов матршчных дешифратора и формирова гепя слов подключены к соответствующим шивеои связи. Источники информации, принятые во внимание при экспертизе 1.. EUN/EtE 1972, у. 17, № 6. 2.Computer olecember 1973. 3. Электронная техника , сер. 3. Микроэлектроника, вып. 5 (53), с. 2226 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое логическое устройство | 1979 |

|

SU864338A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Программируемая запоминающая матрица | 1981 |

|

SU1003144A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Программируемое логическое устройство | 1980 |

|

SU982092A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

Авторы

Даты

1980-06-05—Публикация

1976-10-04—Подача