Изобретение относится к области вычислительной техники и может найги применение в ЦВМ и приборах четвертого поколения

Известны постоянные запоминающие устройства (ПЗУ), содержащие числовые блоки с большим числом элементов связи, либо с большим числом прошитых сердечников ij,

Однако такие ПЗУ недостаточно надежны, потребляют большую мощность и в них неравномерна нагрузка на адресные шины.

Наиболее близким к изобретению является ПЗУ, содержащее дешифратор адреса, выходы которого подключены ко входам первого и второго накопителей, дешифратор коррекций, выходы которого подключены к входам BTOporip накопителя, и сумматор по модулю два.

Такое устройство также недостаточно надежно, и в нем можно использовать только матрицы накопителей, в которых есть только отказы кратности К-1.

Целью изобретения является повышение надежности устройства.

Эта цель достигается тем, что устройство содержит Бычитатель и третий накопитель, ко входам которого подключены выходы дешифратора адреса. Одни выходы пе вого и третьего накопителей через сумматор по модулю два, а другие непосредственно подключены к соответствующим входам вы читателя.

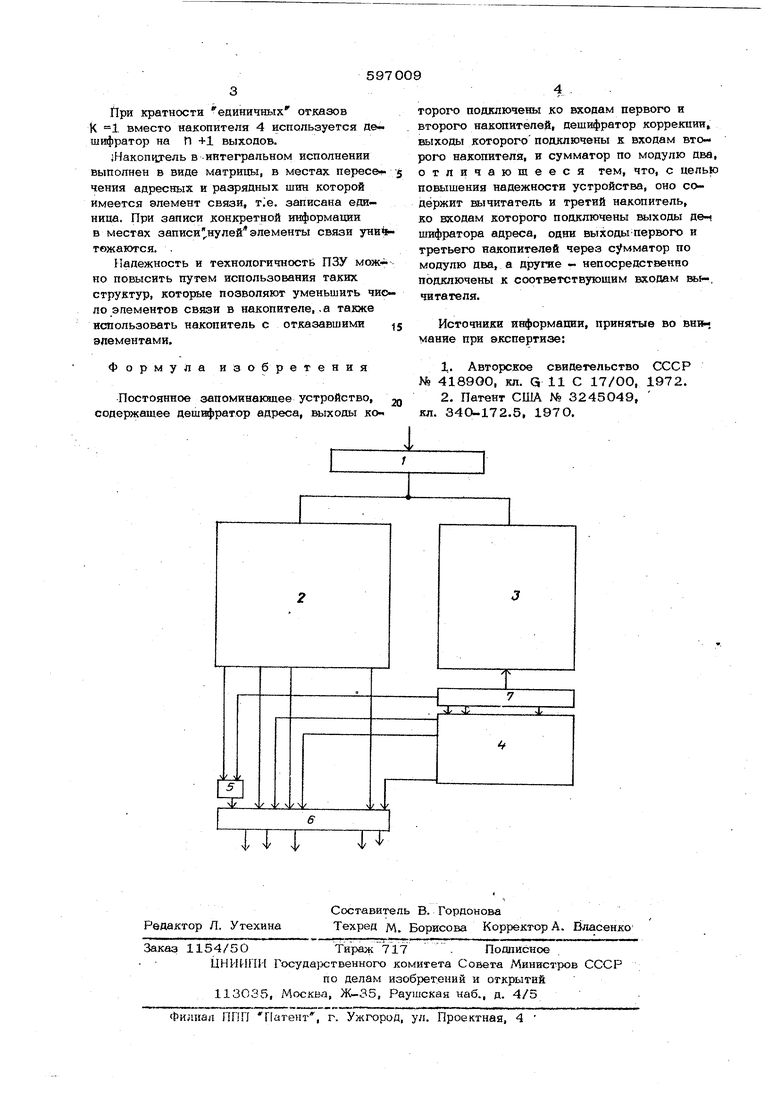

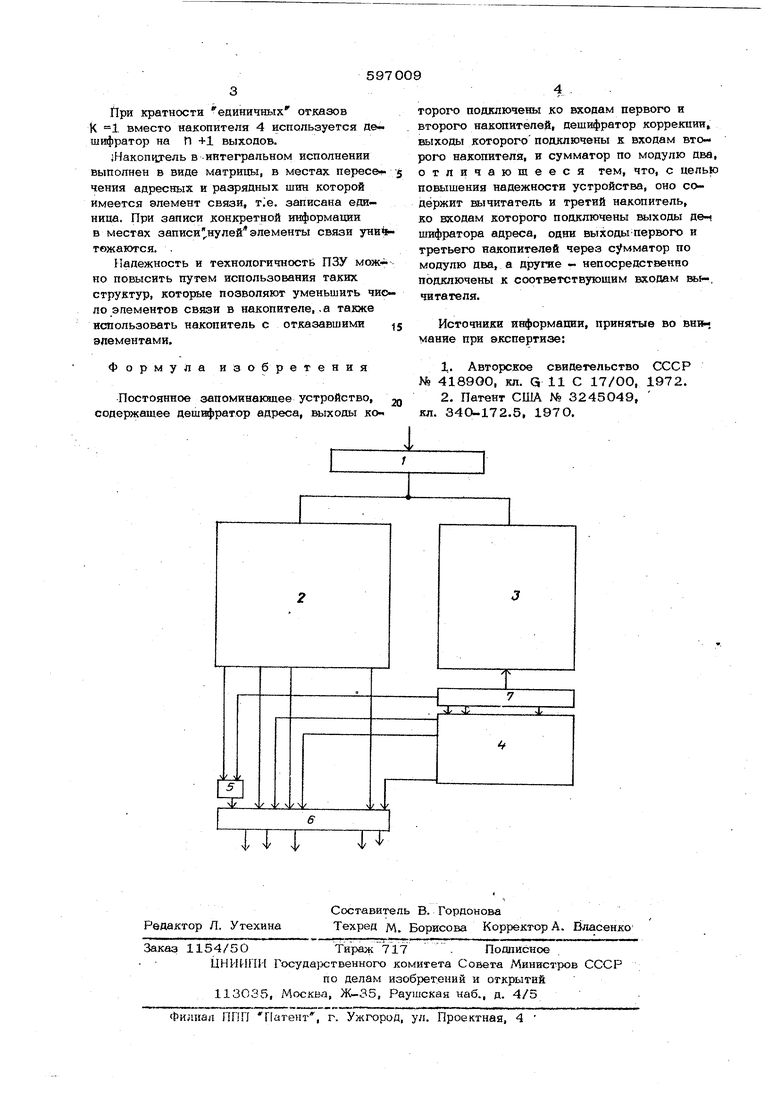

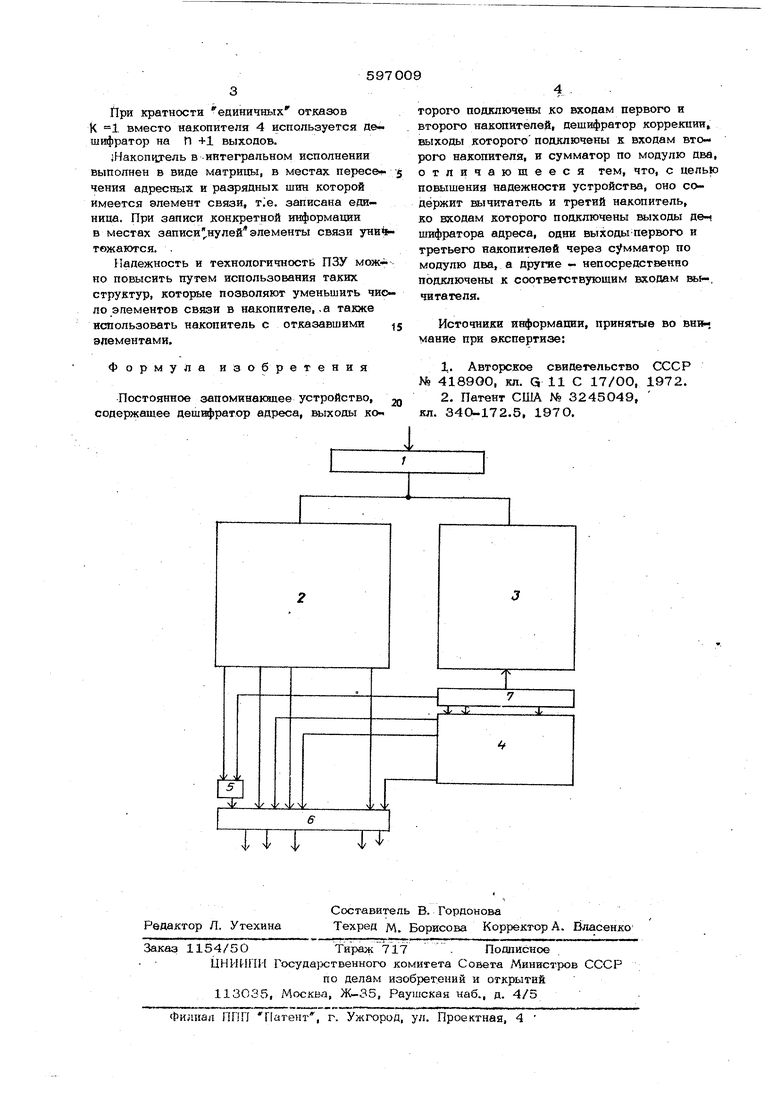

На чертеже дана структурная схема предлагаемого устройства.

Устройство содержит дешифратор адреса 1, первый 2, второй 3 и третий 4 накопители, двухвходовой сумматор по модулю два 5, вычитатель 6 и дешифратор коррекции 7

Устройство работает следующим образом

Сигнал поступает на дешифратор адреса Г, от которого идет обращение к накопителям 2 и 3. В накопителе 3 считывается адрес числа, содержащегося в накопителе 4, и по этому адресу считывается само число. Копы .чисел из накопителей 2 и 4 поступают на вычитатель 6, а их старшие разряды предварительно суммируются на сумматоре по модулю два. На выходах выи читателя G, которые явлтотся В1.1ходами /стрюйства, считывается нужное число кратности ецияичных отказов К 1 вместо накопителя 4 используется дешифратор на П +1 выходов. ;Накопчтель в -интегральном исполнении выполнен в виде матрицы, в местах переевчения адресных и разрядных шин которой имеется элемент связи. Tie. записана единица. При записи конкретной информации в местах записи ,нулей элементы связи уни твжаются. . Надежность и технологичность ПЗУ мож но повысить путем использования таких структур, которые позволяют уменьшить чи ло элементов связи в накопителе,, а также использовать накопитель с отказавшими элементами. Формула изобретения Постоянное запоминающее устройство, содержащее дешифратор адреса, выходы ко торого подключены ко входам первого и второго накопителей, дешифратор коррекции, выходы которого подключены к входам второго накопителя, и сумматор по модулю два, отличающееся тем, что, с целью повышения надежности устройства, оно содержит вычитатель и третий накопитель, ко входам которого подключены выходы де-i шифратора адреса, одни выходыПервого и третьего накопителей через cjfMMaTop по модулю два, а другае - непосредственно подключены к соответствующим входам вы-, читателя. принятые во внвн. Источники информации, мание при экспертизе; 1,. Авторское свидетельство СССР № 4189ОО, кл. Q 11 С 17/00, 1972. 2, Патент США № 3245049, кл. 340-172.5, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU627543A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

Авторы

Даты

1978-03-05—Публикация

1977-02-01—Подача