Изобретение относится к автоматике и бычиспительной технике и может быть использовано в цифровых вычислительных машинах.

Известно постоянное запоминающее

устроЛзтво, содержа цее числовой блок с бопьшшы числом элементов связи 1.

Оно характеризуется большой потребляемой мощностью, яеравномерносгью нагрузки на адресные шины.

Наиболее по . технической сущности к изобретению является постоянное запоминающее устройство, сонержащее дешифратор адреса, выходы которого соединены с входами накопнтеля, и управляющие шины, которые подключены к сумматорам но модулю два C2J.

Недостатками устройства является большое число элементов связи, значител ная разрядность числового блока, низкая надежность работы.

Келью изобретения является повышени наде кности, а также уменьшение потребпяемой мощности.

Цель достигается тем, что постоянное запоминающее устройство содержит регистр, дополнительные управляющие шины, одни из которых через элементы И соединены с дополнительными су мато- рами по модулю два, соединены через дополнительные сумматоры по модулю два, с соответствующими элементами И, выходы которых соединены с входами основных и дополнительных сумматоров по модулю два,. а входы подключены к выходам регистра.

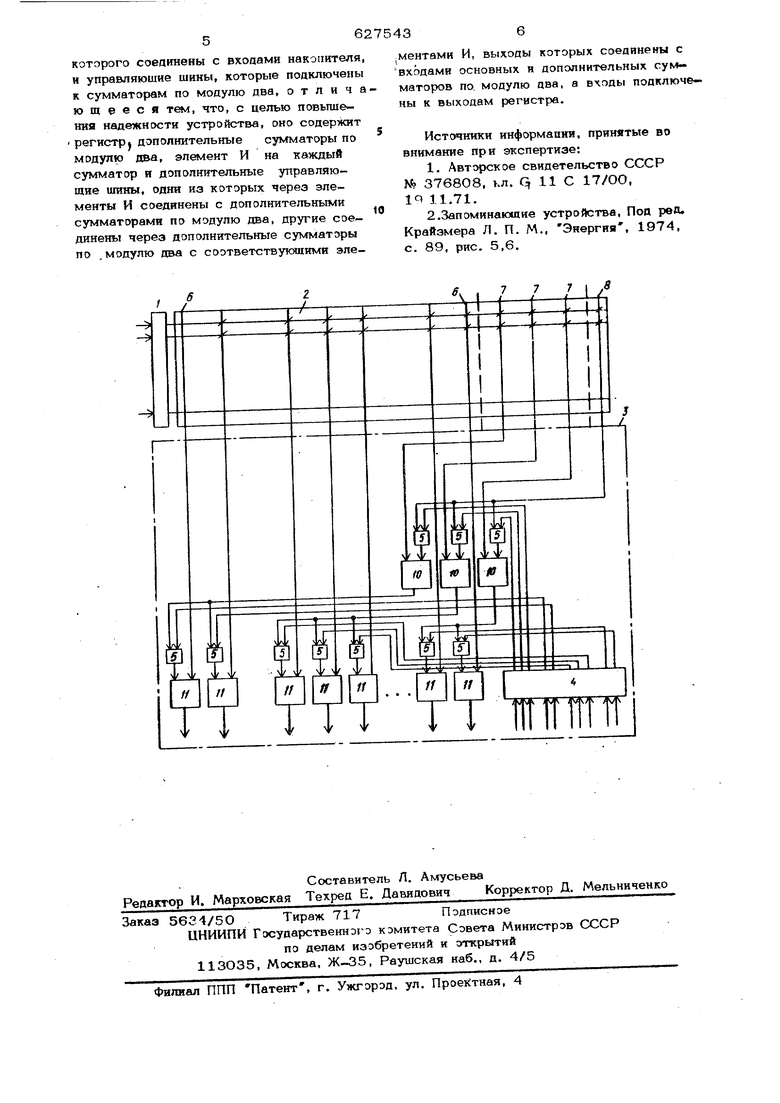

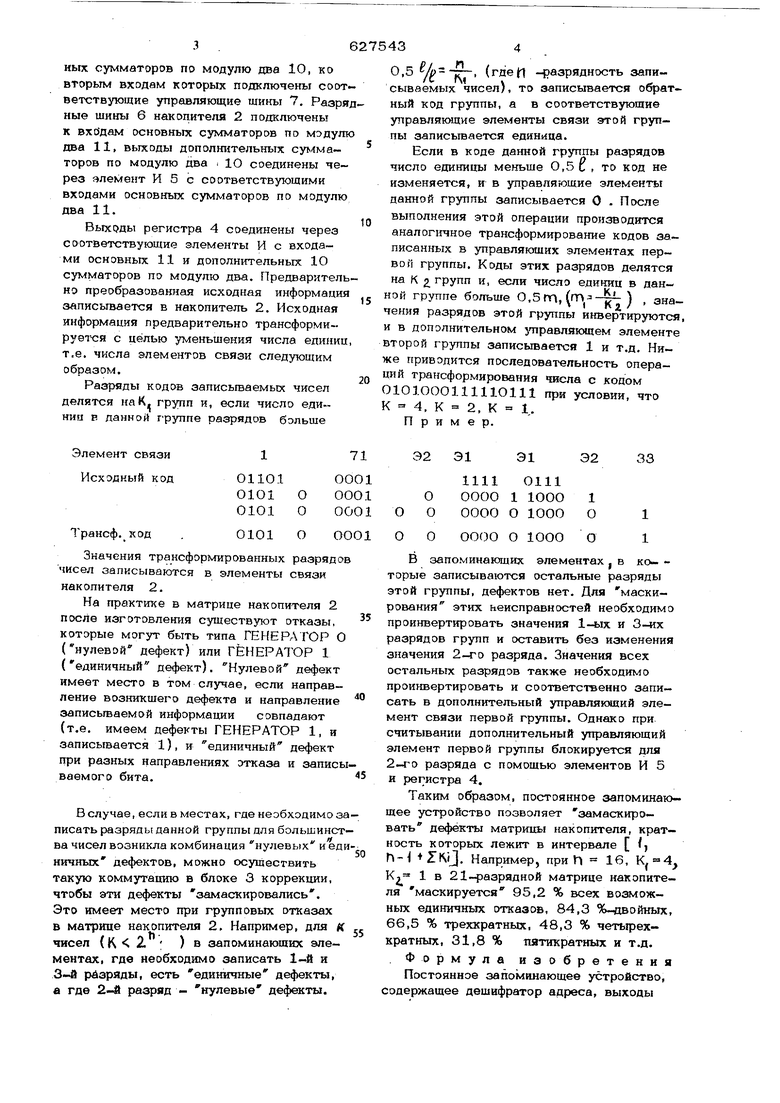

На чертеже представлена функционалы- ная схема устройства.

Устройство содержит дешифратор 1 адреса, накопитель 2 и блок 3 коррекции, построенный на основе сумматоров по модулю два, регистра 4 и элементов И 5. Накопитель 2 содержит разрядные шины 6, управляющие шины 7 и дополнительные управлакйдие шины 8. Выходы дешифратора адреса 1 подключены к входам накопителя 2. Дополнительная управляющая шина 8 через группу элементов И 5 подключена к первым входам дополнительных сумматоров по модулю два 10, ко вторым входам которых подключены соот ветствующие управляющие шины 7. Разря ные шины б накопителя 2 подключены к входам основных сумматоров по модулю два 11, выходы дополнительных су лматоров по модулю два 1О соединены через элемент И 5 с соответствующими входами основных сумматоров по модулю два 11. Выходы регистра 4 соединены через соответствующие элементы И с входами основных 11 и дополнительных 1О сук маторов по модулю два. Предваритель но преобразованн 1Я исходная информация записывается в накопитель 2. Исходная информация предварительно трансформируеахгя с целью уменьшения числа единиц т.е. числа элементов связи следующим образом. Разряды кодов записьтаемых чисел делятся на К, групп и, если число единиц в данной группе разрядов больше

0001

01101

О О ООО1

О1О1

0101 0001 Трансф. код О101 О O Значения трансфор1 л1рованных разрядо чисел записываются в элементы связи накопителя 2. На практике в матрице накопителя 2 после изготовления существуют отказы, которые могут быть типа ГЕНЕРАТОР О (нулевой дефект) или ГЕНЕРАТОР 1 (единичный дефект). Нулевой дефект имеет место в том случае, если направление возникшего дефекта и направление записьтаемой информации совпадают (т.е. имеем дефекты ГЕНЕРАТОР 1, и записьгеается 1), и единичный дефект при разных направлениях отказа и записы ваемого бита. В случае, если в местах, где необходимо з писать разрядь данной группы для большинст ва чисел возникла комбинация нулевых иед ничных дефектов, можно осу1пествить такую коммутацшо в блоке 3 коррекции, чтобы эти дефекты замаскировались. Это имеет место при групповых отказах в матрице накопителя 2. Например, для к чисел {К 2. ) в запоминающих элементах, где необходимо записать 1-Л и 3-й разряды, есть единичные дефекты, а где 2-Л разряд - нулевые дефекты.

2 Э1

33

Э2

Э1

0111

1111

О

0000 1 1000

1

оооо

о о 10ОО

о 0,5 /P- ( -разрядность записываемых чисел), то записывается обратный код группы, а в соответствующие управляющие элементы связи этой группы записывается единица. Если в коде данной группы разрядов число единицы меньше О,5 С , то код не изменяется, и в управляющие элементы данной группы записьшается О . После выполнения этой операции производится аналогичное трансформирование кодов записанных в управляющих элементах перво группы. Коды этих разрядов делятся на К 2. групп и, если число единиц в даной группе больше О,5т, ( ) , знаения разрядов этой группы инвертируются, в дополнительном зтравляющем элементе торой группы записывается 1 и т.д. Ние приводится последовательность операий трансформирования числа с кодом 101000111110111 при условии, что 4, К 2, К 1. Пример. О О ОООО О 10ОО О В запоминающих элементах, в ко- торые записываются остальные разряды этой группы, дефектов нет. Для маскирования этих неисправностей необходимо проинвертировать значения 1-ых и 3-их разрядов групп и оставить без изменения значения 2-го разряда. Значения всех остальных разрядов также необходимо проинвертировать и соответственно записать в дополнительный управляющий элемент связи первой группы. Однако при считывании дополнительный управляющий элемент первой группы блокируется для 2-го разряда с помощью элементов И 5 и регистра 4. Таким образом, постоянное запоминающее устройство позволяет замаскировать дефекты матрицы накопителя, кратность которых лежит в интервале j h- . Например, при П 16, , Кп 1 в 21-фазрядной матрице накопителя маскируется 95,2 % всех возможных единичных отказов, 84,3 %-двойных, 66,5 % трехкратных, 48,3 % четьфехкратных, 31,8 % пятикратных и т.д. Формула изобретения Постоянное запоминающее устройство, содержащее дешифратор адреса, выходы которого соеаинены с входами накопителя и управляющие шины, которые подключены к сумматорам по модулю два, отлич ющееся тем, что, с целью повьпиения надежности устройства, оно содержит регистру дополнительные сумматоры по модулю два, элемент И на каждый сумматор и допопнительные управляющие иганы, опни из которых через элементы И соединены с дополнительными сумматорами по модулю два, другие соединены через дополнительные сумматоры по .модулю два с соответствующими эле ментами И, выходы которых соединены с входами основных и дополнительных сумматоров по, модулю два, а входы подключены к выходам регистра. Источники информации, принятые во внимание при экспертизе; 1, Авторское свидетельство СССР NO 376808, кл. Q 11 С 17/ОО, 11.71. 2.Запоминающие устройства. Под рвД, Крайзмера Л. П. М,, Энергия, 1974, с. 89, рис. 5,6.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Постоянное запоминающее устройсство | 1977 |

|

SU637869A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU649039A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU641499A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

Авторы

Даты

1978-10-05—Публикация

1977-02-01—Подача