групп соединены с соответствующими выходами второго дешифратора пяти- фазного кода, прямой и инверсный вы ходы которого являются прямым и инверсным выходами частотного делителя на 2, прямой вход второго разряда второго входа делимого делителя на 2 соединен с первыми входами третьих элементов И первой и третьей групп, вторыми входами первых элементов И второй и четвертой групп четвертого элемента И четвертой . группы, третьими входами вторых элементов И шестой и седьмой групп и третьими входами четвертого, шестого и восьмого элементов И седьмой группы, инверсный .вход второго разр|Яда второго входа делимого делителя на 2 соединен с перёСлми входами четвертого элемента И первой группы, третьего элемента И второй и четвертой групп, вторыми входами вторых элементов И первой и третьей групп третьими входами первого, третьего и четвертого элементов И шестой группы и третьим входами первого, третьего, пятого и седьмого элементов И седьмой группы, прямой вход третьего разряда второго входа делимого делителя на 2 соединен с первыми входами пятого элемента И первой группы, четвертых элементов И второй, третьей и четвертой групп, с вторьвм1и входами первого и третьего элементов И третьей группы, третьим входом первого элемента И четвертой группы и четвертьми входами третьего, четвертого и седьмого элементов К седьмой группы, инверсный вход третьего разряда второго входа делимого делителя на 2 соединен с первыми входами пятых элементов И второй,третьей и четвертой групп,вторь 1И входами четвертого элемента И первой группы,третьего элемента И второй группы,третьим входомвторого элемента И первой группы и четвертыми входами первогодвторого. Пятого и шестого элементов И седьмой группы, прямой вход четвертого

разряда второго входа делимого делителя на 2 соединен с вторыми входа-ми .второго, третьего и пятого элементов И четвертой группы, пятых элементов И второй и третьей групй, третьим входом второго и третьего элементов И второй группы, второго элемента И третьей группы, четвертого элемента И первой группы и четвертьа4 входом второго элемента И первой группы и является прямым выходом остатка делителя на 2, инверсный вход четвертого разряда втррого входа делимого делителя на 2 соединен с вторыми входами первого, третьего и пятого элементов И первой группы, четвертых элементов И второй и третьей групп, третьими входами первых элементов И второй и третьей групп, третьего элемента И . третьей группы, четвертого элемента И четвертой группы и четвертым входом первого элемента И четвертой 1 руппы и является инверсным выходом остатка делителя на 2, первый, второй, третий и четвертый выходы первого дешифратора пятифазного кода соединены соответственно с четвертыми входами первого элемента и второй группы, четвертых элементов И четвертой и первой групп, второго элемента И третьей группы, пятый, шестой, седьмой и восьмой выходы дешифратора пятифазного кода соединены соответственно с третьими входами первого элемента И первой группы, четвертого элемента И третьей группы, пятого элемента И втррой группы и второго элемента И четвертой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное устройство для деления | 1983 |

|

SU1141402A1 |

| Устройство для деления | 1984 |

|

SU1252772A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| Преобразователь кодов | 1986 |

|

SU1381717A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1985 |

|

SU1291974A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1979 |

|

SU922728A1 |

| Устройство для деления в избыточном последовательном коде | 1986 |

|

SU1365078A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

1. ПРЕОБРАЗОВАТЕЛЬ ПОЗИЦИОННОГО КОДА В ДЮИЧНЫЙ КОД, содержащий треугольную матрицу блоков деленил, первые входы делимого делителя первой строки которой соединены с входами преобразователя, выходы всех разрядов преобразователя, кроме старшего, соединены с выходами частного последних блоков деления всех строк треугольной матрицы, в -й строке которой

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах автоматики, цифровых системах управления электроприводами и в вычислительных устройствах.

Известно устройство для преобразования двоично-десятичных.чисел в двоичный код, выполненное в виде прямоугольной матрицы, содержащей при преобразовании в (m+l)-и разрядный дао ичный код m строк и (mlg 2) столбцов десятичных делителей на два, причем выходы с весё1ми 8 4 2

любого i-ro десятичного делителя на два любого j-ro столбца соединены с входами разрядов тех же весов (1+1)-го десятичного делителя на ,5 два того же столбца, а выход с весом i-ro делителя на два j-ro столбца соединен с входом разряда с весом 10 (i+D-ro столбца 1 .

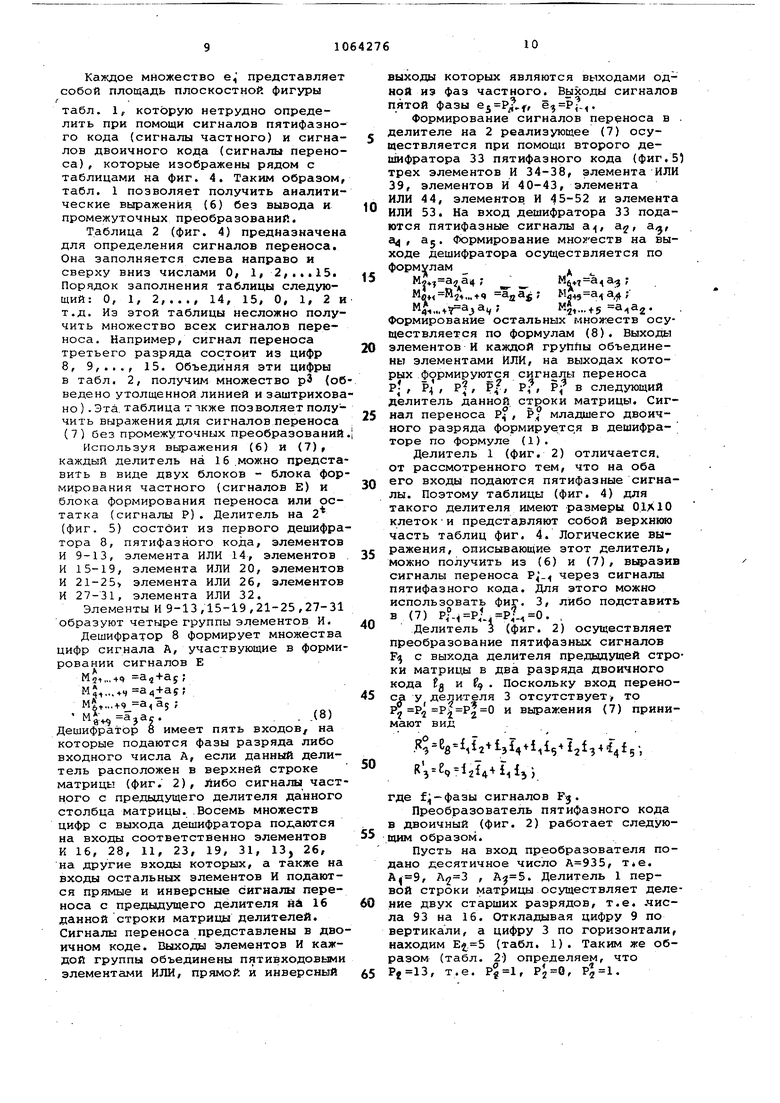

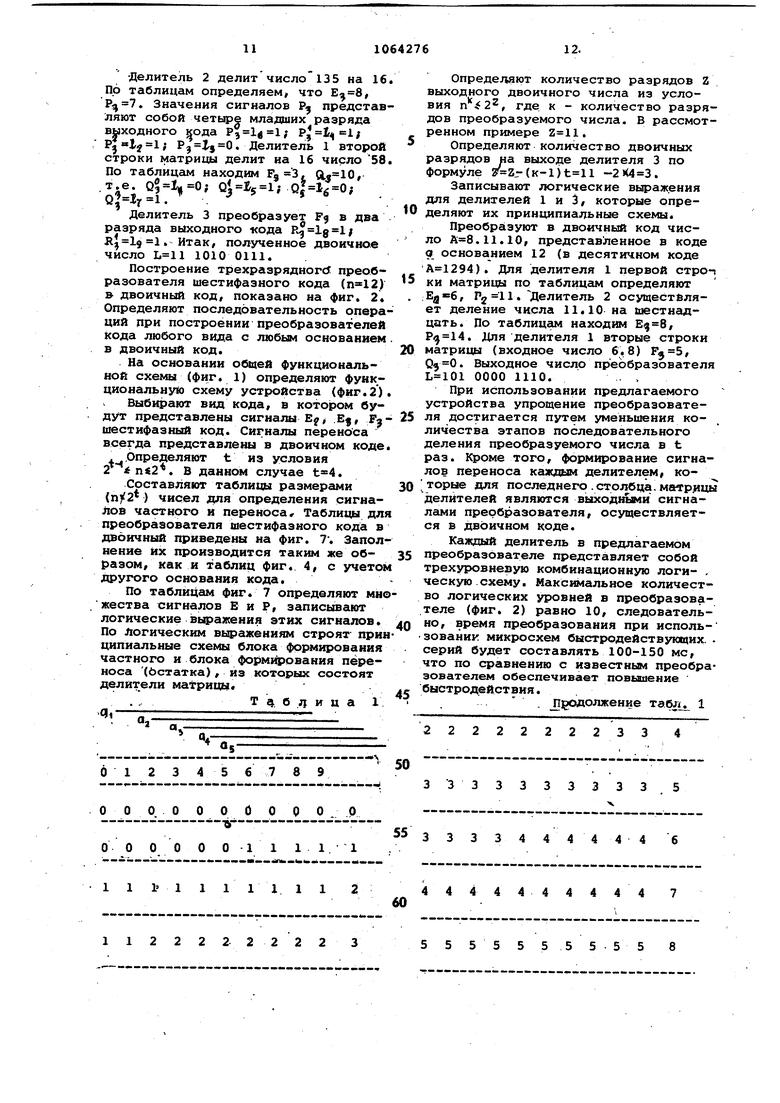

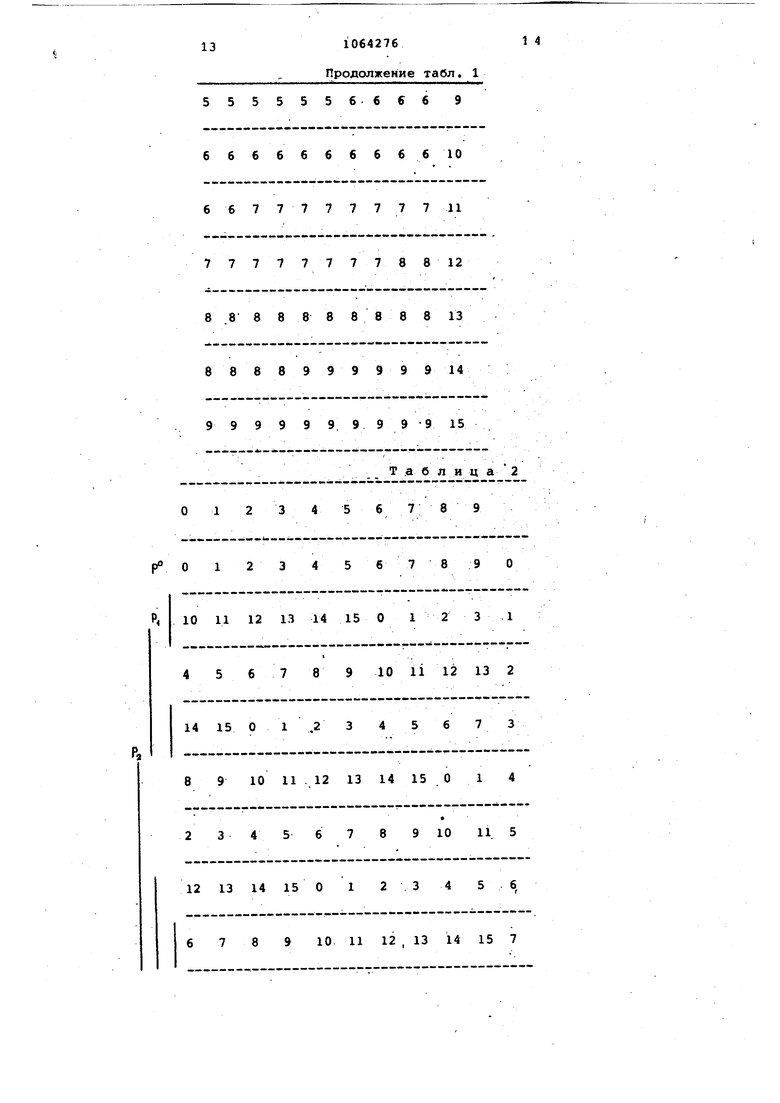

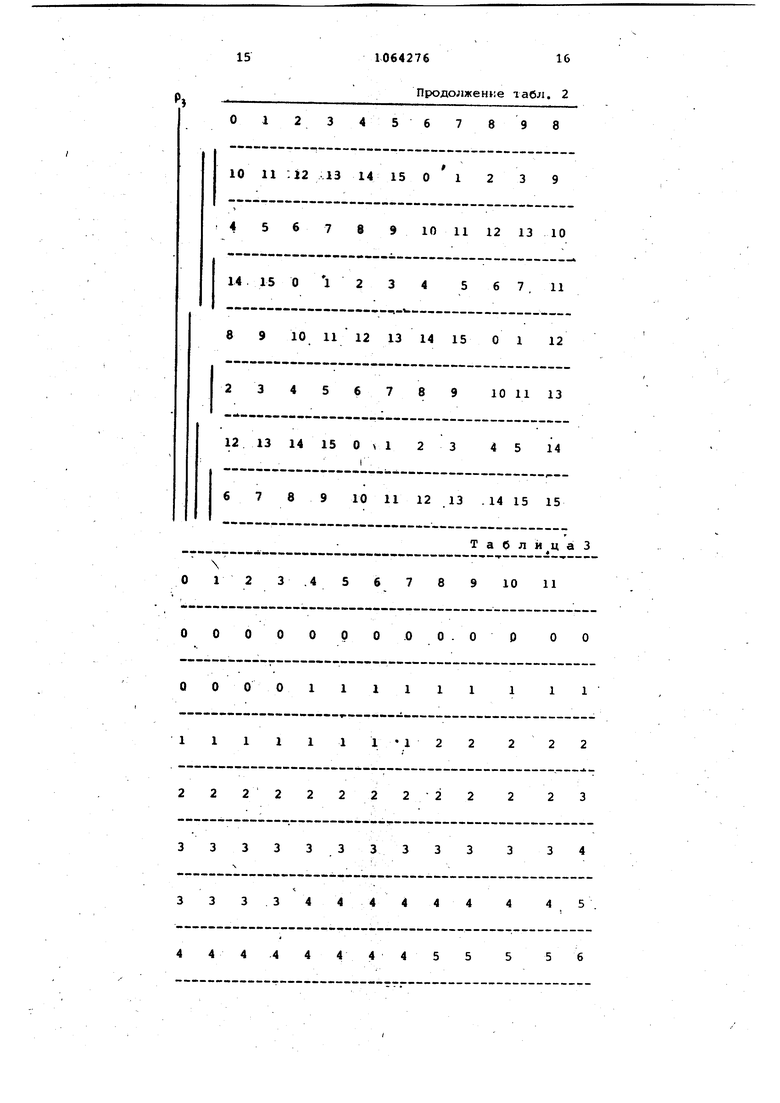

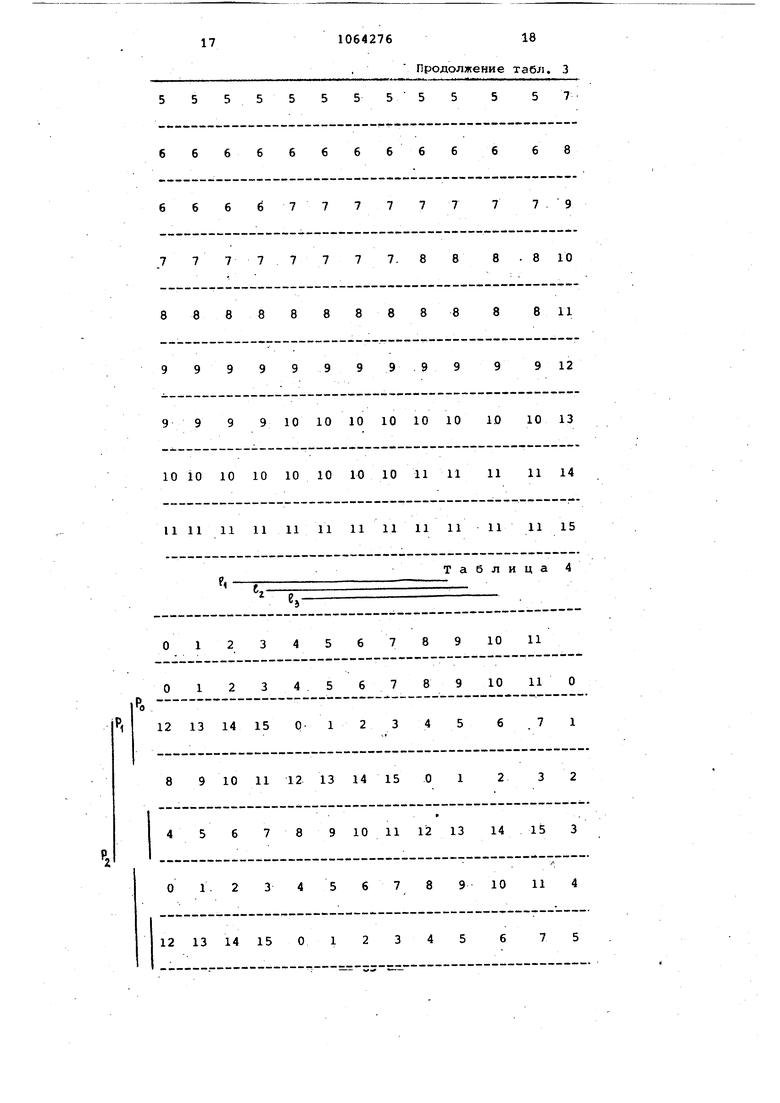

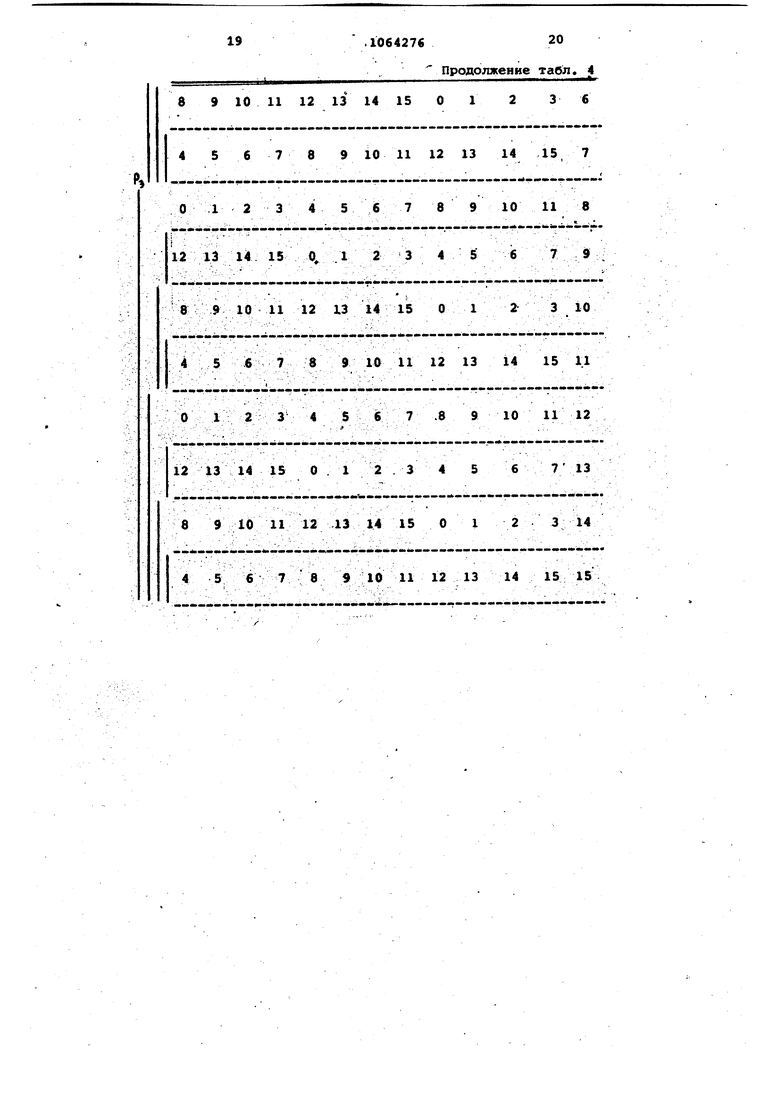

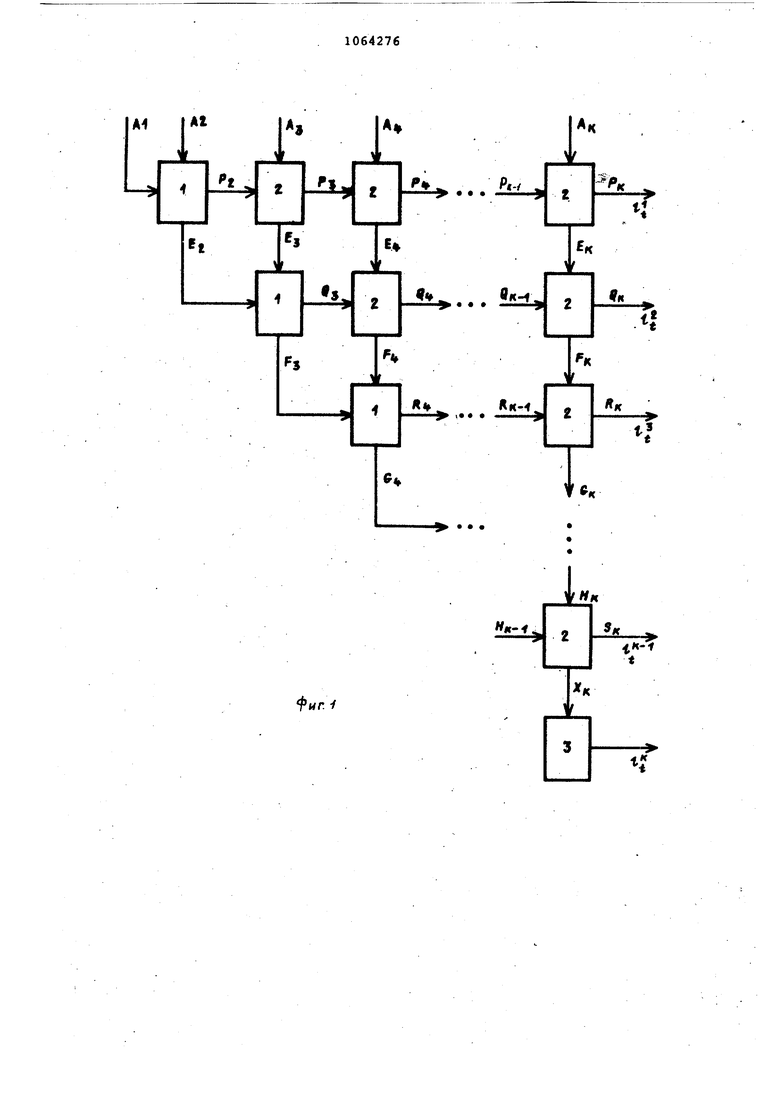

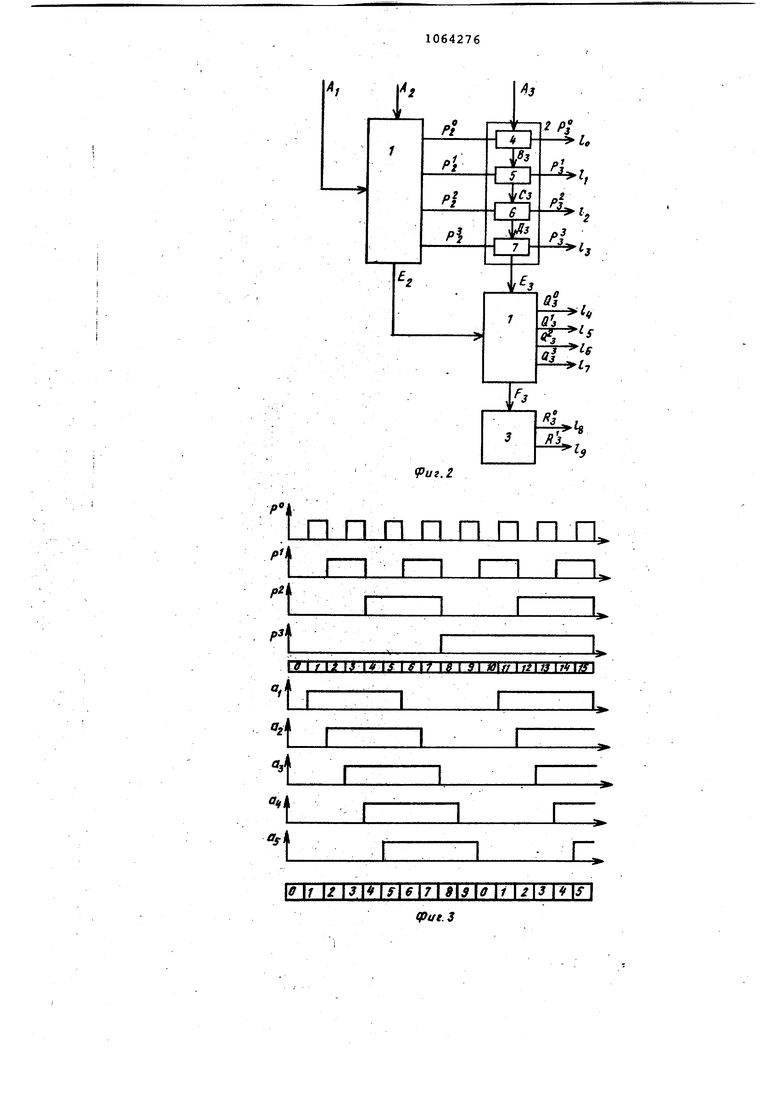

Q Недостатком указанного устройстI за являются невысокое быстродействие и большие аппаратурные затраты. Наиболее близким к предлагаемому ,является преобразователь позиционАс ного кода в двоичный код, содержа1ДИЙ треугольную матрицу делителей, разрядные входы делителей первой строки которой соединены с входами преобразователя, выходы которого соединены с выходами последнихделителей всех строк треугольной матрицы 2 . Недостатки известного преобразователя состоят в относительно низком быстродействии и большом объеме аппаратуры. Цель - повышение быстродействия преобразователя. Поставленная цель достигается те что преобразователь позиционного ко да в двоичный код, содержащий треугольную матрицу блоков деления, пе вые входы делимого блоков деления первой строки которой соединены с входами преобразователя, выходы всех разрядов преобразователя кроме старшего,.соединены с выходами част ного последних блоков деления всех, строк треугольной матрицы, в 1-й; строке которой (1 1-К-1, где К - число разрядов входного кода5, выход частотного j-ro блока деления {j 2-К-1) .соединен с вторым входом делимого (j+l)-ro блока деления i-й строки, а выход остатка соединен с Первым входом, делимого (j-l)-ro бло ка деления (1+1)-й строки,выход остатка первого блока деления i-й строки соединен с вторым входом делимого первого блока деления (1+1)строки, содержит дополнительный делитель на 2 (где t удовлетворяет условиям п 2 , п -основание сис темы счисления входного кода, а каж дый из блоков деления треугольной матрицы выполнен в виде делителя на 2, причем выход старшего разряда преобразователя соединен с выходом частного дополнительного делителя на 2,первый вход делимого которого соединен с выходом остатка блока деления на 2 .К-й строки матрицы. Кроме того, делитель на 2 содер жит- первый и второй дешифраторы пятифазного кода, четыре группы элеме тов И по пять в каждой группе, пяту группу из пяти двухвходовых элеменг тов И, шестую группу из четвертых трехвходовых элементов И, седьмую группу из восьми четырехвходовых элементов И и семь элементов ИЛИ, входы которых соединены с выходами элементов И соответствующих групп, прямые и инверсные выходы первых четырех элементов ИЛИ являются соот ветственно прямыми и инверснь1ми выходами остатка делителя на 2 , прямые и инверсные выходы пятого, шее-: того и седьмого -элементов ИЛИ являются соответственно прямыми .и ин.верснымр выходс1мй частного делите(ля на 2 , первые вхЪды делимого которого являются входами первого и второго дешифраторов пятифазного кода, прямой вход первого разряда второго входа делимого делителя на 2 соединен с первыми входами первых элементов И с первой по седьмую группы, .первыми .входами второго и третьего элементов И пятой и седьмой групп, гГервым входом второго элемента И шестой группы и первым входом четвертого элемента седьмой группы, инверсный вход первого разряда второго входа делимого делителя на 2 соединен с первыми входами вторых элементов И с первой по четвертую групп, четвертого и пятого элементов И пятой группы, третьего элемента И шестой группы и с первыми входами с пятого по седьмой элементы И седьмой группы, первый вход четвертого элемента И шестой группы соединен с прямым входом второго разряда второго входа делимого делителя на 2, вторые входы всех элементов И пятой, шестой и седьмой групп соединены с соответствующими выходами второго дешифратора пятифазного кода, прямой и инверсный выхода которого являются прямым и инверсным выходами частного делителя на 2, прямой вход второго разряда второго входа делимого делителя на 2 соединен с первыми входами третьих элементов И первой и групп, вторыми входами первых элементов И второй и четвертой групп, четвертого элемента И четвертой группы, третьими входами вторых элементов И шестой и седьмой групп и третьими входами четвертого, шестого и восьмого элементов И седьмой группы, инверсный вход второго разряда второго входа делимого делителя на 2 соединен с первыми входами четвертого элемента И первой группы, третьего элемента и второй и четвертой групп, вторыми входами вторых элементов И первой и третьей групп, третьими входами первого, третьего и четвертого элементов И шестой группы и третьими входами первого, третьего, пятого и седьмого элементов И седьмой группы,-прямой вход третьего раэряда второго входа делителя делимого на 2 соединен с первыми входами пятого элемента И первой группы, четвертых элементов И второй, третьей и четвертой групп, с вторыми входами первого и третьего элементов И третьей группы, третьим .входом первого элемента И четвертой группы и . четвертыми входами третьего, четвертого и седьмого элементов И седьмой группы, инверсный вход третьего разряда второго входа делимого делителя на 2 соединен с первыми входами пятых элементов И второй,третьей и четвертой групп, вт.орыми входами четвертого элемента И первой группы третьего элемента И второй группы, третьим входом второго элемента И первой группы и четвертыми входами первого, второго, пятого и шестого элементов И седьмой группы, прямой вход четвертого разряда второго вхо да делимого делителя на 2 соединен с вторыми входами второго, третьего и пятого элементов И четвертой группы, пятых элементов И второй и третьей групп,третьим входом второ, го и третьего элементов И второй группы, второго элемента И третьей группы, четвертого элемента И первой группы и четвертым входом втоtioro элемента И первой группы и является прлмым выходом остатка делителя на 2, инверсный вход четвертого разряда второго входа делимого делителя на 2 соединен с вторыми входами первого, третьего и пятого элементов И первой группы, четвертых элементов И второй и третьей групп, третьими ходами первых элементов И второй и третьей групп, третьего элемента И третьей группы, четвертого элемента И четвертой гру пы и четвертым входом первого элеме та И четвертой группы и является инверсным выходом остатка делителя на 2, первый, второй, третий и чет вертый выходы первого дешифратора пятифазного кода соединены соответственно с четвертыми входами первог элемента И второй группы, четвертых элементов И четвертой и пергой груп второго элемента И третьей группы, пятый, шестой, седьмой и восьмой вы ходы дешифратора пятифазного кода соединены соответственно с третьими входами первого элемента И первой группы, четвертого элемеита И треть ей группы, пятого элемента И второй группы и второго элемента И четвертой группы. На фиг. 1 изображена .функциональ ная схема преобразователя k-разрядного кода с основанием в двоичный код; на фиг. 2 - схема преобразователя трехраэрядного пятифаэного кода в двоичный код; на фиг. 3 сигналы остатка Р, представлейные в двоичном коде, которые выполняют функцию сигналов переноса в строках матрицы делителей, и соответствующие им цифры десятичного кода О, 1, 2,..., 15; на фиг. 4 и фиг. 5 блок-схема делителя на 2. На вход преобразователя (фиг.1) подается К-разрядное число А, представленное в коде с основанием п. Блок деления 1, выполненный в виде делителя на 2, осуществляет деление на 2 двух старших разрядов А |и Aj, причем t удовлетворяет уелоВИЮ 2 i; п 2, На выходах долитс ля 1 формируются частное Е и перенос Р . Затем блок 2 деления,, выполненный в виде делителя на 2 делит ; на 2 разряд А с учетом переноса Pij и на выходе делителя 2 формируются частное E-j и перенос Р и т.д. до Ац. Полученный после первого деления на 2 перенос Р. преобразуется в t разрядов двоичного кода последним делителем на 2 верхней строки матрицы. Аналогичным образом осуществляется следующий этап деления, для чего на делитель 1 второй строки матрицы подаются сигналы Е и Е и на выходе этого делителя формируются частное F и перенос .Q, затем осуществляется деление Е с учетом Q и т.д., -а остаток преобразуется в t разрядов двоичного кода последним делителем второй строки матрицы. Последовательное деление на 2 осуществляется делителями строк матрицы до тех пор, пока частное от последнего деления X ) не будет меньше 2 . С помощью отдельного делителя 3 осуществляется преобразование Х в двоичный код. Преобразователь пятифазного кода в двоичный (фиг. 2) состоит из делителей 1 и 2, обр 1зующих треугольную матрицу, каждый из которых осуществляет деление на 2 6, и делителя 3. Основание кода (, m - число фаз многофазного кода) выбрано как наиболее распространенное и удобное для рассмотрения принципов построения преобразователей. Делитель 1 производит деление двух разрядов пятифазного кода Aj| и Aj, Е и 16 и формирует сигналы частного и , представленные в пятифазном коде, и сигналы переноса Р и последующий делитель строки матрицы, которые представляют собой четырехразрядный двоичный код. Делитель 2 делит на 16 третий разряд А с учетом переносаР. Второй выход Ej делителя 2 подключен к второму входу делителя 1 второй строки матрицы, на первый вход которого подаются пятифазные сигналы Е с второго выхода дгелителя 1 первой строки. Двоичные сигналы Q с первого выхода делителя 1 второй строки матрицы подаются на выходы t, tf, tи tf преобразователя. Второй вйход делителя 1 второй строки подключен к входу делителя 3, выходы которого соединены с выходами t и 9 преобразователя. Делитель 3 преобразует пятифазный сигнал F в два разряда двоичного кода, поскольку для преобразования максимального трехразрядного десятичного числа в двоичный код требуется не более десяти двоичных разрядов. Каждый из делителей 1 и 2 можно представить в виде четырех последовательно соединенных делителей 4-7 (фиг.. 2) , осуществляющих деление на два. Каждый из делителей 4-7 делит на два множество цифр пятифазных сигналов А-/ В, С, D с учетом соответствующего сигнала переноса PJ , Р, Р Pf На двоичном выходе делителей на два Формируются .сигналы переноса Pj, Pj, Р|-, pj в последующий делитель данной строки матрицы, д на втором выходе - пя тифазные сигналы В, ного.. г ; Используя фиг 3, на которой,изо ражены сигналы двоичного кода Р и сигналы пятифазного кОда а , а,.. ау, получают логические выраже(Ния для сигналов переноса Рл и пятифазных сигналов частного Е., которые формируются делителем 2 (фиг. 2) на шестнадцать. Сигнал переноса первого разряда Р Представляет собой множество нечетных чисел сигнала А-З, которые обозначень М, 3, 5, 7, 9. Действительно, только тогда, когда де лятся на ДЕе нечетные цифры пятифаз ного сигнала А ; Таким образом, ,5,7 .+ а а +Сигнал в первой фазы В представляет, собой мнржестврцифр М ч 15 1Ь+2Ь + . . .+5ь. При отсутствии р| сигнал в 1 при делении на два множества цифр MS .., 4. сигнал для М , так как деление с учетом перенрса означает деление на два чисел Ю.д и Ид . Рассуждая аналогич- ным образом, получакгг B,M .....9 +Й..9 В2., +PSM5 ....+. ...,, .-4-9 ,,+ Р-М,; , где Mof... +9 Moti; 4+,,,1-i) Мо4-.. М...4, M,,,.,5 flt9 .л Сигнал переноса второго делителя.на два с учетом (1) ,В2+В)В4+ В, B5+BjB5+B4B5. Подставляя (2) и выполнив преобраз вания, получают I (м,%э+м2,7)+р; (MOI- W S J.M. - Сигналы фаз С можно выразить через множества цифр сигналов В, используя (21 . ... t9 3+ 11.. + q ч-9 + 9 Учитывая, что. М2....9 В2+В5 } M|,..t9 B4+Bs ; М««,., Bg ; , и выполнив преобразования, имеют c,«p;(,...,q)p;p°w 5...qc,p;(pf+M,,).,,j C3 PlP...(W$,.,,, (4) ...,...,9). Ce-PiСигнал переноса третьего разряда Р представляет собой множество нечетных цифр сигналов С, т.е. Pl C Cz+C3 4 + + C3C5+C,C5 PUP...T P°M2i...s (5) РЧР...,,.,...,д). Аналогичнкгм-образом можно получить сигналы фаз с1,(, d,..., dj и сигнал nei/еноса четвертого разряда Pj, который представляет собой множество нечетных цифр сигналов D. Затем, выражая сигналы фаз Е через D, нетрудно получить логические формулы для сигналов фаз е,..,, е, как функции сигналов А и Р. Опуская промежуточные преобразования, записывают логические формулы для сигналов фаз Е и сигналов переноса Р для -того делителя на шестнадцать. ......... е.Р;ЛР.,РД;С....9)РДР.,Ш,...,,1., ..,. ,Р,Р:ДР°,ш;,...„)Р,(Р1.,-еР°,....49)-, е5--Р м- .(65 riO-M . i.T5,7.9 Р; Pr.)Pt.i«.i.6-.9) Р- р;.,....,рГм wi...5Hp;-,(...trr ....5); Р; РИ -ДР°. 5 Р-(p°,м,...,,,..л91 p 4p чГp°1Л8. ,-bpt,Mt...,)p;......... На основе (6) и (7) составляют таблицы чисел размерами 10x16 Клеток, в каждой клетке которых записа но одно число (фиг. 4). Табл. 1 пред назначена для определения множегства цифр сигналов Е и заполняется слева .направо и сверху вниз цифрами от О др 9 по 16 одинаковых цифр подряд. Для определения множества, например, сигнала е, -нужно иметь в виду, что е пятифазного кода состоит из цифр 1, 2, 3, 4 и 5 (фиг. 3). Множество BI выделено в табл. 1 утолщенной линией. .Аналогичным образом можно определить множество ej, которое состоит из цифр 2, 3, 4, 5 и 6 и т.д.

Каждое множество е, представляет собой площадь плоскостной фигуры

с

табл. 1, которую нетрудно определить при помощи сигналов пятифаэного кода (сигналы частного) и сигналов двоичного кода (сигналь переноса) , которые изображены рядом с таблицами на фиг. 4. Таким образом, табл. 1 позволяет получить аналитические выражения. (6) без вывода и промежуточных преобразований.

Таблица 2 (фиг. 4) предназначена для определения сигналов переноса. Она заполняется слева направо и сверху вниз числами О/ 1, 2,...15. Порядок заполнения таблицы следующий: О, 1, 2,..., 14, 15, О, 1, 2 И т.д. Из этой таблицы несложно получить множество всех сигналов переноса. Например, сигнал переноса третьего разряда состоит из цифр 8, 9,..., 15. Объединяя эти цифры в табл. 2, получим множество рЗ {обведено утолщенной линией и заштриховано ). Эта. таблица т 1кже позволяет получить выражения для сигналов переноса (7) без промежуточных преобразований

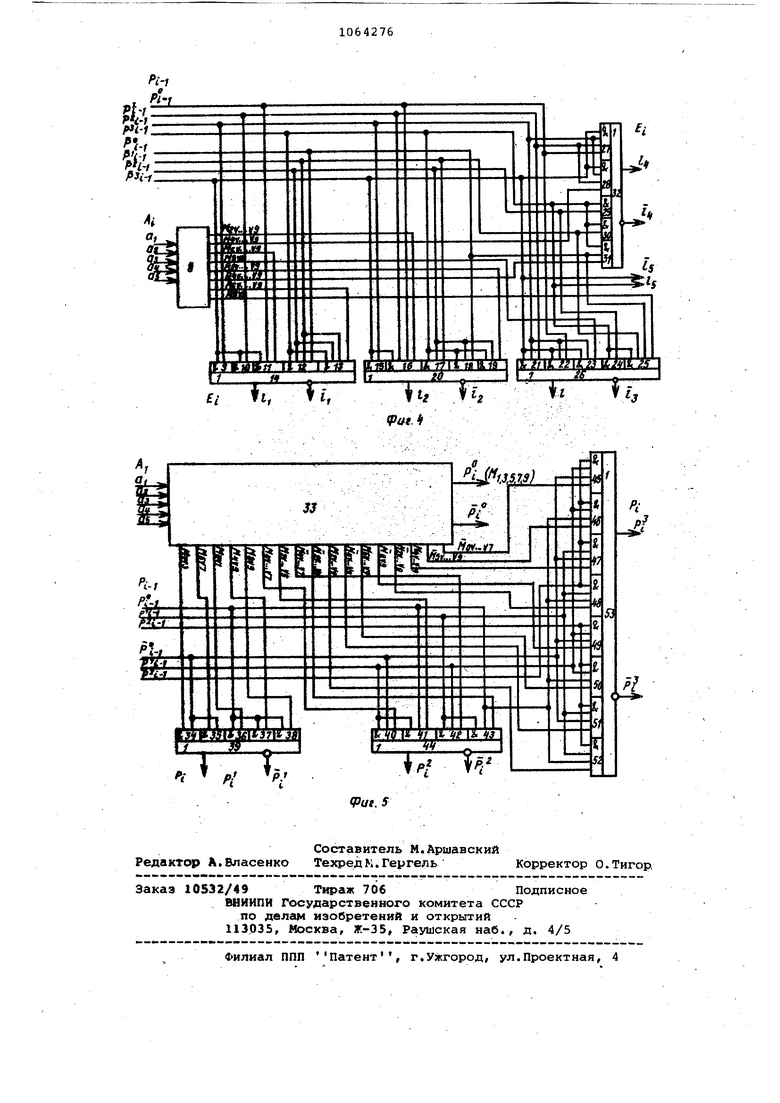

Используя выражения (6) и (7) , каждый делитель на 16.можно представить в виде двух блоков - блока формирования частного (сигналов Е) и блока формирования переноса или остатка (сигналы Р). Делитель на 2 (фиг. 5) состбит из первого дешифратора 8, пятифазного кода, элементов И 9-13, элемента ИЛИ 14, элементов И 15-19, элемента ИЛИ 20, элементов И 21-25 элемента ИЛИ 26, элементов И 27-31, элемента ИЛИ 32.

Элементы И 9-13,15-19,21-25,27-31 образуют четыре группы элементов И.

Дешифратор 8 формирует множества цифр сигнала А, участвующие в формировании сигналов Е

М51„,+ а,2+а5 г

.+ч a4+as

. ау ;

. .(8) м а . а .

Дешифратор 8 имеет пять вxoдoв на которые подаются фазы разряда либо входного числа А, если данный делитель расположен в верхней строке матрицы (фиг. 2), Либо сигналы частного с предыдущего делителя данного столбца матрицы. .Восемь множеств цифр с выхода дешифратора подаются на входы соответственно элементов И 16, 28, 11, 23, 19, 31, 13, 26, на другие входы которых, а также на входы остальных элементов И подаются прямые и инверсные сигналы переноса с предыдущего делителя нА 16 данной строки матрицы делителей. Сигналы переноса представлены в двоичном коде. Выходы элементов И каждой группы объединены пятивходовыми элементами ИЛИ, прямой и инверсный

выходы которых являются выходами одной из фаз частного. Выходы сигналов пятой фазы 6, ..

Формирование сигналов переноса в . с делителе на 2 реализующее (7) осуществляется при помощи второго дешифратора 33 пятифазного кода (фиг.55 трех элементов И 34-38, элемента ИЛИ 39, элементов И 40-43, элемента - ИЛИ 44, элементов. И 45-52 и элемента ИЛИ 53. На вход дешифратора 33 подаются пятифазные сигналы а, а, а, а , aj. Формирование мнохеств на выходе дешифратора осуществляется по формулам.

Х Л - .А

J .j;

...+Ч

в -

И М

мЬ,.,.

а.а.

2i.-t5

Формирование остальных мно :еств осуществляется по формулам (8). Выходы

0 элементов И каждой груПЛы объединены элементами ИЛИ, на выходах которых формируются сигналы переноса Р , Р , р|, Р, Р-, в следующий делитель данной, строки матрицы. Сиг5 нал переноса р|, ipf младшего двоичного разряда формируетс,я в дешифраторе по формуле (1).

Делитель 1 (фиг. 2) отличается. от рассмотренного тем, что на оба

Q его входы подаются пятифаэные сигналы. Поэтому таблицы (фиг. 4) для такого делителя имеют размеры 01X10 клеток и представляют собой верхнкно часть таблиц фиг. 4. Логические вы5 ражения, описывающие этот делитель, можно получить из (6) и (7), вьфазив Сигналы переноса через сигналы пятифазного кода. Для этого можно использовать Фиг. 3, либо подставить

П 7) р.,,о. ,

Делитель 3 (фиг. 2) осуществляет преобразование пятифазных сигналов F с выхода делителя предыдущей строки матрицы в два разряда двоичного кода tg и f . Поскольку вход перено5 са у делителя 3 отсутствует, то Рл Рй Р Р 0 и выражения (7) щ

- - 5 Pi -2принимают вид

.R° ee-f,iVi3i n,542f.s4C,f5-,

R, 9-l2f4 iil3l

где f -фазы сигналов Fj .

Преобразователь пятифазного кода в двоичный (фиг. 2) работает следующим образом.

Пусть на вход преобразователя подано десятичное число , т«е. , , . Делитель 1 первой строки матрицы осуществляет деление двух старших разрядов, т.е. .числа 93 на 16. Откладывая цифру 9 по вертикали, а цифру 3 по горизонтали, находим Е4,5 (табл. 1). Таким же образом (табл. 2-) определяем, что

, т.е. , , . Делитель 2 делит число 135 на 16. По таблицам определяем, что , . Значения сигналов Р. представвторОйстроки матрицы делит на 16 число 58. По таблицам находим Fj 3, , .т.е. ,,- . Делитель 3 преобразует F в два разряда выходного кода RI . Итак, полученное двоичное число 1010 0111. Построение трехраэрядногс преобразователя шестифаэного кода () в двоичный код, показано на фиг. 2« Определяют последовательность операций при построении преобразователей кода любого вида с любым основанием в двоичный код. На основании общей функциональной схемы (фиг. 1) определяют функциональную схему устройства (фиг.2) Выбирают вид кода, в котором будут представлены сигналы Е .В, F шестифазный код. Сигналы переноса всегда представлены в двоичном коде .Определяют t из условия 2 . В данном случае . Составляют таблицы размерами () чисел для определения сигналов частного и переносаг Таблицы для преобразователя шестифазного кода в двоичный приведены на фиг. 7. Заполнение их производится таким же образом, как и таблиц фиг. 4, с учетом другого основания кода. По таблицам фиг. 7 определяют мно жества сигналов Б и Р, записывают логические выражения этих сигналов. По Логическим вкфажениям строят прин ципиальные схемы блока формирования частного и блока форМ1фования переноса (Ьстатка), из которых состоят делители матрицы Т 4. б JI и ц а 1 .. :....ll;;z--ZZT 01 2 3 45 6 7 89

00 00 о 00 00 о

00 о о о 011 111

2 22 2

55

3 3 3 3 4 44444

44444444

60

5 5 55 55

5 5 Опредедяют количество разрядов Z выходного двоичного числа из условия , где к - количество разрядов преобразуемого числа. В рассмотренном примере . Определяют количество двоичных разрядов на выходе делителя 3 по формуле (K-l) . Записывают логические выражения для делителей 1 и 3, которые определяют их принципиальные схемы. Преобразуют в двоичный код число .11.10, представ пенное в коде о основанием 12 (в десятичном коде ). Для делителя 1 первой строп к и матрицы по таблицс1М определяют , Pg 11. Делитель 2 осуществляет деление числа 11.10 на шестнадцать. По таблицам находим , . Для делителя 1 вторые строки матрицы (входное число 6.8) , . Выходное число преобразователя i:, 101 0000 1110. . При использовании предлагаемого устройства упрощение преобразователя достигается путем уменьшения количества этапов последовательного деления преобразуемого числа в t раз. Кроме того, формирование сигналов переноса каждым делителем, ко;торые для последнего.столбца.маФрАШЫ делителей являются выходнъми сигналами преобразователя, осуществляется в двоичном коде. Каждый делитель в предлагаемом преобразователе представляет собой трехуровневую комбинационную логи- , ческую.схему. Максимальное количество логических уровней в преобразователе (фиг. 2) равно 10, следовательно, время преобразования при использовании микросхем быстродействующих серий будет составлять 100-150 мс, что по сравнению с известным преобразователем обеспечивает повьпиение быстродействия. тродолжение таб«. 1 2222222233 4 3333333333

13

Продолжение табл.1

5555556666 9

6 6 6 6 6 6 6 6 6 6 10 6 6 7 7 7 7 7 7 7 7 11 777777778812 8 .8 8 888 888 8 13 888 8 9 99 99 9 14

. 999999999-9 15 012 3 4 56789

р° О 1 23 4 5678 9 О Р, 10 И 12 13 14 15 О 12 3 1 4 56789 10 11 12 13 2

14 15 01 .2 3 4 56 7 3

8 9 10 11 .12 13 14 15 О 1 4

2 345 6 7 8 9 10 11 5 12 13 14 15 О 1 23 4 56, 6 78 9 10 11 12 , 13 14 15 7

10642761 4

Т .а б лиц а 2

О 1 2 3 456 7 8 9 8

10 11 .12 13 14 15 О 1 2 3 9

4 5 67 8 9 10 11 12 13 10

8 9 10 11 12 13 14 15 О 1 12

23456789 10 11 13

12 13 14 15 О ч 1 2345 14

67 89 10 11 12 13 .14 15 15

N О 1 2 3 .4 5 6 7 а 9 10 11

000000000.0000

О 0001 1 1 1 1 1 1 1 1

1 1 1 1 1 1 222 2

2222222222 2 23

3333333333 3 34

3 3 33 4 44 4 44 4 45

4 44 4 4 4445 5 5 5 б

Продолжен1 е табл. 2

ТаОлй цаЗ

17

5 5 555 5 5 5 5 5 5 57

6666666666668

6 6 6 677 7 7 77779

7 7 111 7 7 7. 8 88- 8 10

8888888888 8 811

9 99 9 99 999999 12

99 9 9 10 10 10 10 10 10 10 10 13

10 10 10 10 10 10 10 10 11 11 11 11 14

nil 11 111111 11 nil 11 11 11 15

0123456 7 89 10 11

О 1 2 345 67 8 9 10 11 О

12 13 14 15 Q 1 2 3 4 567 1

8 9 10 11 12 13 14 15 О 1232

45 6 7 8 9 10 11 12 13 14 15 3

О 1. 2 3 45 67 8 9 10 11 4

12 13 14 15 О 1 2 3 4 56 75

106427618

Продолжение табл. 3

Таблица 4

19

8 9 10 11 12 13 14 15 О 1 2 3 6

4 5678 9 10 11 12 13 14 15 7

1 2 3 4 5 б 78 91011 8

. -. - - .- ......

13 14 15 «t I г 3 4 g(579

9 10 11 12 U 14 15 0123 10

5 V 7 8 9 10 1112 131415 11

-- . . . 1 -.--. . ....

1234 5 is 7.8 91011 12

-.- .- - ....-. f .....:--.- - .

13 14 15 О 1 2 34 567 13

9 10 11 12 13 14 15 0123 14

5 67 8 9 10 1112 131415 15

.106427620

Продолжение табл. 4

Г Г- Г

М I А

Е л

иг

р,

-/

If

... «/«н

««

tj

я Лк-Ч,

1

«л

1 /

fi

П П П П П П П П.

p3k

t TTflf FJ I 15 iff 17 lg I ЯЛ

Of I

3

г Р

1с

n

1

(Put. 3

pi-1

Pt-r

И,

ft УН:

t, Ji,

f

t7

.:« p/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| Л-- . ^ - .. -.^nsTfy-;-;:.-; , ,. ^lii-i i _i; i iiCi" . . ,. ,BHb/.hoО. Ф. Лобов | 0 |

|

SU317061A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

Авторы

Даты

1983-12-30—Публикация

1982-01-29—Подача