со

00 N3

30

Изобретение относится к вычислительной TexraiKe, в частности к запоминающим устройствам на нилиндричес- ких магнит ных доменах (1ЩД) со, средствами коррекции ошибочной информации .

Целью изобретения является повышение надежности устройства за счет .введения режима исправления одиноч- Iных постоянных оишбок без перезаписи информации.

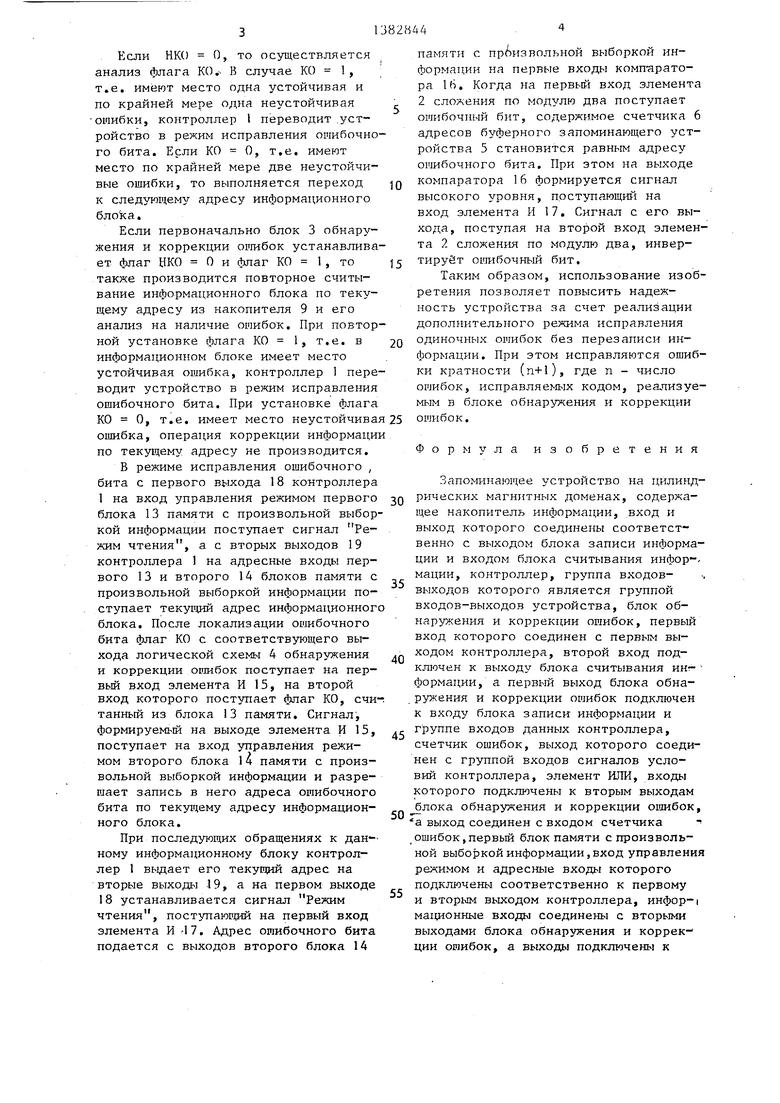

На чертеже представлена структурная схема запоминающего устройства на НМД.

Запоминающее устройство на ЦМД содержит контроллер 1, элемент 2 сло I жения по модулю два, блок 3 оПнаруже I ния и коррекции ошибок, включающий I в себя логическую схему 4 обнаруже- j ния и коррекции ошибок, буферное за- I поминающее устройство 5, счетчик 6 I адресов буферного запоминающего устройства и элемент 7 сложения по модулю два, блок 8 записи информации, накопитель 9 информации, блок 10 считывания информации, элемент ИЛИ 11, счетчик 12 ошибок, первый 13 и второй 14 блоки памяти с произвольной выборкой информации, первый эле- мент И -15, компаратор 16, второй элемент И 17. Контроллер имеет первый 18, вторые 19 и третий 20 выходы, группу входов 21 данных, группу входов 22 сигналов условий.

Кроме того, устройство имеет группу входов-выходов 23.

Устройство работает следующим образом.,

В режиме записи информационный блок с входов-выходов 23 устройства поступает в контроллер 1 , затем с . третьего выхода 20 контроллера передается на вход элемента 2 сложения по модулю два, с выхода которого данные передаются в блок 3 обнаружения и коррекции ошибок, где формируются контрольные разряды, С первого выход блока 3 обнарз ения и коррекции ошибок данные поступают на вход блока 8 записи информации, с выхода которого данные заносятся в накопитель 9.

В режиме чтения информационный блок считывается из накопителя 9 и поступает через блок 10 считывания информации в блок 3 обнаруке1нгя и коррекции оршбок. Далее по группе вх ДОН 21 данные заносятся в контооллео

Q

5

0 5 0

5

Q

0

5

1 и передаются на группу входов-выходов 23 устройства.

В случае обнаружения огиибки в информационном блоке на одном из вторых выходов блока 3 обнаружения и коррекции появляется флаг (сигнал логической 1) корректируемой оишбки (ко) или некорректируемой ошибки (ЖО). Через элемент ИЛИ 11 эти передаются на вход счетчика 12 ошибок и увеличивают на единицу его содержимое. Кроме того, флаги КО и НКО поступают на соответствующие информационные входы первого блока 13 памяти с произвольной выборкой информации и записываются по те- кутдему адресу, присутствующему на . вторых выходах 19 контроллера

После считывания информационного блока из накопителя 9 в контроллере 1 производится анализ наличия и характера ошибок. Неустойчивой считается огшбка, для исправления которой достаточно повторной операции считывания Устойчивой ошибкой считается такая, для исправления которой необходима перезапись информации. В рассматриваемом примере корректируемой является одиночная ошибка, а некорректируемой - две и более. Вначале в контроллере 1 анализируется флаг восстановления (ФВ) информации, поступающий на группу входов 22 сигналов условий контроллера с выхода счетчика 12 ошибок. Если ФВ 1, то выполняется перезапись информации в информационных блоках, в которых имеют место ошибки и адреса которых хранятг ся в первом блоке 13 памяти с произвольной выборкой информации. Если , ФВ О, то анализируются флаги НКО и КО и, в случае необходимости, происходит исправление информации .

Если блок 3 обнаружения и коррекции ошибок устанавливает флаг НКО 1, то производится повторное считывание информационного блока по теку щему адресу из накопителя 9 и анализ его в блоке 3 на наличие ошибок. Если при этом повторно устанавливается флаг НКО 1, т.е. имеют место по крайней мере две устойчивые ошибки, то по группе входов-выходов 23 устройства из контроллера выдается адрес информационного блока с НКО и сообщение о необходимости перезаписи информации по данному адресу.

Если НКО О, то осуществляется анализ флага КО,- В случае КО 1 , т.е. имеют место одна устойчивая и по крайней мере одна неустойчивая ошибки, контроллер 1 переводит .устройство в режим исправления ошибочного бита. Если КО О, т.е. имеют место по крайней мере две неустойчивые ошибки, то выполняется переход к следующем адресу информационного бло ка.

Если первоначально блок 3 обнаружения и коррекции ошибок устанавливает флаг НКО О и флаг КО 1, то также производится повторное считывание информационного блока по текущему адресу из накопителя 9 и его анализ на наличие ошибок. При повторной установке флага КО 1, т.е. в информационном блоке имеет место устойчивая ошибка, контроллер I переводит устройство в режим исправления ошибочного бита. При установке флага КО О, т.е. имеет место неустойчива О1иибка, операция коррекции информаци по текущему адресу не производится.

В режиме исправления ошибочного , бита с первого выхода 18 контроллера 1 на вход управления режимом первого блока 13 памяти с произвольной выборкой информации поступает сигнал Режим чтения, а с вторых выходов 19 контроллера на адресные входы первого 13 и второго 14 блоков памяти с произвольной выборкой информации поступает текугщй адрес информационног блока. После локализации ошибочного бита флаг КО с соответствующего выхода логической схемы 4 обнаружения и коррекции опшбок поступает на пер- вьш вход элемента И 15, на второй вход которого поступает флаг КО, счи танный из блока 13 памяти. Сигнал, формируемый на выходе элемента И 15, поступает на вход управления режимом второго блока 14 памяти с произвольной выборкой информации и разрешает запись в него адреса ошибочного бита по текущему адресу информационного блока.

При последующих обращениях к дан-ному информационному блоку контроллер 1 выдает его текущий адрес на вторые выходы .19, а на первом выходе 18 устанавливается сигнал Режим чтения, поступаюгцш на первый вход элемента И -17. Адрес ошибочного бита подается с выходов второго блока 14

Q

152025

памяти с произвольной выборкой информации на первые входы компаратора Ih. Когда на первьш вход элемента 2 сложения по модулю два поступает ошибочный бит, содержимое счетчика 6 адресов буферного запоминающего устройства 5 становится равным адресу ошибочного бита. При этом на выходе компаратора 16 формируется сигнал высокого уровня, поступающий на вход элемента И 17. Сигнал с его выхода, поступая на второй вход элемента 2 сложения по модулю два, инвертирует ошибочный бит.

Таким образом, использование изобретения позволяет повысить надежность устройства за счет реализации дополнительного режима исправления одиночных ошибок без перезаписи информации. При этом исправляются ошибки кратности (n+l), где п - число ошибок, исправляемь х кодом, реализуемым в блоке обнаружения и коррекции ошибок.

5 0 5

0

35

40

45

0

5

Формула изобретения

Запом п1аю1цее устройство на цилиндрических магнитных доменах, содержащее накопитель информации, вход и выход которого соединены соответственно с выходом блока записи информации и входом блока считывания инфор-. мации, контроллер, группа входов- выходов которого является группой входов-выходов устройства, блок обнаружения и коррекции ошибок, первый вход которого соединен с первым выходом контроллера, второй вход подключен к выходу блока считывания инт- - формации, а первый выход блока обнаружения и коррекции ошибок подключен к входу блока записи информации и группе входов данных контроллера, счетчик ошибок, выход которого соединен с группой входов сигналов условий контроллера, элемент ИЛИ, входы которого подключены к вторым выходам лока обнаружения и коррекции ошибок, а выход соединен с входом счетчика ошибок,первый блок памяти с произвольной выборкой информации,вход управления режимом и адресные входы которого подключены соответственно к первому и вторым выходом контроллера, инфор-i ма1щонные входы соединены с вторыми выходами блока обнаружения и коррекции ошибок, а выходы подключены к

5 -13828446

группе входов сигналов условий конт-выход первого элемента И подключен к роллера, отличаю PJ; весявходу управления режимом второго бло- тем, что, с целью повниения надежно-ка памяти с произвольной выборкой сти устройства за счет введения режи-информации, компаратор, первые и вто- ма исправления одиночных ошибок безрые входы которого соединены соответ- перезаписи информации, оно содержитственно с выходами второго блока па- второй блок памяти с произвольной.мяти с произвольной выборкой информа- выборкой информации, адресные входыции и третьими выходами блока обна- которого соединены с вторыми выходами 0РЗ ения и коррекции ошибок, второй контроллера, а информационные входы -элемент И, первьш вход которого под- с третьими выходами блока обнаруже-ключен к первому выходу контроллера, ния и коррекции ошибок, первый эле-а второй вход - к выходу компаратора, мент И, первый и второй входы которо-элемент сложения по модулю два, пер- го соединены соответственно с одним 4 свый вход которого соединен с третьим из вторых выходов блока обнарзгжениявыходом контроллера, второй вход - и коррекции ошибок и однимс выходом второго элемента И, а вы- |из выходов первого блока памяти сход подключен к третьему входу блока произвольной выборкой информации, аобнаружения и коррекции ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1985 |

|

SU1273999A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1751762A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

Изобретение относится к вычислительной технике, в частности к за- поминаю1чим устройствам на цилиндрических магнитных доменах со средствами коррекции ошибочной информации. Целью изобретения является повышение надежности устройства за введения режима исправления одиночных постоянных ошибок без перезаписи информации .Устройство содержит контрол- .лер 1,элемент2 сложенияпо модулюдва, блок 3 обнаружения и коррекции ovm- бок, блок 8 записи информации, накопитель 9 информации, блок 10 считывания информации, элемент ИЛИ 11, счетчик 12 оиибо к, первый блок 13 памяти с произвольной выборкой информации, второй блок 14 памяти с произвольной выборкой информации, первьш элемент И 15, компаратор 16, второй элемент И 17. В устройстве обеспечивается дополнительный режим локализации и исправления одиночных постоянных омибок, что позволяет исправлять ошибки кратности (п+1), где п - чис ло ошибок, исправляемых кодом, реализуемым в блоке обнаружения и коррек ции ошибок. 1 ил. с о (Л

Авторы

Даты

1988-03-23—Публикация

1986-10-02—Подача