Изобретение относится к вычисли- тельной технике и может быть исполь- ,зовано для построения аппаратных подпрограмм в универсальных и специализированных системах.

Целью изобретения является повышение точности.

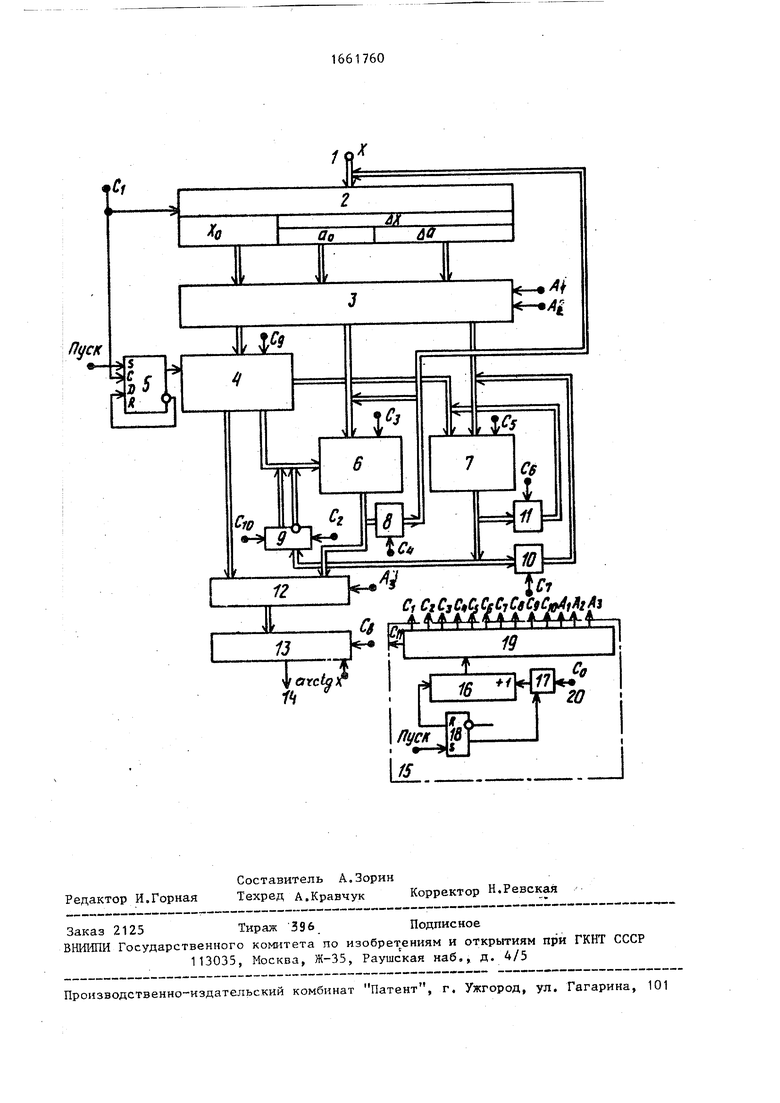

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит вход 1 аргу- мента, регистр 2 аргумента, коммутатор 3, блок 4 памяти, триггер 5, умножители 6 и 7, группы тристабиль- ных формирователей 8.- 11, коммутатор 12, сумматор 13, выход 14, блок 15 синхронизации. Последний содержит счетчик 16, элемент И 17, триггер 18, формирователь 19 управляющих сигналов и вход 20 тактовой частоты.

Устройство работает в соответствии с алгоритмом

arct8X arctR.fllS arctpiXo+jirctga

|-xQa

где а

Дх

Ах

(1+х)+й.ххс

(Л

i52L 45 (1.д к) Г1(4 а)Я 5 1+flx 2j L

Аналогично для величины а

где Ь

1-врЬ

()(Аа7ГГг)(11+а

1+а§

О

а

с&

.

Величины

aretgx можно

-x -Lt- VWe

рассчитать заранее и записать в блоке 4 памяти. Число разрядов адреса блока 4 памяти равно т. В качестве адреса используется величина х0. Выходное слово содержит Зп разрядов. Первая группа из п разрядов составляет первый выход и на нём формируется величина arctgx, вторая руппа Тоже содержит п разрядов и на этом выходе формируется величина т-Ј, на

0 третьем выходе считывается величина

Хо

ТТх|

На вход умножителя 6 с второго выхода коммутатора поступает величи-i на Дх. При этом информация на этом выходе формируется следующим образом. Общее число разрядов равно п. Первые старшие m разрядов обнулены. Следующие m разрядов подключаются коммутатором ко второй группе выходов регистра и последние (п-2п) разрядов подключаются к третьей группе выходов регистра. Третий выход коммутатора полностью аналогичен второму и формирует однотипную информацию. Необходимость в двух каналах передачи связана с необходимостью развязки входов умножителей 6 и 7 при передаче информации с выходов умножителей на вход. В пер вом такте на выходе формирователя 19 управляющих сигналов блока 15 форми

1+х

После снятия сигнале С } и Сд- на выходе умножителей появляется результат умножения, а сигнала Cg в сумматоре 13 - arctgxe. В третьем такте формируются сигналь С3, Су, С4, Св,С С. По этим сигналам в умножитель 6

Дх записывается информация -г- и ,

1+х2л

руется сигнал С и осуществляется за пись аргумента х в регистр 2. Одновременно на управляющие входы коммутатора 3 подаются сигналы А,,АЈ (1,0 При этом на первый вход подается х0, а на второй и третий входы величина Дх аналогично описанному.

Во втором такте формируются сигналы , Сз, Су, Cg (). По перед нему фронту сигналов С3, С5 в схемы умножения записывается следующая информация: в умножитель 6 (--j и их)

х Х°

в умножитель 7 ( и их) и тсд.

Х0

(1-&х---г). Последняя величина форми1 ХО

руется путем инвертирования всех разрядов, кроме знакового (знаковый разряд остается равным нулю). В результате формируется величина

1-Дх7р7 . . 1+х|

но пренебречь.

Погрешностью Т можВ умножитель 7 запишется на оба ,входа один и тот же операнд

Дхт--. Таким образом, в конце тре- +х0,

тьего такта сформируются величины

(y--l) « (1.

Шх1+х U

Т%Ах) и )«,

5

5

0

0

5

В четвертом такте по сигналу С10 величина с выхода умножителя подается на вход умножителя 6, причем знаковый разряд инвертируется, т.е. меняется с нуля на единицу. Умножитель 6 настроен на перемножение кодов, т.е. знаковый разряд рассматривается как значащий с весом , одновременно по С4 и Cj осуществляется запись перемножаемых чисел в умножитель 6.

После выполнения умножения подачей сигналов Сц и С$ результат передается в регистр 2. Полученная величина есть а. Вычисление ведется по приведенному алгоритму. Исключение составляет лишь то, что на управляющие входы поступает код А . При этом на первый выход поступает величина

a$

5

0

Ло

arctga0,

так как она в 2 ип раз меньше, чем то для запоминания величин

1+а|

используется вто1+а

рая страница памяти. Возможность обращения к ней осуществляется записью в триггер 5 единицы. Это происходит подачей сигнала С на счетный вход (сигнал Пуск переводит триггер в 1, запись х в регистр 2 переводит триггер н нуль, а запись величины а - в единицу). На второй и третий выходы коммутатора поступает величина Да, которая формируется следующим образом. Младшие (п-2га) разрядов подключаются к третьему выходу регистра 2, а старшие 2т разрядов отключены, т.е. на них формируется уровень, соответствующий нулю.

Вычисление b ведется в два такта. Дополнительно в первом такте значение arctgae из блока 4 памяти через коммутатор 12 добавляется к предыдущему значению сумматора.

В седьмом такте результат с выхода умножителя 6 поступает на сумматор (А,1) и складывается с содержимым сумматора. Таким образом, arctgx arctgx0+arctga+b. Здесь arctgb b. Достигаемая при этом точность равна .

Формула изобретения Устройство для вычисления функции арктангенса, содержащее регистр аргу мента, первый и второй коммутаторы, блок памяти, блок синхронизации и сумматор, отличающееся тем, что, с целью повышения точности, в него введены четыре группы триста- бильных формирователей, два умножителя и триггер, причем вход аргумента устройства соединен с информационным входом регистра аргумента, выходы старших, средних и младших разрядов которого соединены соответственно с первым, вторым и третьим информационными входами первого коммутатора, выходы с первого по третий которого соединены соответственно с первым адресным входом блока памяти входом первого сомножителя первого умножителя и входом первого сомножителя второго умножителя, выходы с первой по третью групп разрядов блока памяти соединены соответственно с первым информационным входом втброго коммутатора, входом второго сомножителя первого умножителя, выход первого умножителя соединен с вторым информационным входом второго коммутатора и информационным входом первой группы тристабильных формирователей, выход которой соединен с информационным входом регистра аргумента и входом первого сомножителя первого умножителя, выход второго умножителя соединен с информационными входами со второй по четвертую группы тристабильвторого сомножителя первого умножителя, выходы третьей и четвертой групп тристабильных формирователей соединен ны с входами соответственно первого и второго сомножителей второго умножителя, выход второго коммутатора соединен с информационным входом сумматора, выход которого соединен с выходом устройства, вход запуска которого соединен с входом установки в 1 триггера, прямой выход которого соединен с вторым адресным входом блока памяти, инверсный выход триггера соединен с информационным входом триггера, выходы с первого по четырнадцатый блока синхронизации соединены соответственно с входом записи входного регистра, входом разрешения передачи инверсного кода второй группы тристабильных формирователей, тактовым входом первого умножителя, -входом разрешения передачи первой группы тристабильных формирователей, тактовым входом второго умножителя, входом разрешения передачи третьей группы тристабильных формирователей, входом разрешения передачи четвертой группы трист бильных формирователей, тактовым входом сумматора, входом разрешения чтения блока памяти входом разрешения передачи прямого кода второй группы тристабильных формирователей, входом установки сумматора, первым адресным 35 входом первого коммутатора, вторым ад ресным входом первого коммутатора и адресным входом второго коммутатора, вход синхронизации триггера соединен- с первым выходом блока синхронизации,

ных формирователей, прямой и инверс-ч

ный выходы второй группы тристабиль- 40 вход пуска которого соединен с входом

ных формирователей соединены с входом запуска устройства.

0

второго сомножителя первого умножителя, выходы третьей и четвертой групп тристабильных формирователей соединен ны с входами соответственно первого и второго сомножителей второго умножителя, выход второго коммутатора соединен с информационным входом сумматора, выход которого соединен с выходом устройства, вход запуска которого соединен с входом установки в 1 триггера, прямой выход которого соединен с вторым адресным входом блока памяти, инверсный выход триггера соединен с информационным входом триггера, выходы с первого по четырнадцатый блока синхронизации соединены соответственно с входом записи входного регистра, входом разрешения передачи инверсного кода второй группы тристабильных формирователей, тактовым входом первого умножителя, -входом разрешения передачи первой группы тристабильных формирователей, тактовым входом второго умножителя, входом разрешения передачи третьей группы тристабильных формирователей, входом разрешения передачи четвертой группы тристабильных формирователей, тактовым входом сумматора, входом разрешения чтения блока памяти входом разрешения передачи прямого кода второй группы тристабильных формирователей, входом установки сумматора, первым адресным 5 входом первого коммутатора, вторым адресным входом первого коммутатора и адресным входом второго коммутатора, вход синхронизации триггера соединен- с первым выходом блока синхронизации,

5

0

0 вход пуска которого соединен с входом

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для масштабирования | 1989 |

|

SU1649565A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1734102A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании универсальных и специализированных ЭВМ. Целью изобретения является повышение точности, которое достигается введением в устройство, содержащее регистр аргумента, два коммутатора, блок памяти, сумматор и блок синхронизации, четырех групп тристабильных формирователей, двух умножителей и триггера. Точность повышается за счет использования иного алгоритма вычисления. 1 ил.

| Устройство для вычисления обратных тригонометрических и гиперболических функций | 1981 |

|

SU983709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функции @ | 1985 |

|

SU1297041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-07-03—Подача