(Л

со

00

со со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения группы процессоров с группой внешних устройств | 1988 |

|

SU1599865A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1989 |

|

SU1658163A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах, например коммуникационных комплек - сах сетей передачи данных и сетей ЭВМ. Целью изобретения является повышение быстродействия. Устройство содержит узел 6 выборки и группу блоков 5 формирования сигналов обмена. 4 ил.

ф1/2./

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах, например коммуникационных комплексах сетей передачи данных и сетей ЭВМ.

Цель изобретения - повышение быстродействия.

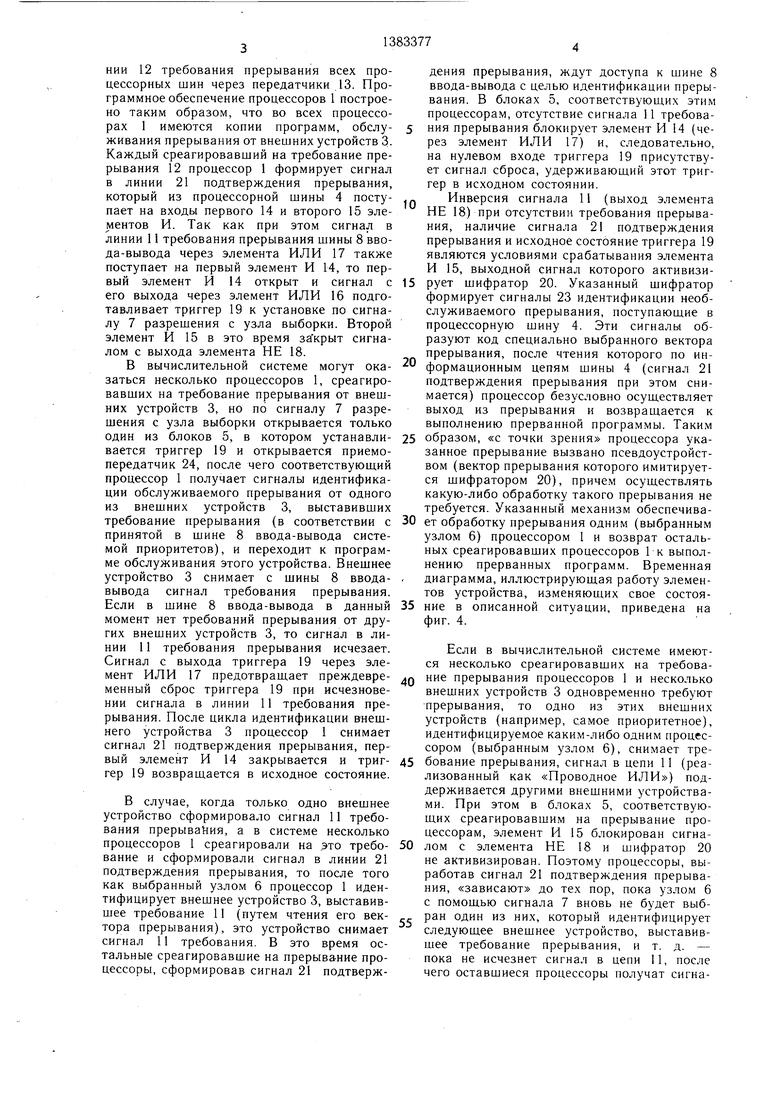

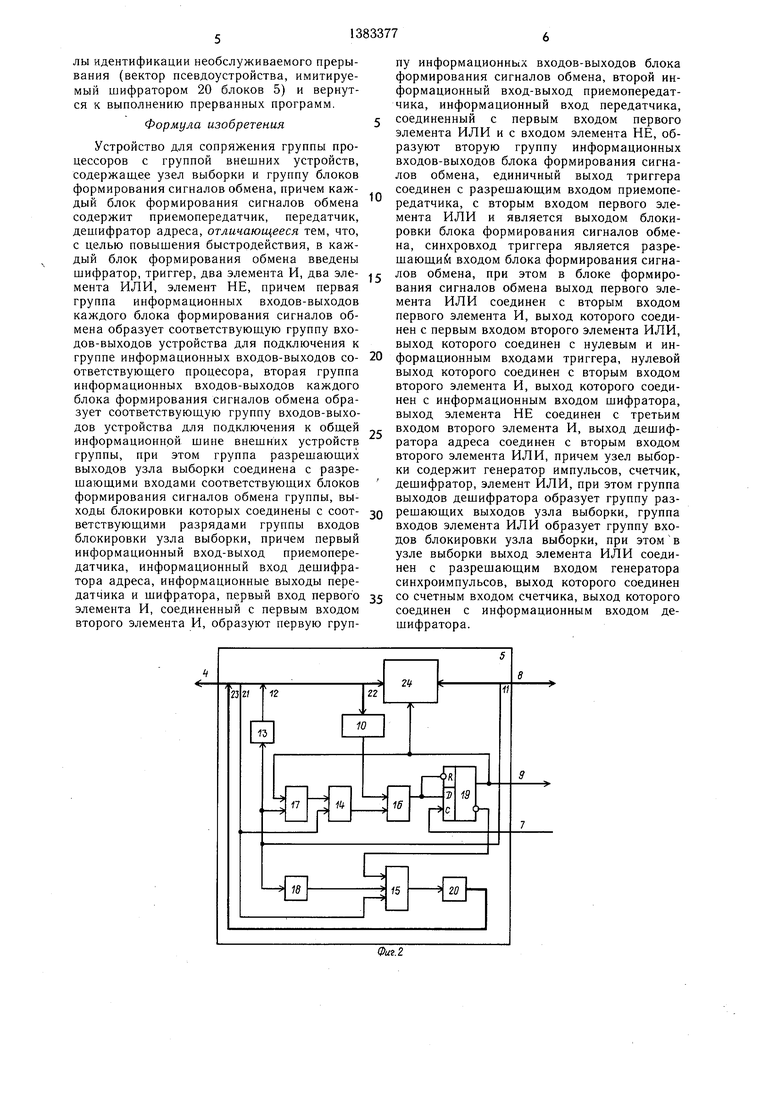

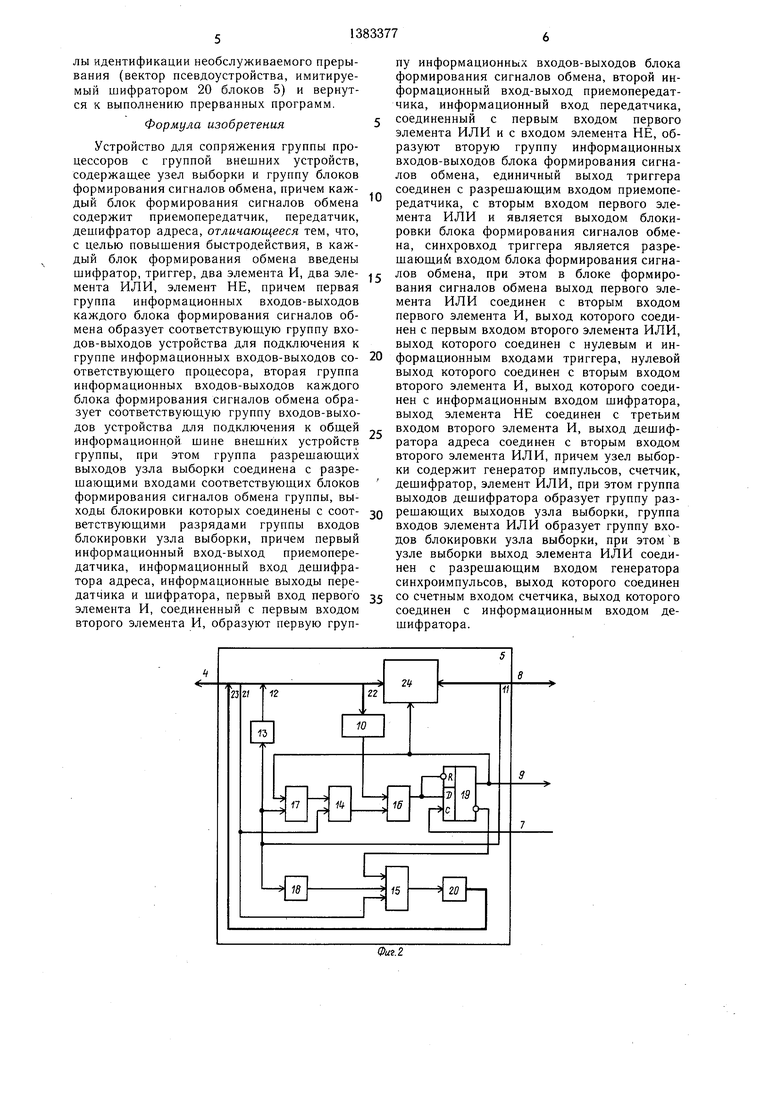

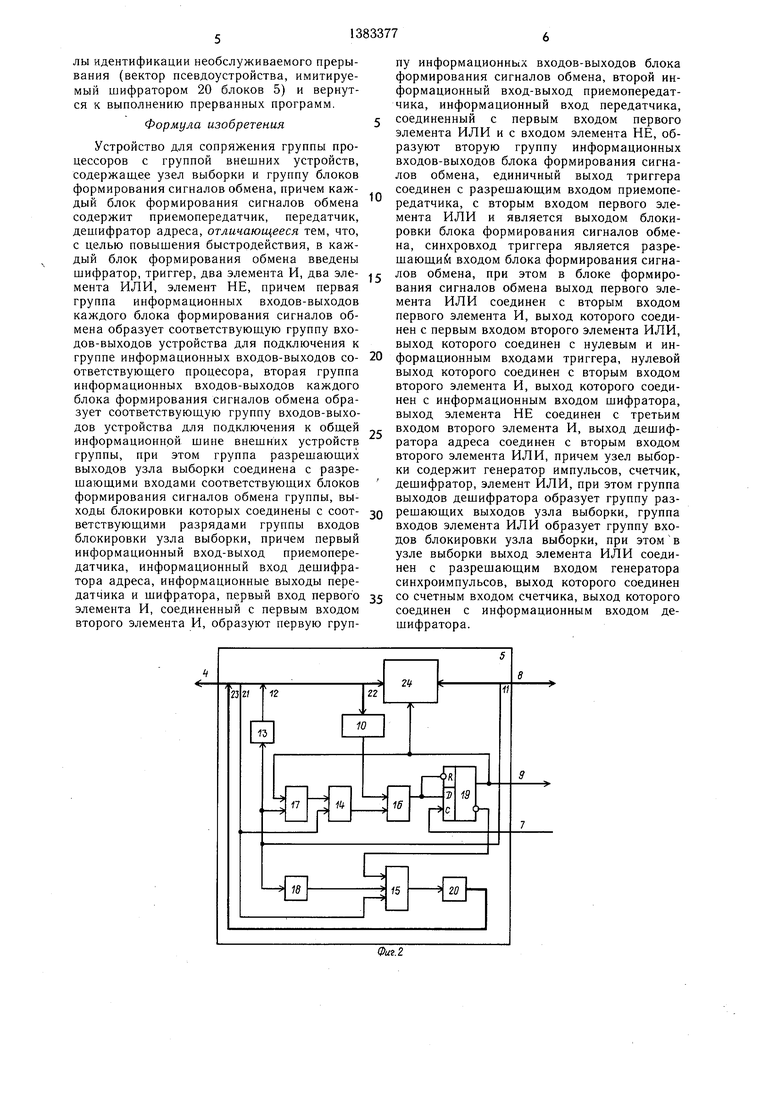

На фиг. 1 представлена структурная схема устройства для сопряжения группы процессоров с группой внешних устройств; на фиг. 2 - структурная схема блока формирования сигналов обмена; на фиг. 3 - схема узла выборки; на фиг. 4 - временная диаграмма, иллюстрируюш.ая работу элементов блока формирования сигналов обмена.

Устройство содержит процессоры 1, устройство 2 для сопряжения, внешние устройства 3, процессорные шины 4, блоки 5 формирования сигналов обмена, узел 6 выборки, линии 7 сигналов разрешения, шину 8 ввода-вывода, линии 9 сигналов блокировки.

Блок 5 содержит (фиг. 2) дешифратор 10 адреса, линию И сигнала требования прерывания шины ввода-вывода, линию 12 сигнала требования прерывания процессорной шины, передатчик 13, первый элемент И 14, второй элемент И 15, второй элемент ИЛИ 16, первый элемент ИЛИ 17, элемент НЕ 18, триггер 19, шифратор 20, служаш,ий для идентификации необслуживаемого прерывания, линию 21 сигнала подтверждения прерывания и линию 22 сигналов адреса процессорной шины 4, информационные линии 23 процессорной шины 4, приемопередатчик 24, предназначенный для соединения процессорной шины с шиной ввода-вывода.

Узел 6 выборки содержит (фиг. 3) генератор 25 импульсов, счетчик 26, дешифратор 27 и элемент ИЛИ 28.

На временной диаграмме позициями обозначены: 29 - график сигнала 11 требования прерывания после элемента НЕ 18 на входе элемента И 15, 30 - график сигнала 21 подтверждения прерывания на входе элемента И 15, 31 - график сигнала на выходе элемента И 15, который вырабатывается при отсутствии сигнала 11, наличии сигнала 21 и исходном состоянии триггера 19, 32 - график сигналов идентификации необслуживаемого прерывания с выхода шифратора 20 (условно показана одна из информационных цепей 23 процессорной шины 4).

Устройство работает следуюшим образом.

Процессоры 1 многопроцессорной вычислительной системы, работая параллельно и независимо друг от друга, могут в произвольный момент времени обращаться к внешним устройствам 3, подключенным к шине 8 ввода-вывода (являющейся обшей для всей системы). При этом дешифратор 10 адреса блока 5, через который инициируется обра0

5

0

5

0

5

0

5

0

5

шение, дешифрирует адрес обращения на линиях 22 сигналов адреса и вырабатывает сигнал обращения, который через элемент ИЛИ 16 поступает на информационный вход триггера 19, подготавливая триггер к установке, а также на нулевой вход триггера, прекращая тем самым сброс триггера 19 управления по нулевому входу.

Конфликт одновременного доступа нескольких процессоров 1 к шине 8 ввода- вывода разрешает узел 6 выборки, предоставляя поочередно право доступа к шине 8 ввода-вывода только одному из процессоров 1 путем подачи поочередно на блоки 5 сигналов по линиям 7 разрешения.

Счетчик 26 узла 6 выборки считает тактовые импульсы с генератора 25 импульсов. К выходу счетчика 26 подключен дешифратор 27. В зависимости от кода, поступающего с выхода счетчика 26, на выходах дешифратора 27 попеременно появляются сигналы, которые по линиям 7 разрешения подаются на триггеры 19 соответствующих блоков 5. Если по переднему фронту сигнала с выхода дещифратора 27 триггер 19 не устанавливается, то с приходом следующего тактового импульса от генератора 25 импульсов изменяется состояние счетчика 26 и, соответственно, сигнал 7 раз- рещения с одного блока 5 снимается дешифратором 27 и подается на другой блок 5. Если в блоке 5 триггер 19 подготовлен к установке (есть обращение от процессора 1), то по переднему фронту сигнала 7 разрешения с дешифратора 27 узла 6 выборки триггер 19 устанавливается и открывает приемопередатчик 24, который логически и электрически соединяет процессорную шину 4 обратившегося процессора 1 с шиной 8 ввода-вывода, обеспечивая доступ процессора 1 к внешним устройствам 3. Кроме того, сигнал с выхода триггера 19 по линии 9 запрета поступает на элемента ИЛИ 28 узла 6 выборки и выключает генератор 25 импульсов, тем самым запрещая арбитраж на время обращения процессора 1 к шине 8 ввода-вывода. После завершения обращения сигнал с выхода дещифратора 10 адреса снимается и через элемент ИЛИ 16 производится сброс триггера 19 по нулевому входу в исходное состояние, что приводит к закрытию приемопередатчика 24 и включению генератора 25 тактовых импульсов. Счетчик 26 переходит в следующее состояние, продолжая тем самым арбитраж доступа к шине 8 ввода-вывода.

Внешние устройства 3 могут потребовать обслуживания по прерыванию, при этом необходимо, чтобы такое требование обслужил какой-либо один процессор 1. Для обеспечения быстрой реакции процессоров на прерывание сигнал 11 требования прерывания из щины 8 ввода-вывода от внешних устройств 3 поступает на лиНИИ 12 требования прерывания всех процессорных шин через передатчики 13. Программное обеспечение процессоров 1 построено таким образом, что во всех процессорах 1 имеются копии программ, обслуживания прерывания от внешних устройств 3- Каждый среагировавший на требование прерывания 12 процессор 1 формирует сигнал в линии 21 подтверждения прерывания, который из процессорной шины 4 поступает на входы первого 14 и второго 15 элементов И. Так как при этом сигнал в линии 11 требования прерывания шины 8 ввода-вывода через элемента ИЛИ 17 также поступает на первый элемент И 14, то первый элемент И 14 открыт и сигнал с его выхода через элемент ИЛИ 16 подготавливает триггер 19 к установке по сигналу 7 разрешения с узла выборки. Второй элемент И 15 в это время за крыт сигналом с выхода элемента НЕ 18.

В вычислительной системе могут оказаться несколько процессоров 1, среагировавших на требование прерывания от внешних устройств 3, но по сигналу 7 разрешения с узла выборки открывается только один из блоков 5, в котором устанавливается триггер 19 и открывается приемопередатчик 24, после чего соответствующий процессор 1 получает сигналы идентификации обслуживаемого прерывания от одного из внешних устройств 3, выставивших требование прерывания (в соответствии с принятой в шине 8 ввода-вывода системой приоритетов), и переходит к программе обслуживания этого устройства. Внешнее устройство 3 снимает с шины 8 ввода- вывода сигнал требования прерывания. Если в шине 8 ввода-вывода в данный момент нет требований прерывания от других внешних устройств 3, то сигнал в линии 11 требования прерывания исчезает. Сигнал с выхода триггера 19 через элемент ИЛИ 17 предотвращает преждевременный сброс триггера 19 при исчезновении сигнала в линии 11 требования прерывания. После цикла идентификации внешнего устройства 3 процессор 1 снимает сигнал 21 подтверждения прерывания, первый элемент И 14 закрывается и триггер 19 возвращается в исходное состояние.

В случае, когда только одно внешнее устройство сформировало сигнал 11 требования прерыва11ия, а в системе несколько процессоров 1 среагировали на это требование и сформировали сигнал в линии 21 подтверждения прерывания, то после того как выбранный узлом 6 процессор 1 идентифицирует внешнее устройство 3, выставившее требование 11 (путем чтения его вектора прерывания), это устройство снимает сигнал 11 требования. В это время остальные среагировавшие на прерывание процессоры, сформировав сигнал 21 подтверждения прерывания, ждут доступа к шине 8 ввода-вывода с целью идентификации прерывания. В блоках 5, соответствующих этим процессорам, отсутствие сигнала 11 требования прерывания блокирует элемент И 14 (через элемент ИЛИ 17) и, следовательно, на нулевом входе триггера 19 присутствует сигнал сброса, удерживающий этот триггер в исходном состоянии.

Инверсия сигнала 11 (выход элемента НЕ 18) при отсутствии требования прерывания, наличие сигнала 21 подтверждения прерывания и исходное состояние триггера 19 являются условиями срабатывания элемента И 15, выходной сигнал которого активизи5 рует шифратор 20. Указанный шифратор формирует сигналы 23 идентификации необслуживаемого прерывания, поступающие в процессорную шину 4. Эти сигналы образуют код специально выбранного вектора прерывания, после чтения которого по ин формационным цепям шины 4 (сигнал 21 подтверждения прерывания при этом снимается) процессор безусловно осуществляет выход из прерывания и возвращается к выполнению прерванной программы. Таким

5 образом, «с точки зрения процессора указанное прерывание вызвано псевдоустройством (вектор прерывания которого имитируется шифратором 20), причем осуществлять какую-либо обработку такого прерывания не требуется. Указанный механизм обеспечива0 ет обработку прерывания одним (выбранным узлом 6) процессором I и возврат остальных среагировавших процессоров 1 к выполнению прерванных программ. Временная диаграмма, иллюстрирующая работу элементов устройства, изменяющих свое состоя5 ние в описанной ситуации, приведена на фиг. 4.

Если в вычислительной системе имеются несколько среагировавщих на требова0 ние прерывания процессоров 1 и несколько внешних устройств 3 одновременно требуют прерывания, то одно из этих внешни.х устройств (например, самое приоритетное), идентифицируемое каким-либо одним процессором (выбранным узлом 6), снимает тре5 бование прерывания, сигнал в цепи 11 (реализованный как «Проводное ИЛИ) поддерживается другими внешними устройствами. При этом в блоках 5, соответствующих среагировавшим на прерывание процессорам, элемент И 15 блокирован сигна0 ло.м с элемента НЕ 18 и шифратор 20 не активизирован. Поэтому процессоры, выработав сигнал 21 подтверждения прерывания, «зависают до тех пор, пока узлом 6 с помощью сигнала 7 вновь не будет выбf. ран один из них, который идентифицирует следующее внешнее устройство, выставившее требование прерывания, и т. д. - пока не исчезнет сигнал в цепи 11, после чего оставшиеся процессоры получат сигналы идентификации необслуживаемого прерывания (вектор псевдоустройства, имитируемый шифратором 20 блоков 5) и вернутся к выполнению прерванных программ.

Формула изобретения

Устройство для сопряжения группы процессоров с группой внешних устройств, содержащее узел выборки и группу блоков формирования сигналов обмена, причем каждый блок формирования сигналов обмена содержит приемопередатчик, передатчик, дец ифратор адреса, отличающееся тем, что, с целью повышения быстродействия, в каждый блок формирования обмена введены шифратор, триггер, два элемента И, два элемента ИЛИ, элемент НЕ, причем первая группа информационных входов-выходов каждого блока формирования сигналов обмена образует соответствующую группу входов-выходов устройства для подключения к группе информационных входов-выходов соответствующего процесора, вторая группа информационных входов-выходов каждого блока формирования сигналов обмена образует соответствуюшую группу входов-выходов устройства для подключения к общей информационной шине внешних устройств группы, при этом группа разрешающих выходов узла выборки соединена с разре- щающими входами соответствующих блоков формирования сигналов обмена группы, выходы блокировки которых соединены с соответствующими разрядами группы входов блокировки узла выборки, причем первый информационный вход-выход приемопередатчика, информационный вход дешифратора адреса, информационные выходы передатчика и шифратора, первый вход первого элемента И, соединенный с первым входом второго элемента И, образуют первую груп0

5

0

5

0

5

пу информационных входов-выходов блока формирования сигналов обмена, второй информационный вход-выход приемопередатчика, информационный вход передатчика, соединенный с первым входом первого элемента ИЛИ и с входом элемента НЕ, образуют вторую группу информационных входов-выходов блока формирования сигналов обмена, единичный выход триггера соединен с разрешающим входом приемопередатчика, с вторым входом первого элемента ИЛИ и является выходом блокировки блока формирования сигналов обмена, синхровход триггера является разрешающий входом блока формирования сигналов обмена, при этом в блоке формирования сигналов обмена выход первого элемента ИЛИ соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с нулевым и информационным входами триггера, нулевой выход которого соединен с вторым входом второго элемента И, выход которого соединен с информационным входом щифратора, выход элемента НЕ соединен с третьим входом второго элемента И, выход дешифратора адреса соединен с вторым входом второго элемента ИЛИ, причем узел выборки содержит генератор импульсов, счетчик, дешифратор, элемент ИЛИ, при этом группа выходов дешифратора образует группу разрешающих выходов узла выборки, группа входов элемента ИЛИ образует группу входов блокировки узла выборки, при этом в узле выборки выход элемента ИЛИ соединен с разрешающим входом генератора синхроимпульсов, выход которого соединен со счетным входом счетчика, выход которого соединен с информационным входом дешифратора.

Фаг. 2

Фа.:5

| Коммуникационное оборудование: Сб | |||

| Симпозиум о развитии технических средств связи | |||

| - М., 1979, с | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Катецки Д | |||

| и др | |||

| RLURIBUS - отказоустойчивый операционный мультиплексор, ТИИЭР, 1978, т | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-14—Подача