Изобретение относится к вычислительной технике и может быть использовано в запоминающем устройстве микропроцессорных систем.

Известны динамические ОЗУ, содержащие банк памяти, формирователи сигналов управления модулем ОЗУ, мультиплексор адреса, узел формирования адресного кода регенерации и буферный регистр (см. например [1]).

Недостатками известных устройств являются низкое быстродействие, большое количество сигналов управления, а также необходимость применения счетчиков адреса регенерации, что усложняет устройство.

Наиболее близким техническим решением к изобретению является устройство для регенерации информации динамической памяти [2]

Устройство содержит первый триггер, блок анализа приоритетов, вход обращения которого соединен с выходом первого триггера, первый формирователь синхроимпульса, вход обращения и вход регенерации которого соединены с первым и вторым выходами блока анализа приоритетов, первый, второй и третий выходы первого формирователя синхросигналов являются соответственно выходами выборки строки, разрешения записи и выборки столбца устройства, четвертый выход первого формирователя синхросигнала соединен с входом сброса первого триггера, счетчик адреса регенерации, мультиплексор, первый и второй адресные входы которого соединены соответственно с выходом счетчика адреса регенерации, первым выходом блока анализа приоритетов и с выходом счетчика адреса регенерации, адресный вход и выход мультиплексора являются адресным входом и адресным выходом устройства, счетчик регенерации, вход которого является тактовым входом устройства, элемент И, второй формирователь синхросигналов, вход обращения которого является входом обращения устройства, первый выход первого формирователя синхросигналов является тактовым выходом устройства, вход установки и вход сброса которого соединены соответственно с третьим выходом и входом обращения второго формирователя синхросигналов, выход второго триггера соединен с первым входом элемента И, третий триггер, входы установки и сброса которого соединены соответственно с выходом счетчика регенерации и пятым выходом второго формирователя синхросигналов, выход третьего триггера соединен с вторым входом элемента И, вход счетчика адреса регенерации соединен с пятым выходом второго формирователя синхросигналов, вход обращения блока анализа приоритета соединен с выходом элемента И.

Известное устройство позволяет повысить быстродействие контроллера, но оно не учитывает специфики новых модификаций микросхем ОЗУ, таких как К565РУ7, в которых счетчик адреса регенерации входит в состав микросхемы и регенерация памяти может быть осуществлена в режиме  - перед

- перед  . Такой вариант построения контроллера позволяет значительно упростить устройство и повысить надежность за счет исключения значительного количества навесных элементов.

. Такой вариант построения контроллера позволяет значительно упростить устройство и повысить надежность за счет исключения значительного количества навесных элементов.

Сущность предлагаемого изобретения заключается в том, что в состав устройства для регенерации информации динамической памяти, содержащее первый формирователь импульсов, первый мультиплексор, входы которого являются входными адресными шинами устройства для связи с ЭВМ, а выходы являются выходами устройства для связи с динамической памятью, элемент ИЛИ, первый вход которого является первым управляющим входом устройства для связи с ЭВМ и выходом устройства для связи с динамической памятью, второй вход вторым управляющим входом для связи с ЭВМ и выходом устройства для связи с динамической памятью, а выход подсоединен к первым входам первого мультиплексора и первого триггера, второй вход которого соединен с третьим выходом второго формирователя импульсов, четвертый выход которого подключен к первому входу второго триггера, а первый вход ко входу счетчика и является тактовым входом устройства, введены элемент задержки, второй мультиплексор и инвертор, вход которого соединен с выходом счетчика, входом первого формирователя, выходом соединенного с первым входом второго мультиплексора, и третьим входом первого триггера, выход которого подключен ко второму входу второго формирователя, второму входу второго мультиплексора и является третьим управляющим выходом устройства для связи с динамической памятью, третий вход второго мультиплексора подсоединен ко второму выходу второго формирователя, а выход является выходом выборки столбца устройства, выход инвертора через элемент задержки является выходом выборки строки устройства, второй вход второго триггера подключен к выходу элемента ИЛИ, третий вход к выходу сигнала логической единицы, первый выход является выходом устройства для связи с ЭВМ, а второй выход подключен к третьему входу второго формирователя, первый выход которого соединен со вторым управляющим входом первого мультиплексора.

Предлагаемое техническое решение позволяет значительно упростить динамическое ОЗУ и устройство для регенерации информации динамической памяти при использовании в его составе перспективных микросхем памяти, например К565РУ7, за счет исключения внешних счетчиков адреса регенерации строки, обеспечить снижение корпусов мультиплексора адреса, так как исчезает необходимость большого количества у него входов, и исключить ряд других элементов. Все это позволяет также повысить надежность устройства.

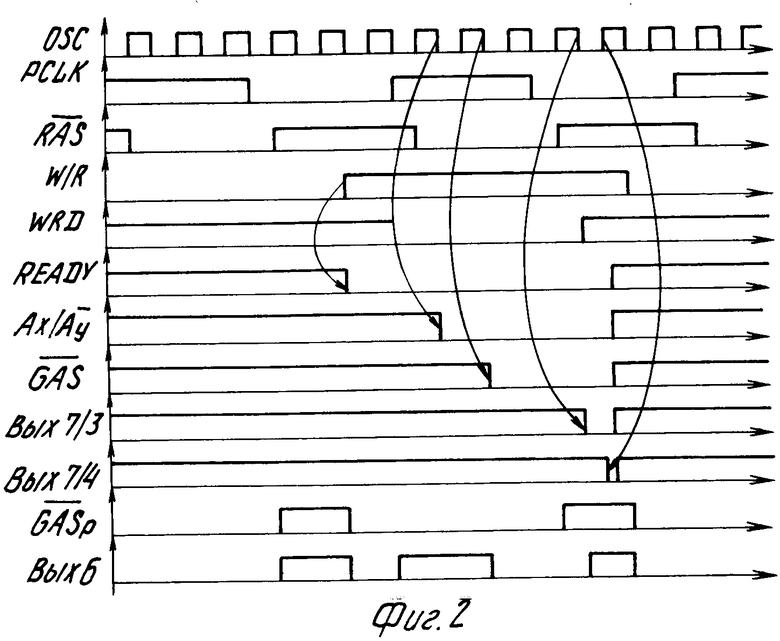

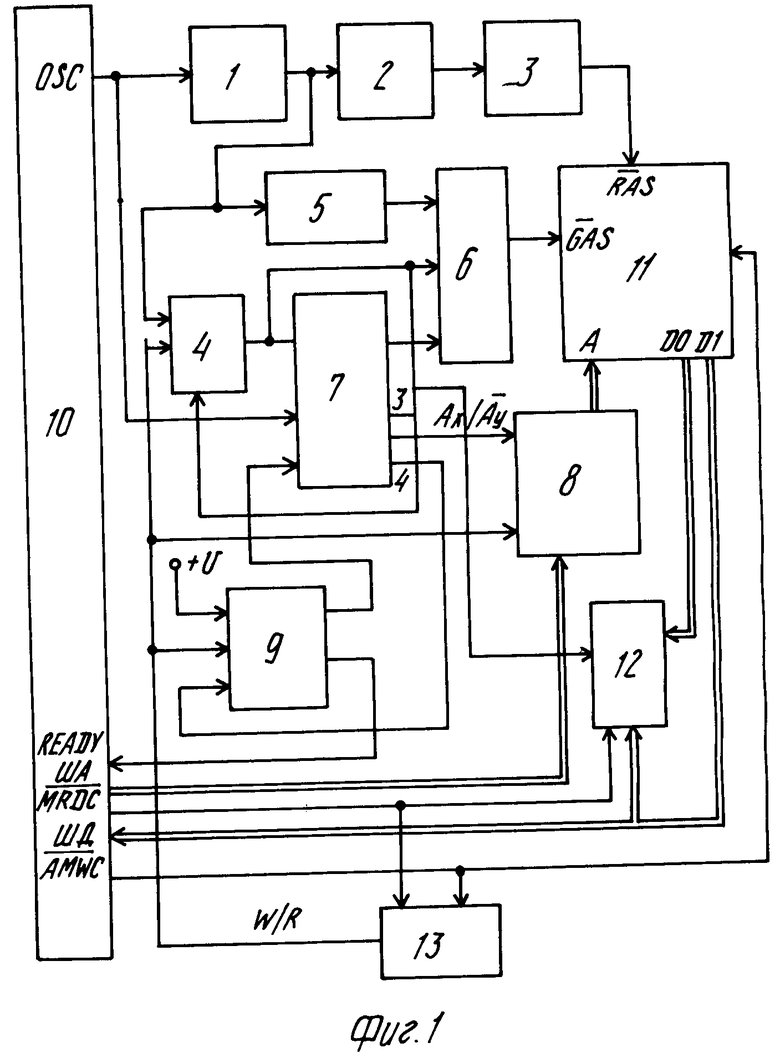

На фиг. 1 приведена электрическая схема устройства, а также миниЭВМ и элементы динамического ОЗУ. На фиг. 2 приведены временные диаграммы работы устройства.

Устройство содержит счетчик 1, вход которого подключен к тактовому входу ОSC, а выход РСLK через инвертор 2 и элемент задержки 3 подключен ко входу выборки строки  банка ОЗУ. Кроме того, сигнал PCLK поступает на счетный вход первого триггера 4 и вход второго формирователя импульсов 5, выход которого подключен к первому входу второго мультиплексора 6, выход которого подключен ко входу выборки столбца

банка ОЗУ. Кроме того, сигнал PCLK поступает на счетный вход первого триггера 4 и вход второго формирователя импульсов 5, выход которого подключен к первому входу второго мультиплексора 6, выход которого подключен ко входу выборки столбца  банка ОЗУ. Сигнальный вход триггера 4 соединен со входом обращения W/R устройства, а выход WRD с управляющим входом мультиплексора 6 и сигнальным входом второго формирователя 7, первый выход которого подключен ко входу коммутации адреса строки и адреса столбца Ax/Ay первого мультиплексора 8, второй к третьему входу второго мультиплексора 6, третий к установочному входу второго триггера 9, выход которого является выходом сигнала готовности READY устройства. Опорные сигналы на устройство снимаются с микроЭВМ 10. Кроме того, на рисунке изображены банк динамического ОЗУ 11, буферный регистр 12 и элемент ИЛИ 13.

банка ОЗУ. Сигнальный вход триггера 4 соединен со входом обращения W/R устройства, а выход WRD с управляющим входом мультиплексора 6 и сигнальным входом второго формирователя 7, первый выход которого подключен ко входу коммутации адреса строки и адреса столбца Ax/Ay первого мультиплексора 8, второй к третьему входу второго мультиплексора 6, третий к установочному входу второго триггера 9, выход которого является выходом сигнала готовности READY устройства. Опорные сигналы на устройство снимаются с микроЭВМ 10. Кроме того, на рисунке изображены банк динамического ОЗУ 11, буферный регистр 12 и элемент ИЛИ 13.

В исходном состоянии, т. е. при отсутствии сигналов чтения/запись по переднему фронту тактовых импульсов ОSC (фиг. 2), счетчик 1 формирует на своем выходе сигнал РСLK (фиг. 2), равный по длительности допустимому по ТУ на микросхему ОЗУ сигналу  (фиг. 2). Сигнал РСLK служит для синхронизации работы всех элементов устройства и для формирования импульсов выборки строки

(фиг. 2). Сигнал РСLK служит для синхронизации работы всех элементов устройства и для формирования импульсов выборки строки  . Сигнал

. Сигнал  формируется путем инвертирования импульсов PCLK, задержки их по фазе элементов задержки 3 и непрерывно поступает на вход

формируется путем инвертирования импульсов PCLK, задержки их по фазе элементов задержки 3 и непрерывно поступает на вход  банка ОЗУ 11. На вход

банка ОЗУ 11. На вход  банка ОЗУ в исходном состоянии с выхода мультиплексора 6 поступают импульсы

банка ОЗУ в исходном состоянии с выхода мультиплексора 6 поступают импульсы  p (фиг. 2), генерируемые формирователем 5, длительность которых меньше сигнала

p (фиг. 2), генерируемые формирователем 5, длительность которых меньше сигнала  в соответствии с идеологией регенерации ОЗУ в режиме "

в соответствии с идеологией регенерации ОЗУ в режиме " -передRAS". По отрицательному фронту сигнала при нулевом уровне

-передRAS". По отрицательному фронту сигнала при нулевом уровне  происходит переключение внутреннего счетчика адреса регенерации микросхем динамического ОЗУ (например, микросхемы К565РУ7) на следующую строку и ее регенерация. Триггер 4 и формирователь импульсов 7 формируют на своих выходах уровни логической единицы, на первом выходе триггера 9 нулевой уровень, на втором выходе уровень логической единицы. Мультиплексор 8 находится в третьем состоянии, у мультиплексора 6 к выходу подключен первый вход.

происходит переключение внутреннего счетчика адреса регенерации микросхем динамического ОЗУ (например, микросхемы К565РУ7) на следующую строку и ее регенерация. Триггер 4 и формирователь импульсов 7 формируют на своих выходах уровни логической единицы, на первом выходе триггера 9 нулевой уровень, на втором выходе уровень логической единицы. Мультиплексор 8 находится в третьем состоянии, у мультиплексора 6 к выходу подключен первый вход.

В режиме обмена с микроЭВМ 10 на вход динамического ОЗУ поступает сигнал либо чтения, либо записи, который в виде сигнала W/R (фиг. 2) через элемент ИЛИ 13 выключает в мультиплексоре 8 режим третьего состояния и подключает к адресному входу банка ОЗУ 11 код адреса строк. Последовательность формируемых управляющих импульсов следующая.

По сигналу W/R на адресный вход банка ОЗУ 11 поступает код адреса строки. Через время, задаваемое элементом задержки 3, на вход  банка ОЗУ с выхода элемента задержки поступает задний фронт импульса ввода строки

банка ОЗУ с выхода элемента задержки поступает задний фронт импульса ввода строки  . По этому импульсу адрес строки фиксируется в адресном регистре строки микросхем банка ОЗУ.

. По этому импульсу адрес строки фиксируется в адресном регистре строки микросхем банка ОЗУ.

Кроме того, по переднему фронту сигнала W/R триггер 9 перебрасывается в другое устойчивое состояние, при котором на его первом выходе формируется сигнал логического нуля, на втором выходе сигнал логической единицы, который деблокирует формирователь 7 по третьему входу. Сигнал READY (фиг. 2) с первого выхода триггера 9 является сигналом готовности ОЗУ к следующему циклу обращения и при необходимости инициализирует формирование миниЭВМ пустых тактов для согласования временных диаграмм микроЭВМ и устройства.

По переднему фронту сигнала РСLK (фиг. 2) происходит переброс триггера 4 в состояние логического нуля. Формируемый при этом сигнал WRD (фиг. 2) поступает на второй вход мультиплексора 6 и второй вход формирователя 7, чем обеспечивается подключение его первого выхода через мультиплексор 6 на вход  банка ОЗУ. При этом импульсы

банка ОЗУ. При этом импульсы  p, снимаемые с выхода формирователя импульсов 5, отключаются от входа

p, снимаемые с выхода формирователя импульсов 5, отключаются от входа  банка ОЗУ. Состояние буферного регистра 12 по отрицательному фронту сигнала WRD не изменяется.

банка ОЗУ. Состояние буферного регистра 12 по отрицательному фронту сигнала WRD не изменяется.

Задний фронт ближайшего импульса сигнала OSC (фиг. 2) вызывает переключение первого выхода формирователя импульсов 7 в состояние нулевого уровня, что обеспечивает подачу через мультиплексор 8 на адресные входы банка ОЗУ 11 адреса столбцов.

Задний фронт очередного импульса OSС перебрасывает второй выход формирователя импульсов 7 в состояние нулевого уровня, которое через открытый по третьему входу мультиплексор 6 поступает на вход  банка ОЗУ и по своему отрицательному фронту фиксирует в адресном регистре столбцов микросхем памяти банка ОЗУ адрес столбца, а также осуществляет либо запись информации в банк ОЗУ в режиме записи, либо в режиме чтения выводит записанную в микросхемах памяти информацию на вход буферного регистра 12.

банка ОЗУ и по своему отрицательному фронту фиксирует в адресном регистре столбцов микросхем памяти банка ОЗУ адрес столбца, а также осуществляет либо запись информации в банк ОЗУ в режиме записи, либо в режиме чтения выводит записанную в микросхемах памяти информацию на вход буферного регистра 12.

Следующий импульс сигнала OSC своим задним фронтом переключает третий выход формирователя 7 в состояние нулевого уровня, которое возвращает триггер 4 в исходное состояние. По положительному фронту сигнала WRD выход мультиплексора 6 переключается с третьего входа на первый, и на вход  банка ОЗУ начинают поступать импульсы с выхода формирователя 5. Кроме того, положительный фронт сигнала в режиме чтения фиксирует выходные данные банка ОЗУ 11 в буферном регистре 12.

банка ОЗУ начинают поступать импульсы с выхода формирователя 5. Кроме того, положительный фронт сигнала в режиме чтения фиксирует выходные данные банка ОЗУ 11 в буферном регистре 12.

Очередной импульс сигнала ОSC своим передним фронтом переключает четвертый выход формирователя импульсов 7 в состояние нулевого уровня, которое возвращает триггер 9 в исходное состояние, при котором на его первом выходе появляется сигнал готовности динамического банка ОЗУ к очередному циклу обращения, а логический нуль на втором выходе переводит формирователь 7 в исходное состояние, т.е. на всех его выходах появляется уровень логической единицы.

На этом заканчивается режим обращения и устройство переходит в режим регенерации. Регенерация будет производиться до очередного обращения к ОЗУ и прихода импульсов MRWD/AMWC, по которым ОЗУ без задержки переходит в режим обмена. Следовательно, в предложенном устройстве реализован способ "прозрачной" регенерации. Устройство работоспособно и при повышении тактовой частоты микропроцессора микроЭВМ 10, т.е. во всех условиях после цикла обмена обеспечивается как минимум один цикл регенерации. При этом суммарное время регенерации при длительности цикла обмена (в соответствии с ТУ на микросхемы памяти), равном 0,4 мкс, составляет 410 мкс, что значительно меньше допустимого по ТУ 8000 мкс. При частоте импульсов OSC, равной 15 МГц, и частоте импульсов РСLК, равной 2,5 МГц, в данном устройстве полностью реализуется временная диаграмма чтения, записи, регенерации в режиме  перед

перед  , требуемая по ТУ на микросхемы памяти.

, требуемая по ТУ на микросхемы памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1377909A1 |

| Устройство для регенерации информации динамической памяти | 1988 |

|

SU1635213A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для счета количества изображений объекта | 1987 |

|

SU1494021A1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах микропроцессорных систем. Устройство содержит счетчик 1, инвертор 2, элемент задержки 3, два триггера 4, 9, два мультиплексора 6, 8, два формирователя 5, 6, элемент ИЛИ 13. 2 ил.

УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ, содержащее первый формирователь импульсов, первый мультиплексор, входы которого являются адресными входами устройства для связи с ЭВМ, а выходы являются выходами устройства для связи с динамической памятью, элемент ИЛИ, первый вход которого является первым управляющим входом устройства для связи с ЭВМ и выходом устройства для связи с динамической памятью, второй вход вторым управляющим входом для связи с ЭВМ и выходом устройства для связки с динамической памятью, а выход подключен к первому управляющему входу первого мультиплексора и первому входу первого триггера, второй вход которого соединен с третьим выходом второго формирователя импульсов, четвертый вход которого подключен к первому входу второго триггера, а первый вход к входу счетчика и является тактовым входом устройства, отличающееся тем, что в него введены элемент задержки, второй мультиплексор и инвертор, вход которого соединен с выходом счетчика, третьим входом первого триггера и входом первого формирователя, выход которого соединен с первым входом второго мультиплексора, выход первого триггера подключен к второму входу второго формирователя, второму входу второго мультиплексора и является третьим управляющим выходом устройства для связи с динамической памятью, третий вход второго мультиплексора соединен с вторым выходом второго формирователя, а выход является выходом выборки столбца устройства, выход инвертора через элемент выдержки является выходом выборки строки устройства, второй вход второго триггера подключен к выходу элемента ИЛИ, третий вход является входом логической единицы устройства, первый выход является управляющим выходом устройства для связи с ЭВМ, а второй выход подключен к третьему входу второго формирователя, первый выход которого соединен с вторым управляющим входом первого мультиплексора.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для регенерации информации динамической памяти | 1988 |

|

SU1635213A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-11-27—Публикация

1992-05-27—Подача