Изобретение относится к вычислительной технике и может быть использовано в локальных вычислительных сетях.

Цель изобретения - повышение достоверности контроля информации.

На фиг. 1 показана блок-схема устройства для контроля информации; на

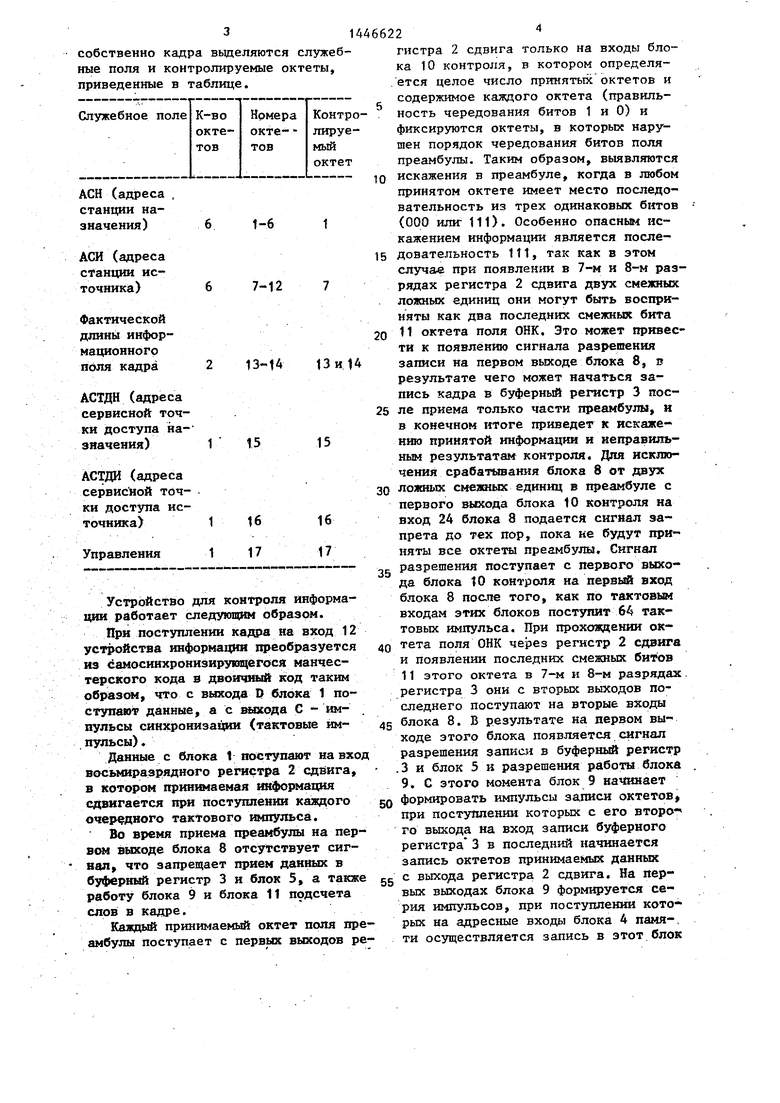

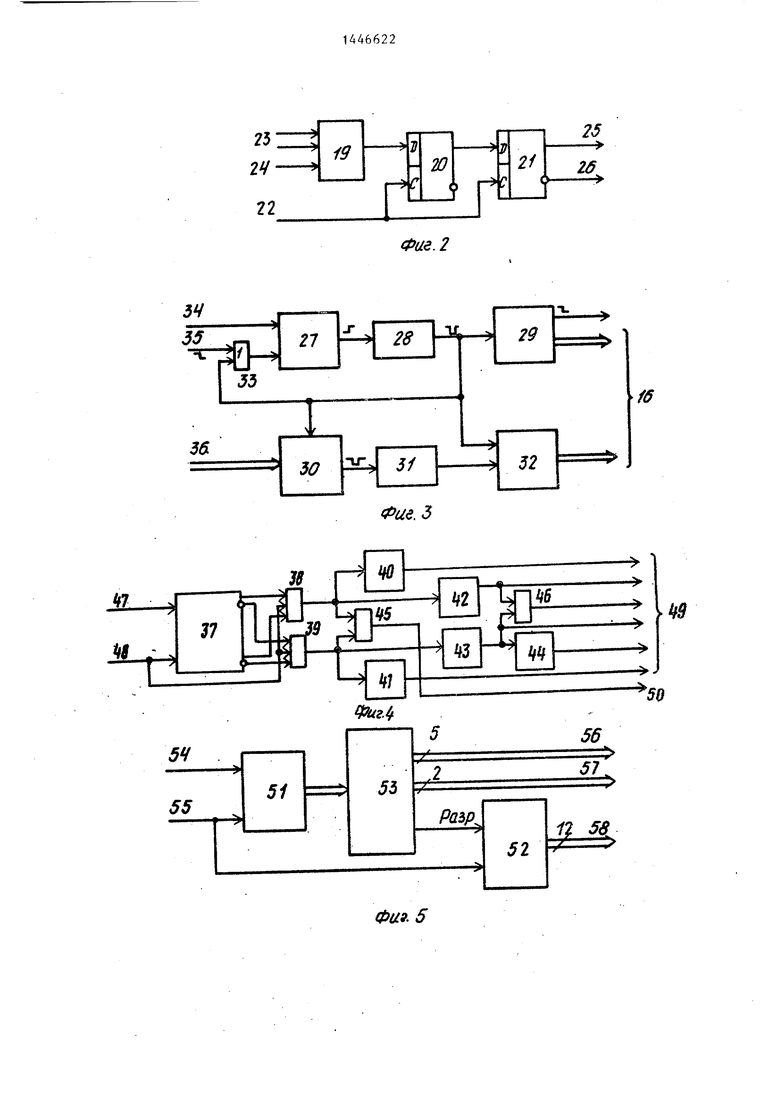

Блок 11 подсчета слов в кадре может быть выполнен на первом и втором счетчиках 51 и 52 и дешифраторе 53. На фиг. 5 обозначены разрешающий и счетный входы 54 и 55 и первые третьи выходы 56-58.

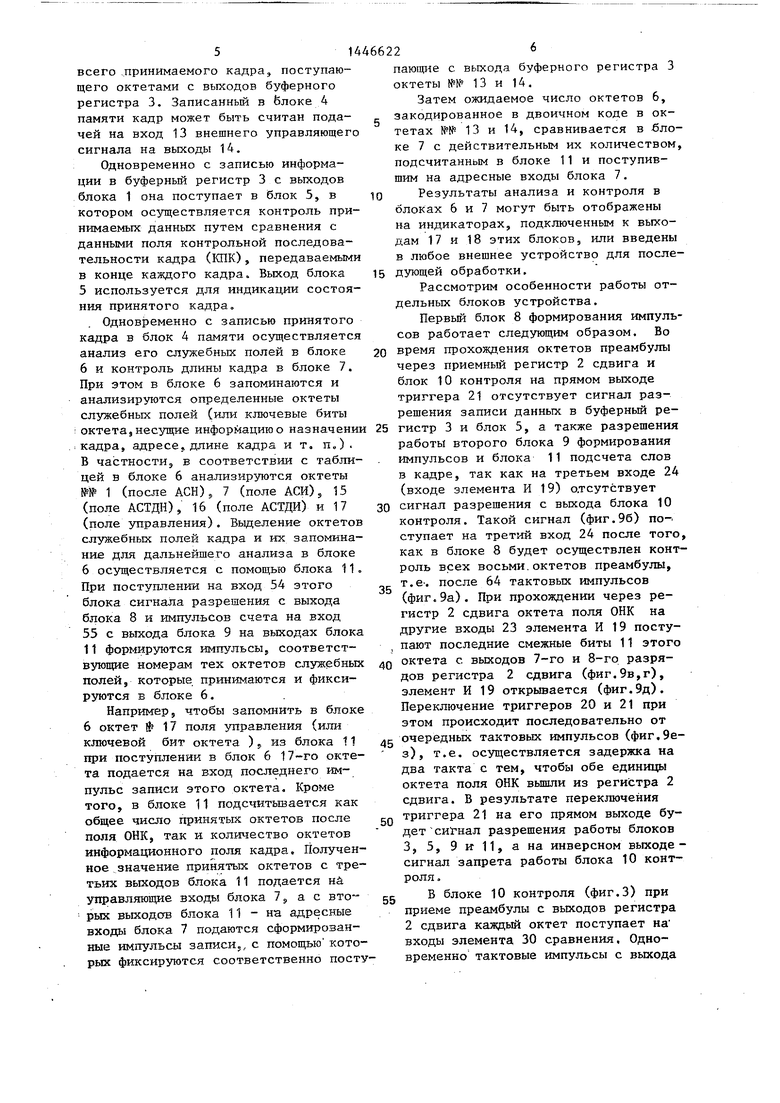

Второй блок 6 сравнения может быть вьшолнен (фиг.6) на регистрах 59, эле20

25

30

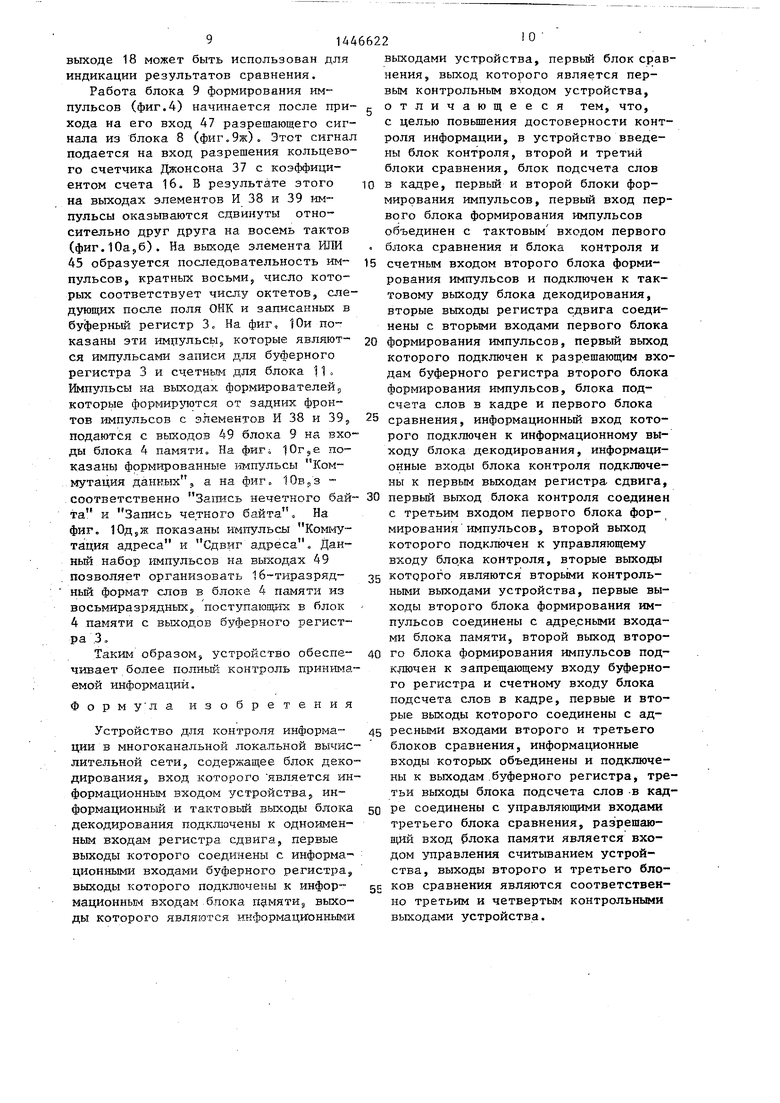

фиг. 2 - первый блок формирования им- ю мантах 60 сравнения и источнике 61 ко- пульсов; на фиг. 3 - блок контроля; На фиг. 4 - второй блок формирования импульсов; на фиг. 5 - блок подсчета слов в кадре; на фиг, 6 и 7 - второй и третий блоки сравнения соответст- 15 венно; на фиг, 8 - диаграмма, поясняющая преобразование самосинхронизирующего манчестерского кода в двоичный код (без возврата к нулю); на фиг. 9 и 10 - времен ш диаграммы сигналов в первом и втором формирователях импульсов.

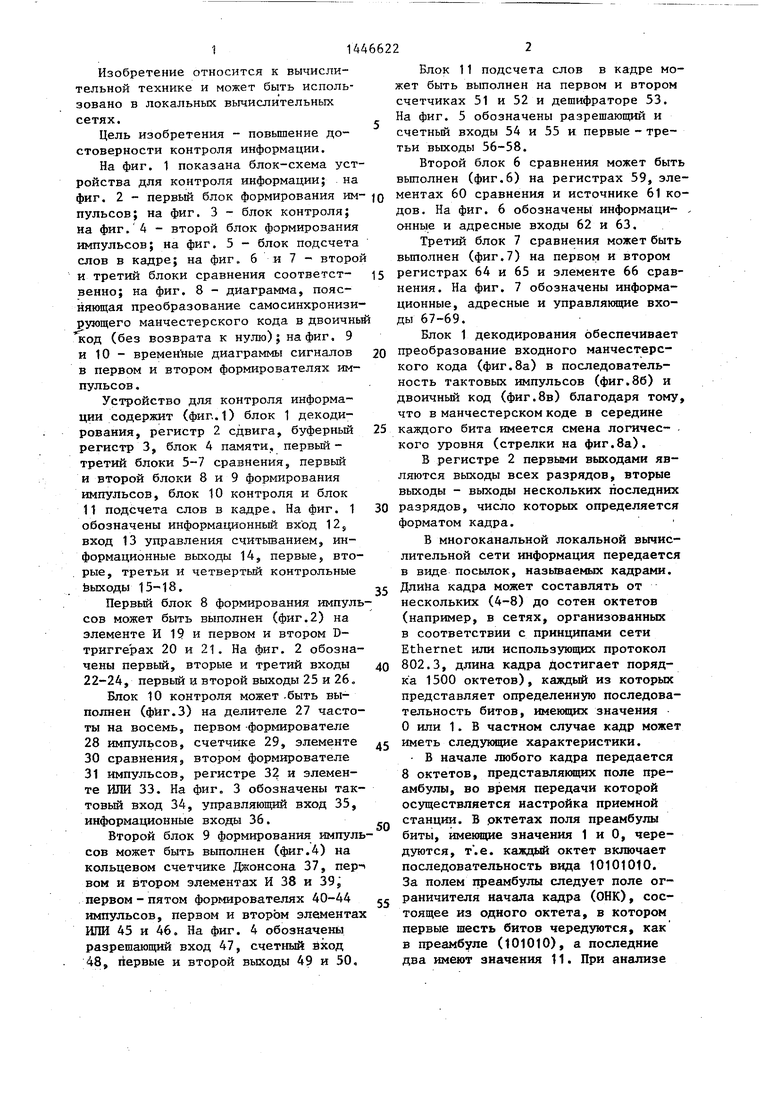

Устройство для контроля информации содержит (фиг,.1) блок 1 декодирования, регистр 2 сдвига, буферный регистр 3, блок 4 памяти, первый- третий блоки 5-7 сравнения, первый и второй блоки 8 и 9 формирования импульсов, блок 10 контроля и блок 11 подсчета слов в кадре. На фиг. 1 обозначены информационный вход IZj вход 13 управления считьшанием, информационные выходы 14, первые, вто- . рые, третьи и четвертый контрольные Ьыходы 15-18,

Первый блок В формирования импульсов может быть выполнен (фиг.2) на элементе И 19 и первом и втором D- триггерах 20 и 21. На фиг. 2 обозначены первый, вторые и третий входы 22-24, первьй и второй выходы 25 и 26 Блок 10 контроля может .быть выполнен (фйг.З) на делителе 27 частоты на восемь, первом -формирователе 28 импульсов, счетчике 29, элементе

30сравнения, втором формирователе

31импульсов, регистре 3 и элементе ИЛИ 33. На фиг, 3 обозначены тактовый вход 34, управляющий вход 35, информационные входы 36.

Второй блок 9 формирования импульсов может быть выполнен (фиг.4) на кольцевом счетчике Джонсона 37, nepi BOM и втором элементах И 38 и 39j первом - пятом формирователях 40-44 импульсов, первом и втором алиментах ИЛИ 45 и 46. На фиг, 4 обозначены разрешающий вход 47, счетный вход 48, йервые и второй выходы 49 и 50,

дов. На фиг. 6 обозначены информационные и адресные входы 62 и 63.

Третий блок 7 сравнения может быть выполнен (фиг.7) на первом и втором регистрах 64 и 65 и элементе 66 сравнения. На фиг. 7 обозначены информационные, адресные и управляющие входы 67-69.

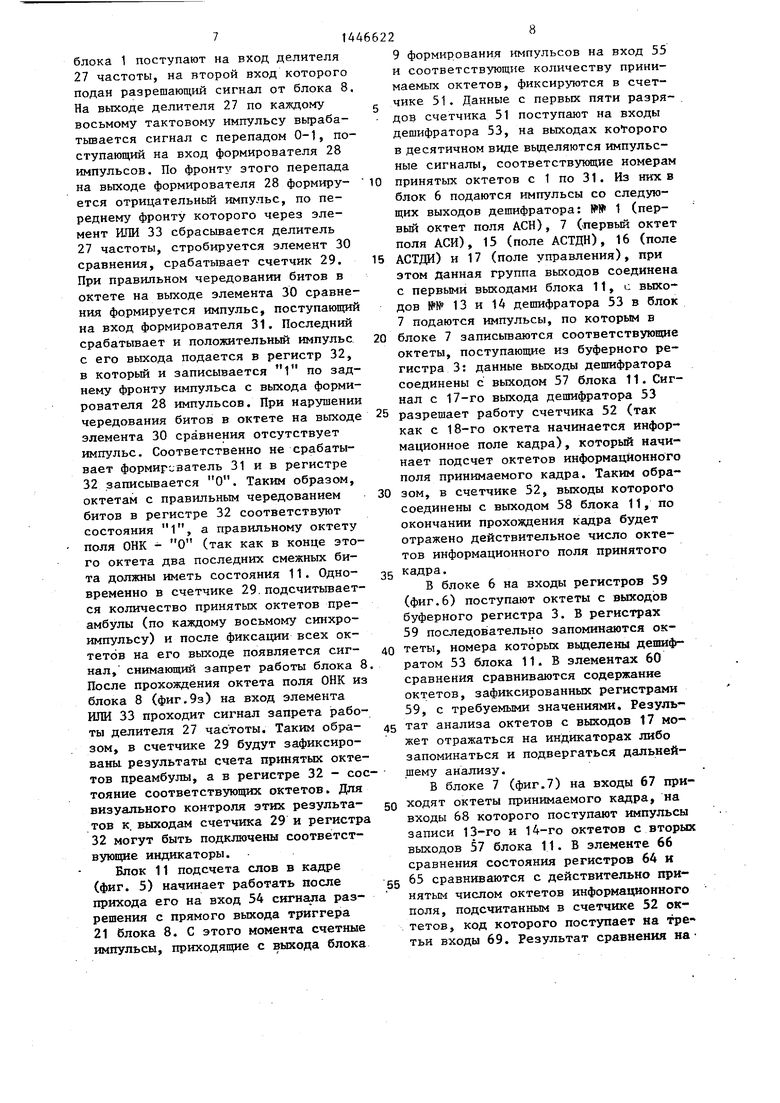

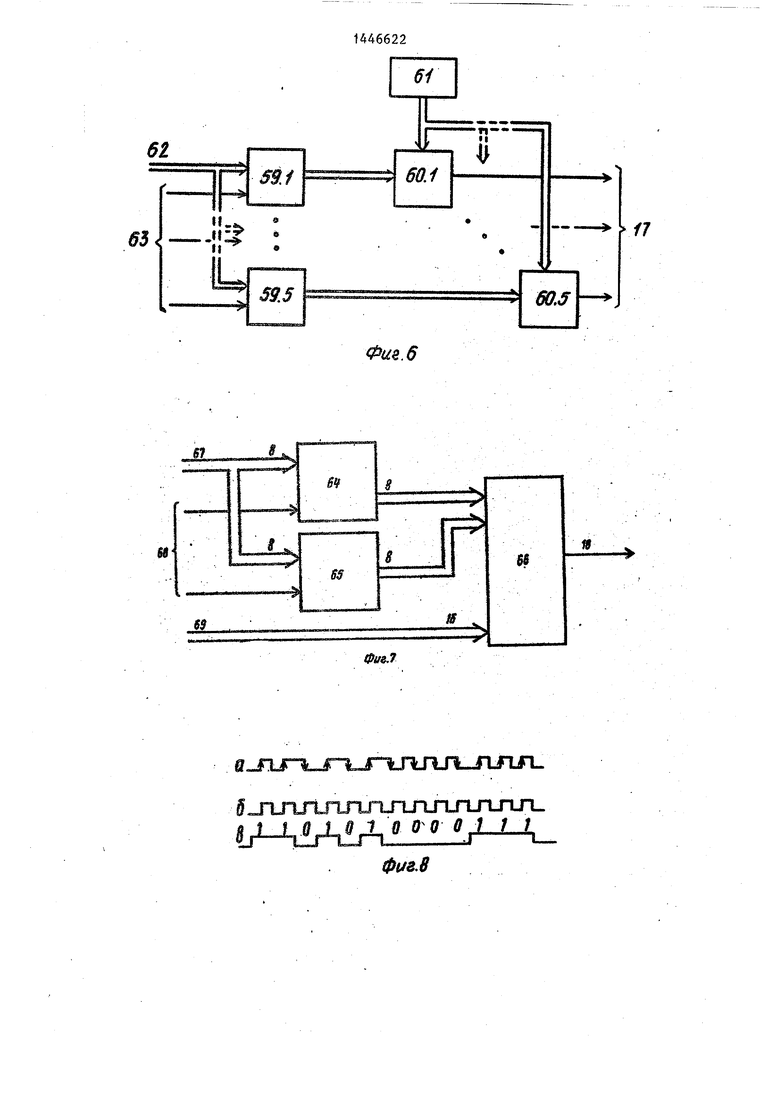

Блок 1 декодирования обеспечивает преобразование входного манчестерского кода (фиг.8а) в последовательность тактовых импульсов (фиг.86) и двоичный код (фиг.8в) благодаря тому, что в манчестерском коде в середине каждого бита имеется смена логичес- - кого уровня (стрелки на фиг,8а),

В регистре 2 первыми выходами являются выходы всех разрядов, вторые выходы - выходы нескольких последних разрядов, число которых определяется форматом кадра.

В многоканальной локальной вычислительной сети информация передается в виде посылок, наэьюаемых кадрами. Длина кадра может составлять от нескольких (4-8) до сотен октетов (например, в сетях, организованных в соответствии с принципами сети Ethernet или использующих протокол 802.3, длина кадра достигает порядка 1500 октетов), каждый из которых представляет определенную последовательность битов, имекшщх значения О или 1. В частном случае кадр может иметь следующие характеристики.

Б начале любого кадра передается 8 октетов, представлякнцих поле преамбулы, во время передачи которой осуществляется настройка приемной станции, В рктетах поля преамбулы биты, имеющие значения 1 и О, чередуются, т ,е. каящый октет включает последовательность вида 10101010, За полем преамбулы следует поле ог- 5J раничителя начала кадра (ОНК), состоящее из одного октета, в котором первые шесть битов чередуются, как в преамбуле (101010), а последние два имеют значения 11, При анализе

35

40

45

50

222

Блок 11 подсчета слов в кадре может быть выполнен на первом и втором счетчиках 51 и 52 и дешифраторе 53. На фиг. 5 обозначены разрешающий и счетный входы 54 и 55 и первые третьи выходы 56-58.

Второй блок 6 сравнения может быть вьшолнен (фиг.6) на регистрах 59, эле0

5

0

мантах 60 сравнения и источнике 61 ко- 5

дов. На фиг. 6 обозначены информационные и адресные входы 62 и 63.

Третий блок 7 сравнения может быть выполнен (фиг.7) на первом и втором регистрах 64 и 65 и элементе 66 сравнения. На фиг. 7 обозначены информационные, адресные и управляющие входы 67-69.

Блок 1 декодирования обеспечивает преобразование входного манчестерского кода (фиг.8а) в последовательность тактовых импульсов (фиг.86) и двоичный код (фиг.8в) благодаря тому, что в манчестерском коде в середине каждого бита имеется смена логичес- - кого уровня (стрелки на фиг,8а),

В регистре 2 первыми выходами являются выходы всех разрядов, вторые выходы - выходы нескольких последних разрядов, число которых определяется форматом кадра.

В многоканальной локальной вычислительной сети информация передается в виде посылок, наэьюаемых кадрами. Длина кадра может составлять от нескольких (4-8) до сотен октетов (например, в сетях, организованных в соответствии с принципами сети Ethernet или использующих протокол 802.3, длина кадра достигает порядка 1500 октетов), каждый из которых представляет определенную последовательность битов, имекшщх значения О или 1. В частном случае кадр может иметь следующие характеристики.

Б начале любого кадра передается 8 октетов, представлякнцих поле преамбулы, во время передачи которой осуществляется настройка приемной станции, В рктетах поля преамбулы биты, имеющие значения 1 и О, чередуются, т ,е. каящый октет включает последовательность вида 10101010, За полем преамбулы следует поле ог- J раничителя начала кадра (ОНК), состоящее из одного октета, в котором первые шесть битов чередуются, как в преамбуле (101010), а последние два имеют значения 11, При анализе

5

0

5

0

собственно кадра вьзделяются служебные поля и контролируемые октеты, приведенные в таблице.

1-6

7-12

13-14 13 и 14

15

16 17

15

16 17

Устройство для контроля информации работает следующЮ4 образом.

При поступлении кадра на вход 12 устройства информации преобразуется из ёамосинхронизнрующегося манчестерского кода а двоичный код таким образом, что с выхода Р блока 1 поступают данные, а с шосода С - импульсы синхронизации (тактовые импульсы).

Данные с блока 1 поступают на вход восьмиразрядного регистра 2 сдвига, в котором принимаемая информация сдвигается при поступлении каждого очередного тактового импульса.

Во время приема преамбулы на первом выходе блока 8 отсутствует сиг- вал, что запрещает прием данных в буферный регистр 3 и блок 5, а также работу блока 9 и блока 11 подсчета слов в кадре.

Каждый принимаемый октет поля хфе- амбулы поступает с первых выходов ре

5

гистра 2 сдвига только на входы блока 10 контроля, в котором определяется целое число принятых октетов и содержимое каждого октета (правильность чередования битов 1 и 0) и фиксируются октеты, в которых нарушен порядок чередования битов поля преамбулы. Таким образом, выявляются искажения в преамбуле, когда в любом принятом октете имеет место последовательность из трех одинаковых битов (000 или- 111). Особенно опасным искажением информации является последовательность 111, так как в этом случае при появлении в 7-м и 8-м разрядах регистра 2 сдвига двух смежных ложных единиц они могут быть восприняты как два последних смежньос бита 11 октета поля ОНК. Это может привести к появлению сигнала разрешения записи на первом выходе блока 8, в результате чего может начаться запись кадра в буферный регистр 3 пос5 ле приема только части преамбулы, и в конечном итоге приведет к искажению принятой информации и кеправиль- ньм результатам контроля. Дня исключения срабатывания блока 8 от двух

0 ложных смешшх единиц в преамбуле с первого выхода блока 10 контроля на вход 24 блока 8 подается сигнал запрета до тех пор, пока не будут при- няты все октеты преамбулы. Сигнал разрешения поступает с первого выхода блока to контроля на первый вход блока 8 пос-пе того, как по тактовкм входам этих блоков поступит 64 тактовых импульса. При прохождении октета поля ОНК через регистр 2 сдвига и появлении последних смежных битов 11 этого октета в 7-м и 8-м разрядах. регистра 3 они с вторых выходов последнего поступают на вторые входы блока 8. В результате на первом выходе этого блока появляется сигнал разрешения записи в буферный регистр .3 и блок 5 и разрешения работы блока . 9. С этого момента блок 9 начинает

0 формировать импульсы записи октетов, при поступлении которых с его второ го выхода на вход записи буферного регистра 3 в последнш1 начинается запись октетов принимаемых данных с регистра 2 сдвига. На первых выходах блока 9 формируется серия импульсов, при поступлении которых на адресные входы блока 4 памя-. ти осуществляется запись в зтот блок

5

0

5

5

всего принимаемого кадра, поступающего октетами с выходов буферного регистра 3. Записанньш в Ьлоке 4 памяти кадр может быть считан подачей на вход 13 внешнего управляющего сигнала на выходы 14.

Одновременно с записью информации в буферный регистр 3 с выходов блока 1 она поступает в блок 5, в Котором осуществляется контроль принимаемых данных путем сравнения с данными поля контрольной последовательности кадра (КПК), передаваемыми в конце каждого кадра. Выход блока

5используется для индикации состояния принятого кадра.

Одновременно с записью принятого кадра в блок 4 памяти осуществляется анализ его служебных полей в блоке

6и контроль длины кадра в блоке 7. При этом в блоке 6 запоминаются и анализируются определенные октеты служебных полей (или ключевые биты

I октета J несущие информацию о назначени кадра, адресе, длине кадра и т. п.). В частности, в соответствии с таблицей в блоке 6 анализируются октеты т 1 (после АСН) 7 (поле АСИ) 15 (поле АСТДН), 16 (поле АСТДИ) и 17 (поле зтЕравления). Выделение октетов служебньк полей кадра и их запоминание для дальнейшего анализа в блоке 6 осуществляется с помощью блока 11. При поступлении на вход 54 этого блока сигнала разрешения с выхода блока 8 и импульсов счета на вход 55 с выхода блока 9 на выходах блока 11 формируются импульсы, соответствующие номерам тех октетов служебных полей, которые принимаются и фикси- РЗШ)тся в блоке 6,

Например, чтобы запомнить в блоке 6 октет 1 17 поля управления (или ключевой бит октета ). из блока t1 при поступлении в блок 6 17-го октета подается на вход последнего импульс записи этого октета. Кроме того, в блоке 11 подсчитывается как общее число принятых октетов после поля ОНК, так и количество октетов информационного поля кадра. Полгучен- ное.значение принятых октетов с третьих выходов блока 11 подается нд. управляющие входы блока 7., а с вторых выходов блока 11 - на адресные входы блока 7 подаются сформированные импульсы записи, с помощью которых фиксируются соответственно поступающие с выхода буферного регистра 3 октеты №№ 13 и 14.

Затем ожидаемое число октетов 6, закодированное в двоичном коде в октетах №№ 13 и 14, сравнивается в 5ло- ке 7 с действительным их количеством, подсчитанным в блоке 11 и поступившим на адресные входы блока 7. Результаты анализа и контроля в блоках 6 и 7 могут быть отображены на индикаторах, подключенным к выходам 17 и 18 этих блоков, или введены в любое внешнее устройство для после5 дующей обработки.

Рассмотрим особенности работы отдельных блоков устройства.

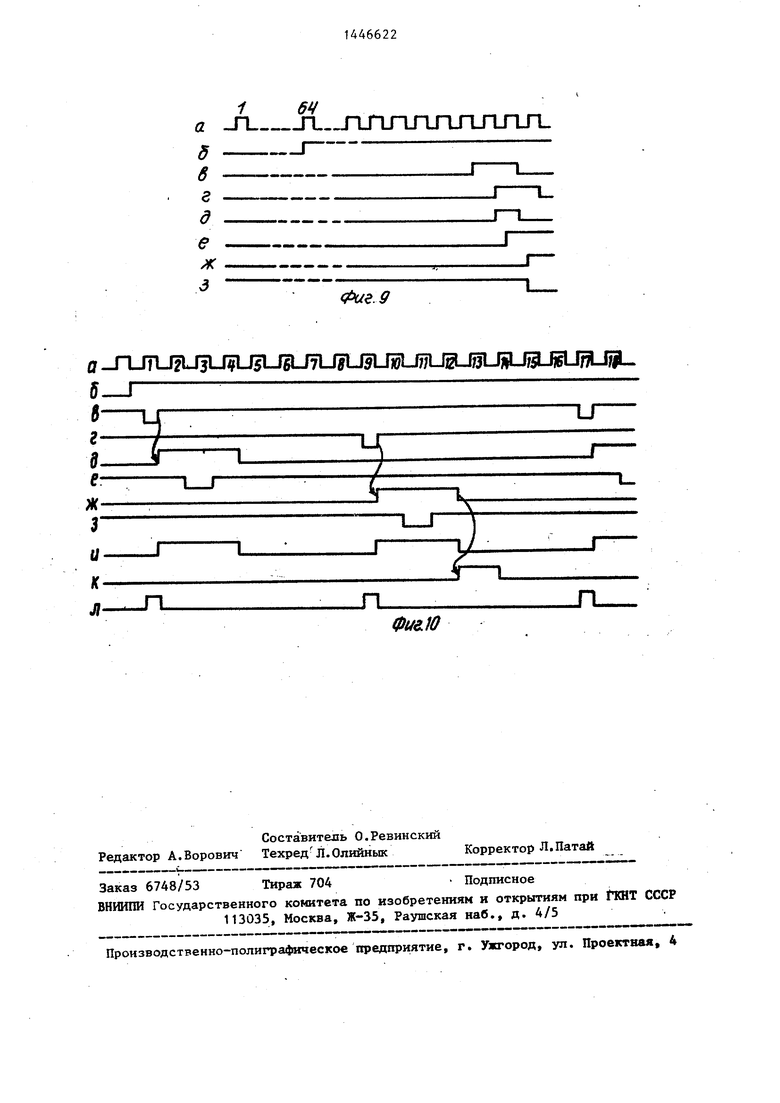

Первьй блок 8 формирования импульсов работает следующим образом. Во

0 время прохождения октетов преамбулы через приемный регистр 2 сдвига и блок 10 контроля на прямом выходе триггера 21 отсутствует сигнал разрешения записи данных в буферный ре5 гистр 3 и блок 5, а также разрешения работы второго блока 9 формирования импульсов и блока 11 подсчета слов в кадре, так как на третьем входе 24 (входе элемента И 19) отсутствует

0 сигнал разрешения с выхода блока 10 контроля. Такой сигнал (фиг.96) по-. ступает на третий вход 24 после того, как в блоке 8 будет осуществлен контроль всех восьми.октетов преамбулы, т.е-, после 64 тактовых импульсов (фиг.9а). При прохождении через регистр 2 сдвига октета поля ОНК на другие входы 23 элемента И 19 поступают последние смежные биты 11 этого

Q октета с выходов 7-го и 8-го разрядов регистра 2 сдвига (фиг.9в,г), элемент И 19 открывается (фиг.9д). Переключение триггеров 20 и 21 при этом происходит последовательно от

с очередных тактовых импульсов (фиг,9е- з), т.е. осуществляется задержка на два такта с тем, чтобы обе единицы октета поля ОНК вьшши из регистра 2 сдвига. В результате переключения триггера 21 на его прямом выходе будет сигнал разрешения работы блоков 3, 5, 9 и 11, а на инверсном выходе- сигнал запрета работы блока 10 контроля .

g В блоке 10 контроля (фиг.З) при приеме прес1мбулы с выходов регистра 2 сдвига каждый октет поступает на входы элемента 30 сравнения. Одновременно тактовые импульсы с выхода

5

0

блока 1 поступают на вход делителя 27 частоты, на второй вход которого подан разрешающий сигнал от блока 8 На выходе делителя 27 по каждому восьмому тактовому импульсу вьфаба- тьшается сигнал с перепадом 0-1, поступающий на вход формирователя 28 импульсов. По фронту этого перепада на выходе формирователя 28 формиру- ется отрицательный импульс, по переднему фронту которого через элемент ИЛИ 33 сбрасывается делитель 27 частоты, стробируется элемент 30 сравнения, срабатывает счетчик 29. При правильном чередовании битов в октете на выходе элемента 30 сравнения формируется импульс, поступающий на вход формирователя 31. Последний срабатывает и положительный импульс с его выхода подается в регистр 32, в который и записывается 1 по заднему фронту импульса с выхода формирователя 28 импульсов. При нарушении чередования битов в октете на выходе элемента 30 сравнения отсутствует импульс. Соответственно не срабатывает формиг-ватель 31 и в регистре 32 записывается О. Таким образом, октетам с правильным чередованием битов в регистре 32 соответствуют состояния 1, а правильному октету поля ОНК - О (так как в конце этого октета два последних смежных бита должны иметь состояния 11. Одновременно в счетчике 29.подсчитывается количество принятых октетов преамбулы (по каждому восьмому синхроимпульсу) и после фиксации всех октетов на его выходе появляется сигнал, снимающий запрет работы блока 8 После прохождения октета поля ОНК из блока 8 (фиг.9з) на вход элемента ИЛИ 33 проходит сигнал запрета работы делителя 27 частоты. Таким образом, в счетчике 29 будут зафиксированы, результаты счета принятых октетов преамбулы, а в регистре 32 - состояние соответствующих октетов. Для визуального контроля этих результатов к. выходам счетчика 29 и регистра 32 могут быть подключены соответствующие индикаторы.

Блок 11 подсчета слов в кадре (фиг. 5) начинает работать после прихода его на вход 54 сигигша разрешения с прямого выхода триггера 21 блока 8. С этого момента счетные импульсы, приходящие с выхода блока

9 формирования импульсов на вход 55 и соответствующие количеству принимаемых октетов, фиксируются в счетчике 51. Данные с первых пяти разря- дов счетчика 51 поступают на входы дешифратора 53, на выходах ко горого в десятичном виде вьоделяются импульсные сигналы, соответствующие номерам

принятых октетов с 1 по 31. Из них в блок 6 подаются импульсы со следующих выходов дешифратора: №№ 1 (первый октет поля АСН), 7 (первый октет поля АСИ), 15 (поле АСТДН), 16 (поле

АСТДИ) и 17 (поле управления), при этом данная группа выходов соединена с первьми выходами блока 11, с выходов №№ 13 и 14 дешифратора 53 в блок 7 подаются импульсы, по которым в

блоке 7 записьтаются соответствующие октеты, поступающие из буферного регистра 3: данные выходы дешифратора соединены с выходом 57 блока 11. Сигнал с 17-го выхода дешифратора 53

разрешает работу счетчика 52 (так как с 18-го октета начинается информационное поле кадра), который начинает подсчет октетов информационного поля принимаемого кадра. Таким образом, в счетчике 52, выходы которого соединены с выходом 58 блока 11, по окончании прохождения кадра будет отражено действительное число октетов информационного поля принятого

кадра.

В блоке 6 на входы регистров 59 (фиг.6) поступают октеты с выходов буферного регистра 3. В регистрах 59 последовательно запоминаются октеты, номера которых вьщелены дешиф- ратом 53 блока 11. В элементах 60 сравнения сравниваются содержание октетов, зафиксированных регистрами 59, с требуемыми значениями. Результат анализа октетов с выходов 17 может отражаться на индикаторах либо запоминаться и подвергаться дальнейшему анализу.

В блоке 7 (фиг.7) на входы 67 приходят октеты принимаемого кадра, на входы 68 которого поступают импульсы записи 13-го и 14-го октетов с вторых выходов 57 блока 11. В элементе 66 сравнения состояния регистров 64 и

65 сравниваются с действительно принятым числом октетов информационного поля, подсчитанным в счетчике 52 октетов, код которого поступает на третьи входы 69. Результат сравнения на

выходе 18 может быть использован для индикации результатов сравнения.

Работа блока 9 формирования импульсов (фиг.4) начинается после прихода на его вход 47 разрешающего сигнала из блока 8 (фиг.Эж). Этот сигнал подается на вход разрешения кольцевого счетчика Джонсона 37 с коэффициентом счета 16. В результате этого на выходах элементов И 38 и 39 импульсы оказьшаются сдвинуты относительно друг друга на восемь тактов (фиг. 10а.,б) . На выходе элемента ИЛИ 45 образуется последовательность импульсов, кратньпс восьмиJ число которых соответствует числу октетов, следующих после поля ОНК и записанных в буферный регистр Зо На фиг, 10и показаны эти имцульсы которые являются импульсами записи для буферного регистра 3 и счетным для блока 11„ Импульсы на выходах формирователейj которые формируются от задних фронтов импульсов с элементов И 38 и 39, подаются с выходов 49 блока 9 на входы блока 4 памяти. На фиг показаны формированные И1 гпульсы Коммутация данкых % а на фиг. - ,соответственно Запись нечетного бай-

та и Запись четного байта. На фиг. ЮдуЖ показаны импульсы Коммутация адреса и Сдвиг адреса. Данный набор импульсов на выходах 49 позволяет организовать 1б тиразряд- ный формат слов в блоке 4 памяти из восьмиразрядных; поступающих в блок 4 памяти с выходов буферного регистра 3,

Таким образом, устройство обеспечивает более полньш контроль принима емой информации,

Форм у л а изобретения

Устройство для контроля информации в многоканальной локальной вычислительной сети, содержащее блок декодирования у вход которого является информационным входом устройства; информационный и тактовый выходы блока декодирования подключены к одноименным входам регистра сдвига, первые выходы которого соединены с информа- ционными входами буферного регистра, выходы которого подключены к инфор- мационнь м входам блока п -мяти, выходы которого являются икформацконными

5

0

выходами устройства, первый блок сравнения, выход которого является первым контрольным входом устройства, отличающееся тем, что, с целью повьшения достоверности контроля информации, в устройство введены блок контроля, второй и третий блоки сравнения, блок подсчета слов в кадре, первый и второй блоки формирования импульсов, первый вход первого блока формирования импульсов объединен с тактовым входом первого блока сравнения и блока контроля и счетным входом второго блока формирования импульсов и подключен к тактовому выходу блока декодирования, вторые выходы регистра сдвига соединены с вторыми входами первого блока

0 формирования импульсов, первый выход которого подключен к разрешающим входам буферного регистра второго блока формирования импульсов, блока подсчета слов в кадре и первого блока

5 сравнения, информационный вход которого подключен к информационному выходу блока декодирования, информационные входы блока контроля подключены к первым выходам регистра сдвига, первый выход блока контроля соединен с третьим входом первого блока формирования импульсов, второй выход которого подключен к управляющему входу блока контроля, вторые выходы

5 которого являются вторь ми контрольными выходами устройства, первые выходы второго блока формирования импульсов соединены с адре.сными входами блока памяти, второй выход второ0 го блока формирования импульсов под- кда)чен к запрещающему входу буферного регистра и счетному входу блока подсчета слов в кадре, первые и вторые выходы которого соединены с ад5 ресными входами второго и третьего блоков сравнения, информационные входы которых объединены и подключены к выходам .буферного регистра, третьи выходы блока подсчета слов -в кад0 ре соединены с управляющими входами третьего блока сравнения, разрешаю- ащй вход блока памяти является входом управления считыванием устройства, выходы второго и третьего бло5Е

ков сравнения являются соответственно третьим и четвертым контрольными выходами устройства.

Фае. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения временных параметров станции | 1987 |

|

SU1429119A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для декодирования манчестерского кода | 1986 |

|

SU1383510A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2000 |

|

RU2179334C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ И ДОСТУПА К КАНАЛУ ДЛЯ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1992 |

|

RU2060539C1 |

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

Изобретение относится к вычислительной технике. Его использование в локальных вычислительных сетях с покадровой передачей информации манчестерским кодом позволяет повысить достоверность контроля информации. Устройство содержит блок 1 декодирования, ротор 2 сдвига, буферный регистр 3, блок 4 памяти и блок 5 сравнения. Благодаря введению бло-- ков 6, 7 сравнения, блоков 8, 9 фор- мирования нмпульсов, блока Ю контроля и блока 11 подсчета слов в кадре, обеспечивается контроль длины кадра и анализ служебной информации, подаваемой в кадре. 10 ил., 1 табл. (Л /J. 17

5S

iJ J3

27

55

ЪО

nr.

ifL

M

54

28

li

/

/if

J/

52

Фие.З

9

г4

50

0U9. 5

61

Ш

65}

-

-1

U

5Й5

U.JlUr jr jr S S S Jrifli.

f nJTJlJTXlJTJTJljr J

в Q 1 1

0I4B,8

«I

17

Ш

Фи.б

/6

а ППnJinJirLrLTLrLTL

5 в г д

е ж

3

Фие.9

ff-TTJTUBJIUipJsUetJ J U

,, J

ж

3

t;

7

.s

Л-

Фиг.Ю

| Устройство для обмена информацией между микро ЭВМ и периферийными устройствами | 1983 |

|

SU1195351A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Electronic Design, 1985, v.33, 2, p.173-180 | |||

| Патент США № 4393498, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-23—Публикация

1987-06-16—Подача