00 00

ел

Од

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретныхОб'ЕКТОВ | 1978 |

|

SU798852A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Сигнатурный анализатор | 1987 |

|

SU1429118A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для контроля радиоэлектронных блоков | 1987 |

|

SU1531100A1 |

Изобретение относится к технике контроля и диагностики цифровых систем передачи и обработки информации. Цель изобретения - повышение быстродействия путем устранения пауз на время сравнения сигнатур./Устр-во содержит регистры 2 и 3, дешифратор 4, индикатор 5, селектор 6, формир о- ватель 7 стробов, компаратор (К) 8 сигнатур. Введены следящий К 1 и фиксатор 9 нестабильности. К 1 содержит два сумматора по модулю два, D-триг- гер. К 8 выполнен в виде пятнадцатиразрядного блока сравнения. Фиксатор 9 содержит эл-т ИЛИ, инвертор,D-триг- гер, 1К-триггер. На вход селектора 6 поступают сигналы, определяющие длительность и положение во времени интервала измерения, а также выборки принимаемых данных, определяющих сигнал синхронизации. В селекторе 6 производится выбор активного фронта этих сигналов к-рые затем поступают в формирователь 7 стробов, а сигнал тактовой синхронизации - на входы регистра 2, К 1 и фиксатора 9. Сигнал с выхода 1К-триггера управляет соот- ветствуюпщм сегментом индикатора 5, определенным как индикатор нестабильности, горение к-рого указывает.на наличие сбоев во входных данных. 3 3.п. ф-лы, 2 ил. с (О (Л

Фи, 1

Изобретение относится к технике контроля и диагностики цифровых систем передачи и обработки информации.

Цель изобретения - повышение быстродействия путем устранения пауз на время сравнения сигнатур.

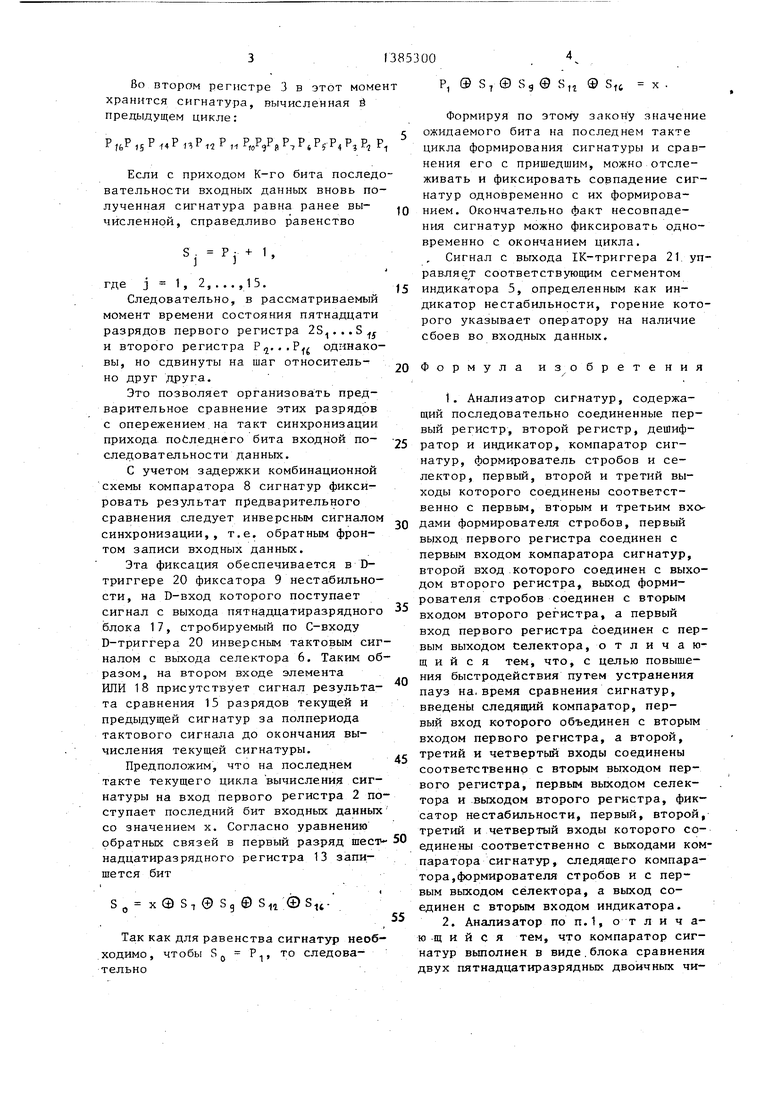

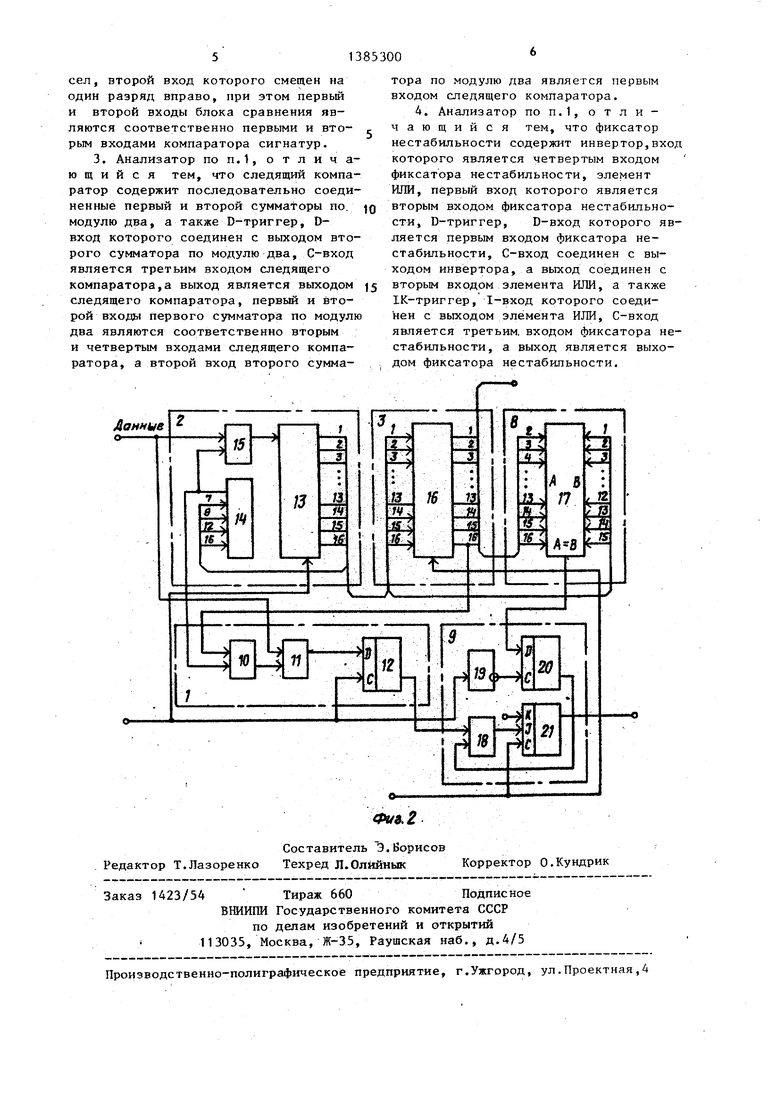

На фиг.1 представлена электрическая структурная схема анализатора сигнатур; на фиг.2 - пример конструктивного выполнения первого и второго регистров, компаратора сигнатур, следящего компаратора и фиксатора нестабильности.

Анализатор сигнатур (фиг.1) содержит следящий компаратор 1, первый 2 и второй 3 регистр), дешифратор 4, индикатор 5, селектор 6, формирователь 7 стробов, компаратор 8 сиг на тур, фиксатор 9 н естабильности. Следящий компаратор 1 (фиг.2) содержит первый 10 и второй 11 сумматоры по модулю два, D-триггер Л2.

Первый регистр 2 (фиг.2) содержит шестнадцатиразрядный регистр 13, первый 14 и второй 15 сумматоры по модулю два.

Второй регистр 3 (фиг.2) выполнен в виде шестнадцатиразрядного регистра 1 6.

Компаратор 8 сигнатур (фиг.2) выполнен в виде пятнадцатиразрядного блока 17 сравнения.

Фиксатор 9 нестабильности (фиг.2) содержит элемент ИЛИ 18, инвертор 19 D-триггер 20, 1К-триггер 21.

Аналиаатор сигнатур работает следующим образом.

На вход селектора 6 поступают сигналы, определяющие длительность и положение.во времени интервала из мерения, а также выборки принимаемых данных,, определяющих сигнал синхронизации. В селекторе 6 производится выбор активного фронта этих сигналов, которые затем поступают в формирователь 7 стробов, а сигнал тактовой синхронизации на входы первого регистра 2, с;ледящег.о компаратора 1 и фиксатора 9 нестабильности. В первом регистре 2 сигналы с выходов 7- 9-; 12 и 16-го разрядов шестнадцатиразрядного регистра 13 суммируются в первом сумматоре 14, а результат поступает на вход следящего компаратора 1 и сумматора 10, где они суммируются с последовательностью входных дантп.1х и поступают на вход шестнадца

тиразрядного регистра 13, Структура первого регистра 2 соответствует структуре шестнадцатиразрядного генератора сигнатур с образующим полиномом вида

h(x) -I- х + х + х + 1 ,

в котором происходит деление двоичной входной последовательности на инверсный полином вида

1 +

+ X + X

11

+ .Х

н

0

5

0

5

0

5

0

5

с получением шестнадцатиразрядного остатка, который и называется сигнатурой. Математически этот процесс описывается выражением

а(х) h (х) - Q(x) + S ,

где Q(X) - частное от деления; S - сигнатура.

Процесс вычисления заканчивается в конце интервала измерения, когда установившееся состояние разрядов шестнадцатиразрядного регистра 13 записывается во второй регистр 3. Значение вычисленной сигнатуры преобразуется дешифратором 4 в комбинацию управления -четырехразрядным семисег- ментным индикатором, входящим в состав индикатора 5, на котором 16 двоичных разрядов полученной сигнатуры представляются в виде четырех шестнадцатиричных цифр в соответствии с алфавитом - О, 1, 2, 3, 4, 5, 6,7, 8, 9, А, С, F, Н, Р, и. Дешифратор 4 представляет собой комбинационный кодопреобразователь двоичного кода в код семисегментного индикатора.

После того, как вновь вычисленная сигнатура перепишется во второй регистр 3, первый регистр 2 готов к началу вычисления новой сигнатуры. Последовательностьвходньгх данных, складываясь с сигналами обратных связей, записывается в первый разряд шестнадцатиразрядного регистра 13 с одновременным сдвигом остальных разрядов. Допустим, что в текущем цикле вычисляется сигнатура последовательности данных, стробируемых К тактами синхронизации. Пусть с приходом (К-1)-го такта состояние регистра 13 следующее

S S 58 14 S ть 11 11 S 5554538 5.

Во втором регистре 3 в этот момент хранится сигнатура, вычисленная и предыдущем цикле:

PjfeP,5P 4Pi Pi7PHP Pi P7PiPfP4PiP Pi

Если с приходом К-го бита последовательности входных данных вновь полученная сигнатура равна ранее вы- .« численной, справедливо равенство

15

Формируя по этому закону значение ожидаемого бита на последнем такте цикла формирования сигнатуры и сравнения его с пришедшим, можно отслеживать и фиксировать совпадение сигнатур одновременно с их формированием. Окончательно факт несовпадения сигнатур можно фиксировать одновременно с окончанием цикла.

Сигнал с выхода 1К-триггера 21 управляет соответствующим сегментом индикатора 5, определенным как индикатор нестабильности, горение которого указывает оператору на наличие сбоев во входных данных.

25

30

S-Pj-1,

где j 1, 2,...,15.

Следовательно, в рассматриваемый момент времени состояния пятнадцати разрядов первого регистра 2S... и второго регистра Р,. ..Р одннако- вы, но сдвинуты на шаг относитель- 20 Ф о р м у л а изобретения но друг друга. ,- .

Это позволяет организовать предварительное сравнение этих разрядов с опережением на такт синхронизации прихода последнего бита входной последовательности данных.

С учетом задержки комбинационной схемы компаратора 8 сигнатур фиксировать результат предварительного сравнения следует инверсным сигналом синхронизации,, т.е. обратным фронтом записи входных данных.

Эта фиксация обеспечивается в D- триггере 20 фиксатора 9 нестабильности, на D-вход которого поступает сигнал с выхода пятнадцатиразрядного блока 17, стробируемый по С-входу D-триггера 20 инверсным тактовым сигналом с выхода селектора 6. Таким образом, на втором входе элемента ИЛИ 18 присутствует сигнал результата сравнения 15 разрядов текущей и предыдущей сигнатур за полпериода тактового сигнала до окончания вычисления текущей сигнатуры.

Предположим, что на последнем такте текущего цикла вычисления сигнатуры на вход первого регистра 2 поступает последний бит входных данных со значением х. Согласно уравнению обратных связей в первый разряд шестнадцатиразрядного регистра 13 запишется бит

35

40

45

50

5д x®ST@Sg©Sii©S,t.

Так как для равенства сигнатур необходимо, чтобы SQ Р, то следовательно

«

5

Р, ® S © Sg © S, ® X .

Формируя по этому закону значение ожидаемого бита на последнем такте цикла формирования сигнатуры и сравнения его с пришедшим, можно отслеживать и фиксировать совпадение сигнатур одновременно с их формированием. Окончательно факт несовпадения сигнатур можно фиксировать одновременно с окончанием цикла.

Сигнал с выхода 1К-триггера 21 управляет соответствующим сегментом индикатора 5, определенным как индикатор нестабильности, горение которого указывает оператору на наличие сбоев во входных данных.

0 Ф о р м у л а изобретения ,- .

5

0

5

0

5

0

5

| Устройство для контроля дискретныхОб'ЕКТОВ | 1978 |

|

SU798852A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-30—Публикация

1986-07-09—Подача