Вход тактодьи импульсов

шина кодов unmepSam

&

(Л

Выхе

RnKoSI

Выход N

00

00

00 N3

Изобретение относится к радиоэлектронике и может быть использовано в устройствах обработки дискретной информации, измерительной технике, синхронизаторах.

Цель изобретения - повышение точное- ти формирования малых временных интервалов между выходными импульсами путем уменьшения времени восстановления программируемого многоканального таймера.

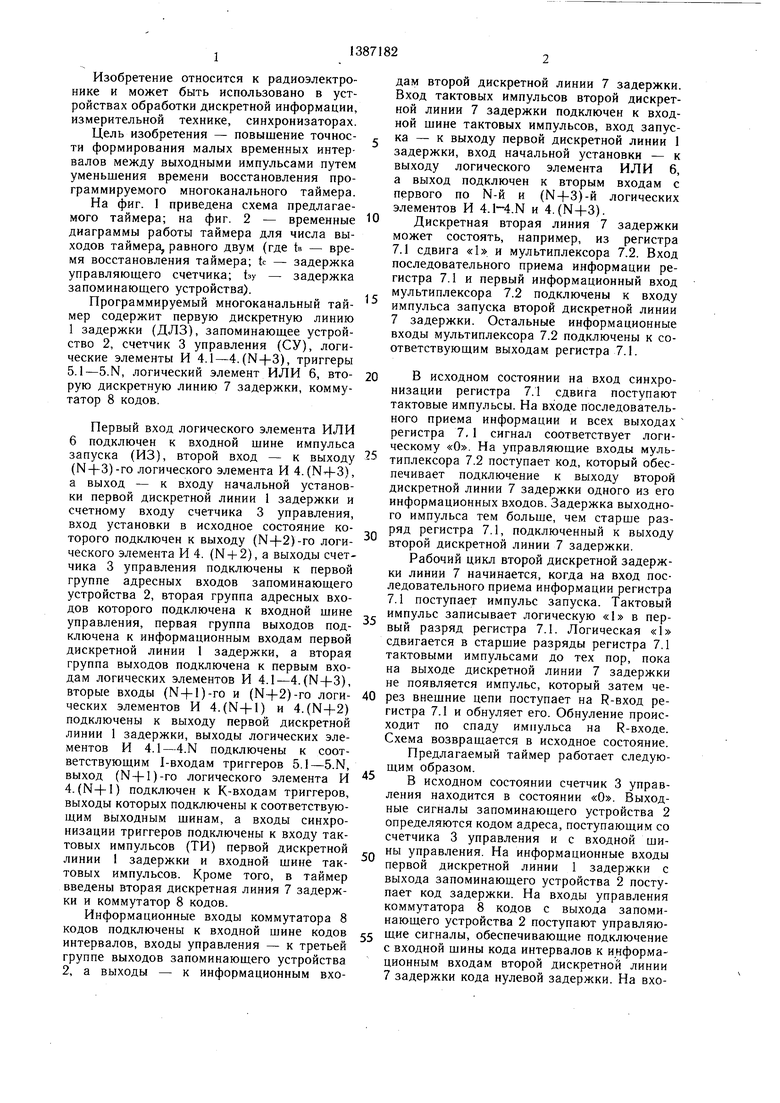

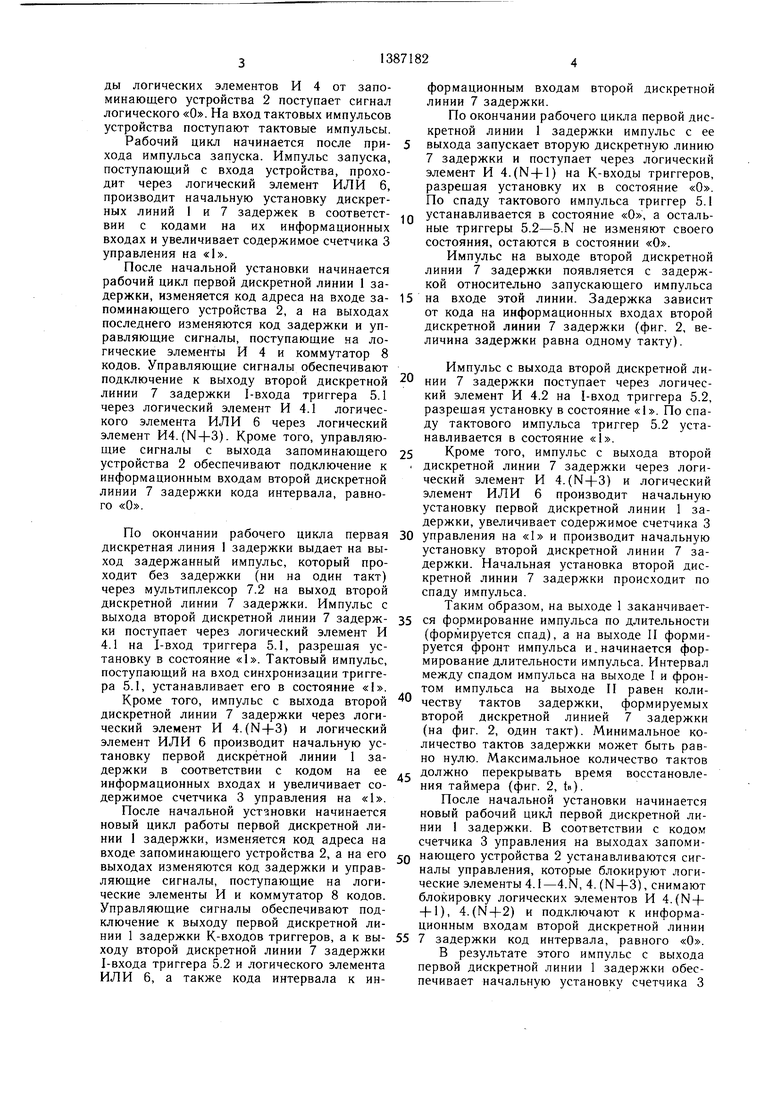

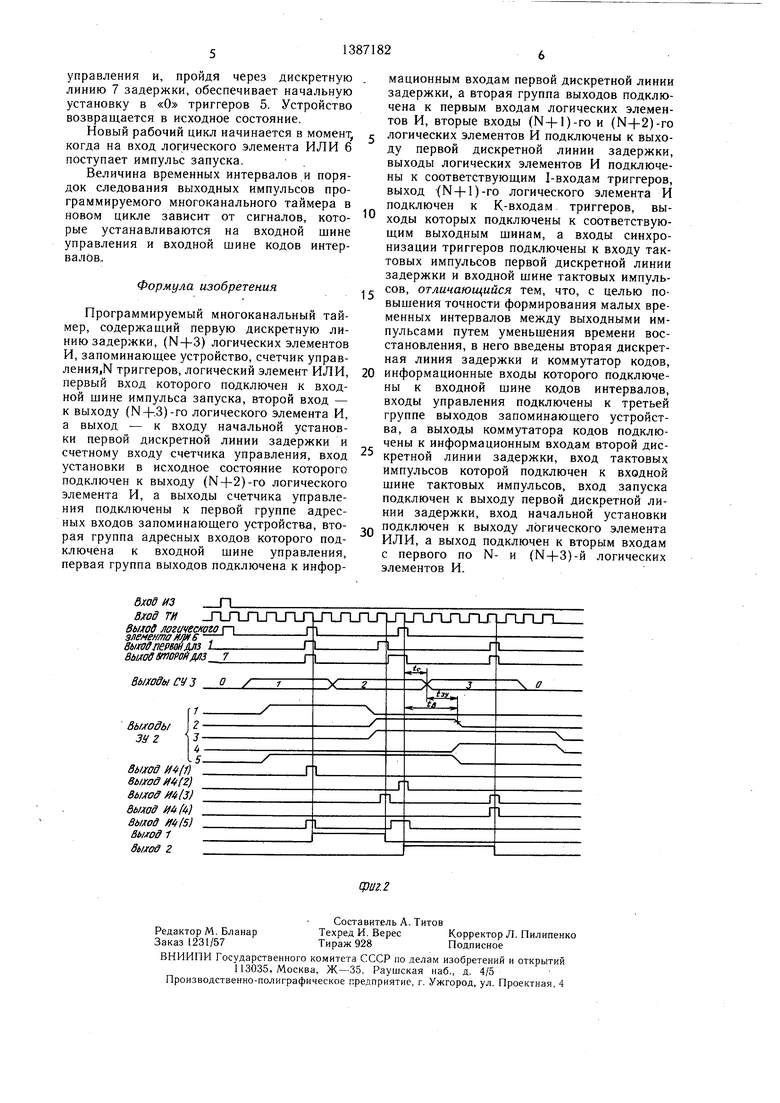

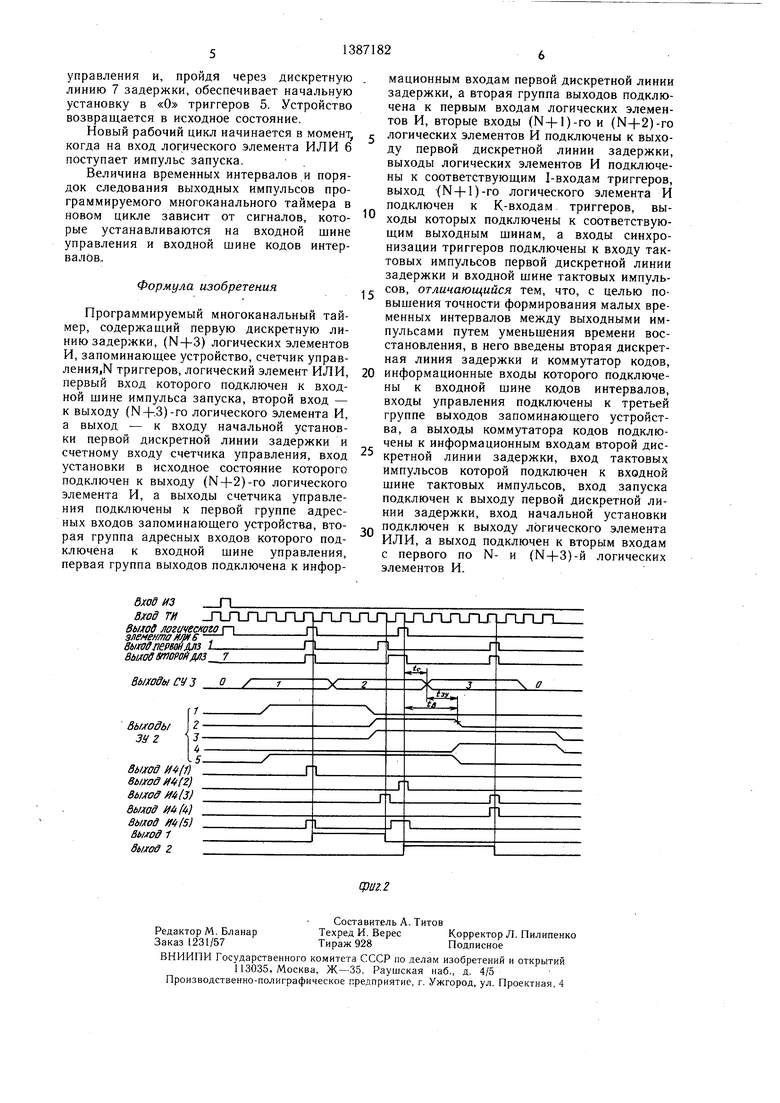

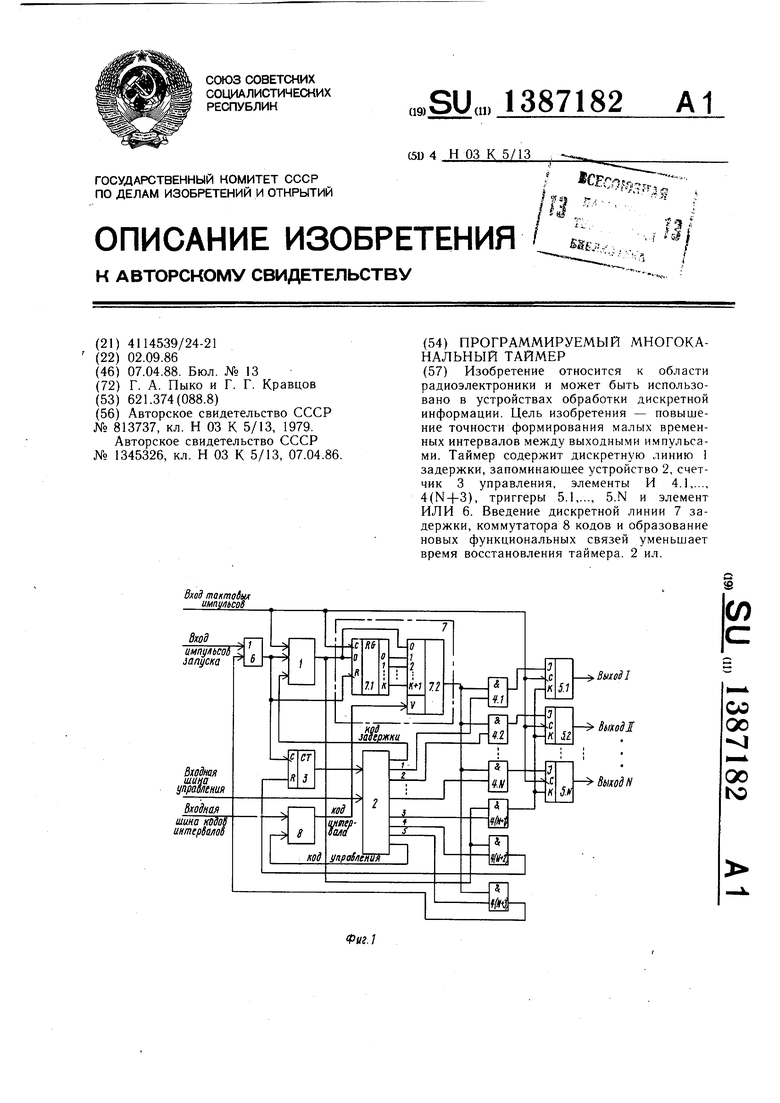

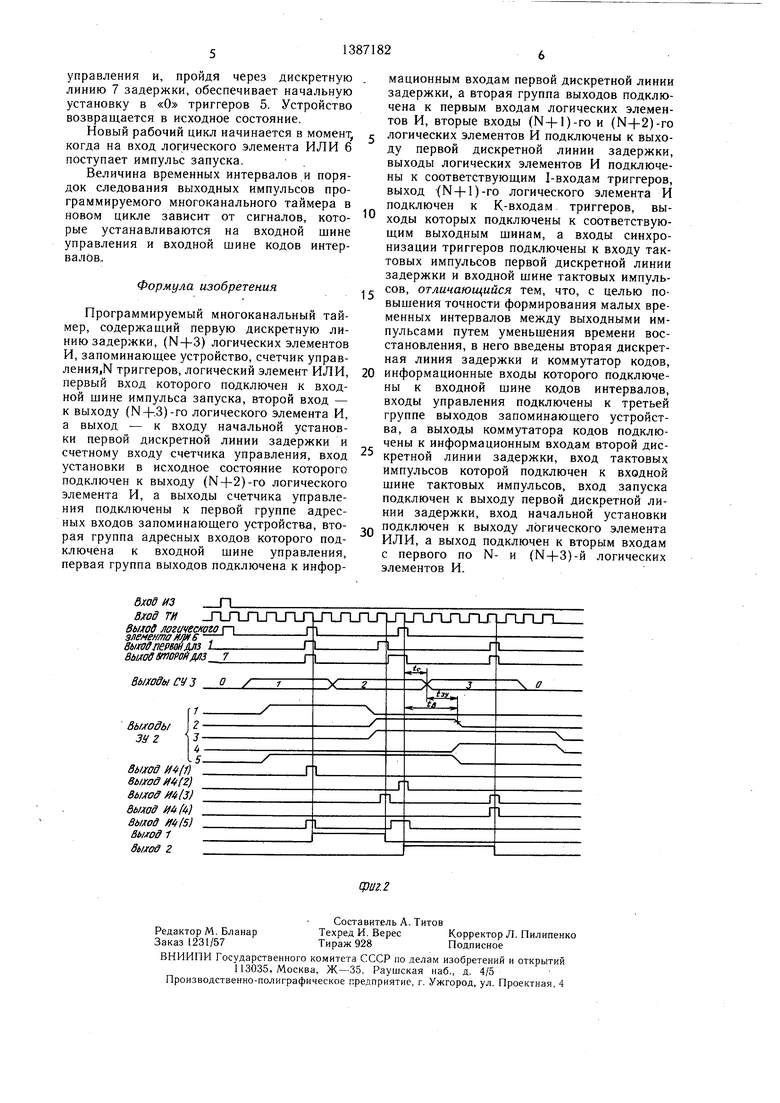

На фиг. 1 приведена схема предлагаемого таймера; на фиг. 2 - временные диаграммы работы таймера для числа выходов таймера, равного двум (где te - время восстановления таймера; tc - задержка управляющего счетчика; 1зу - задержка запоминающего устройства).

Программируемый многоканальный таймер содержит первую дискретную линию 1 задержки (ДЛЗ), запоминающее устройство 2, счетчик 3 управления (СУ), логические элементы И 4.1-4. (N-(-3), триггеры 5.1-5.N, логический элемент ИЛИ 6, вто- рую дискретную линию 7 задержки, коммутатор 8 кодов.

Первый вход логического элемента ИЛИ 6 подключен к входной шине импульса запуска (ИЗ), второй вход - к выходу (М4-3)-го логического элемента И 4. (N4-3), а выход - к входу начальной установки первой дискретной линии 1 задержки и счетному входу счетчика 3 управления, вход установки в исходное состояние которого подключен к выходу (N+2)-ro логического элемента И 4. (N + 2), а выходы счетчика 3 управления подключены к первой группе адресных входов запоминающего устройства 2, вторая группа адресных входов которого подключена к входной шине управления, первая группа выходов под- ключена к информационным входам первой дискретной линии 1 задержки, а вторая группа выходов подключена к первым входам логических элементов И 4.1-4.(N+3), вторые входы (N + l)-ro и (N+2)-ro логи- ческих элементов И 4.(N+1) и 4. (N+2) подключены к выходу первой дискретной линии 1 задержки, выходы логических элементов И 4.1-4.N подключены к соответствующим 1-входам триггеров 5.1-5.N, выход (N + l)-ro логического элемента И 4. (N+1) подключен к К-входам триггеров, выходы которых подключены к соответствующим выходным шинам, а входы синхронизации триггеров подключены к входу тактовых импульсов (ТИ) первой дискретной линии 1 задержки и входной щине тактовых импульсов. Кроме того, в таймер введены вторая дискретная линия 7 задержки и коммутатор 8 кодов.

Информационные входы коммутатора 8 кодов подключены к входной шине кодов интервалов, входы управления - к третьей группе выходов запоминающего устройства 2, а выходы - к информационным входам второй дискретной линии 7 задержки. Вход тактовых импульсов второй дискретной линии 7 задержки подключен к входной шине тактовых импульсов, вход запуска - к выходу первой дискретной линии 1 задержки, вход начальной установки - к выходу логического элемента ИЛИ 6, а выход подключен к вторым входам с первого по N-й и (Ы4-3)-й логических элементов И 4.1-4.N и 4.(Ы4-3).

Дискретная вторая линия 7 задержки может состоять, например, из регистра 7.1 сдвига «1 и мультиплексора 7.2. Вход последовательного приема информации регистра 7.1 и первый информационный вход мультиплексора 7.2 подключены к входу импульса запуска второй дискретной линии 7 задержки. Остальные информационные входы мультиплексора 7.2 подключены к соответствующим выходам регистра 7.1.

В исходном состоянии на вход синхронизации регистра 7.1 сдвига поступают тактовые импульсы. На входе последовательного приема информации и всех выходах регистра 7,1 сигнал соответствует логическому «О. На управляющие входы мультиплексора 7.2 поступает код, который обеспечивает подключение к выходу второй дискретной линии 7 задержки одного из его информационных входов. Задержка выходного импульса тем больше, чем старше разряд регистра 7.1, подключенный к выходу второй дискретной линии 7 задержки.

Рабочий цикл второй дискретной задержки линии 7 начинается, когда на вход последовательного приема информации регистра 7.1 поступает импульс запуска. Тактовый импульс записывает логическую «1 в первый разряд регистра 7.1. Логическая «1 сдвигается в старшие разряды регистра 7.1 тактовыми импульсами до тех пор, пока на выходе дискретной линии 7 задержки не появляется импульс, который затем через внешние цепи поступает на R-вход регистра 7.1 и обнуляет его. Обнуление происходит по спаду импульса на R-входе. Схема возвращается в исходное состояние.

Предлагаемый таймер работает следующим образом.

В исходном состоянии счетчик 3 управления находится в состоянии «О. Выходные сигналы запоминающего устройства 2 определяются кодом адреса, поступающим со счетчика 3 управления и с входной шины управления. На информационные входы первой дискретной линии 1 задержки с выхода запоминающего устройства 2 поступает код задержки. На входы управления коммутатора 8 кодов с выхода запоминающего устройства 2 поступают управляющие сигналы, обеспечивающие подключение с входной шины кода интервалов к информационным входам второй дискретной линии 7 задержки кода нулевой задержки. На входы логических элементов И 4 от запоминающего устройства 2 поступает сигнал логического «О. На вход тактовых импульсов устройства поступают тактовые импульсы.

Рабочий цикл начинается после прихода импульса запуска. Импульс запуска, поступающий с входа устройства, проходит через логический элемент ИЛИ 6, производит начальную установку дискретных линий 1 и 7 задержек в соответствии с кодами на их информационных входах и увеличивает содержимое счетчика 3 управления на «1.

После начальной установки начинается рабочий цикл первой дискретной линии 1 задержки, изменяется код адреса на входе запоминающего устройства 2, а на выходах последнего изменяются код задержки и управляющие сигналы, поступающие на логические элементы И 4 и коммутатор 8 кодов. Управляющие сигналы обеспечивают подключение к выходу второй дискретной линии 7 задержки 1-входа триггера 5.1 через логический элемент И 4.1 логического элемента ИЛИ 6 через логический элемент И4.(М+3). Кроме того, управляющие сигналы с выхода запоминающего устройства 2 обеспечивают подключение к информационным входам второй дискретной линии 7 задержки кода интервала, равного «О.

По окончании рабочего цикла первая дискретная линия 1 задержки выдает на выход задержанный импульс, который проходит без задержки (ни на один такт) через мультиплексор 7.2 на выход второй дискретной линии 7 задержки. Импульс с выхода второй дискретной линии 7 задержки поступает через логический элемент И 4.1 на J-вход триггера 5.1, разрешая установку в состояние «1. Тактовый импульс, поступающий на вход синхронизации триггера 5.1, устанавливает его в состояние «1.

Кроме того, импульс с выхода второй дискретной линии 7 задержки через логический элемент И 4. (N+3) и логический элемент ИЛИ 6 производит начальную установку первой дискретной линии 1 задержки в соответствии с кодом на ее информационных входах и увеличивает содержимое счетчика 3 управления на «1.

После начальной установки начинается новый цикл работы первой дискретной линии 1 задержки, изменяется код адреса на входе запоминающего устройства 2, а на его выходах изменяются код задержки и управляющие сигналы, поступающие на логические элементы И и коммутатор 8 кодов. Управляющие сигналы обеспечивают подключение к выходу первой дискретной линии 1 задержки К-входов триггеров, а к выходу второй дискретной линии 7 задержки 1-входа триггера 5.2 и логического элемента ИЛИ 6, а также кода интервала к информационным входам второй дискретной линии 7 задержки.

По окончании рабочего цикла первой дискретной линии 1 задержки импульс с ее

выхода запускает вторую дискретную линию 7 задержки и поступает через логический элемент И 4.(N+1) на К-входы триггеров, разрещая установку их в состояние «О. По спаду тактового импульса триггер 5.1

Q устанавливается в состояние «О, а остальные триггеры 5.2-5.N не изменяют своего состояния, остаются в состоянии «О.

Импульс на выходе второй дискретной линии 7 задержки появляется с задержкой относительно запускающего импульса

5 на входе этой линии. Задержка зависит от кода на информационных входах второй дискретной линии 7 задержки (фиг. 2, величина задержки равна одному такту).

Импульс с выхода второй дискретной ли0 НИИ 7 задержки поступает через логический элемент И 4.2 на 1-вход триггера 5.2, разрещая установку в состояние «1. По спаду тактового импульса триггер 5.2 устанавливается в состояние «1.

5 Кроме того, импульс с выхода второй . дискретной линии 7 задержки через логический элемент И 4.(N+3) и логический элемент ИЛИ 6 производит начальную установку первой дискретной линии 1 задержки, увеличивает содержимое счетчика 3

0 управления на «1 и производит начальную установку второй дискретной линии 7 задержки. Начальная установка второй дискретной линии 7 задержки происходит по спаду импульса.

Таким образом, на выходе 1 заканчивает5 ся формирование импульса по длительности (формируется спад), а на выходе II формируется фронт импульса и.начинается формирование длительности импульса. Интервал между спадом импульса на выходе I и фронтом импульса на выходе II равен коли0 цеству тактов задержки, формируемых второй дискретной линией 7 задержки (на фиг. 2, один такт). Минимальное количество тактов задержки может быть равно нулю. Максимальное количество тактов

г должно перекрывать время восстановления таймера (фиг. 2, te).

После начальной установки начинается новый рабочий цикл первой дискретной линии 1 задержки. В соответствии с кодом счетчика 3 управления на выходах запомиQ нающего устройства 2 устанавливаются сигналы управления, которые блокируют логические элементы 4.1-4.N, 4. (N+3), снимают блокировку логических элементов И 4.(N-f- -f-1), 4.(N+2) и подключают к информационным входам второй дискретной линии

5 7 задержки код интервала, равного «О. В результате этого импульс с выхода первой дискретной линии 1 задержки обеспечивает начальную установку счетчика 3

управления и, пройдя через дискретную линию 7 задержки, обеспечивает начальную установку в «О триггеров 5. Устройство возвращается в исходное состояние.

Новый рабочий цикл начинается в момент, когда на вход логического элемента ИЛИ 6 поступает импульс запуска.

Величина временных интервалов и порядок следования выходных импульсов программируемого многоканального таймера в новом цикле зависит от сигналов, которые устанавливаются на входной шине управления и входной шине кодов интервалов,.

Формула изобретения

Программируемый многоканальный таймер, содержащий первую дискретную линию задержки, (N-f-S) логических элементов И, запоминающее устройство, счетчик управ- ления.М триггеров, логический элемент ИЛИ, первый вход которого подключен к входной шине импульса запуска, второй вход - к выходу (N-|-.3)-ro логического элемента И, а выход - к входу начальной установки первой дискретной линии задержки и счетному входу счетчика управления, вход установки в исходное состояние которого подключен к выходу (N+2)-ro логического элемента И, а выходы счетчика управления подключены к первой группе адресных входов запоминающего устройства, вторая группа адресных входов которого подключена к входной шине управления, первая группа выходов подключена к инфор0

мационным входам первой дискретной линии задержки, а вторая группа выходов подключена к первым входам логических элементов И, вторые входы (N+l)-ro и (N+2)-ro логических элементов И подключены к выходу первой дискретной линии задержки, выходы логических элементов И подключены к соответствующим 1-входам триггеров, выход (N+l)-ro логического элемента И подключен к К-входам триггеров, выходы которых подключены к соответствующим выходным шинам, а входы синхронизации триггеров подключены к входу тактовых импульсов первой дискретной линии задержки и входной щине тактовых импульс сов, отличающийся тем, что, с целью повышения точности формирования малых временных интервалов между выходными импульсами путем уменьшения времени восстановления, в него введены вторая дискретная линия задержки и коммутатор кодов,

0 информационные входы которого подключены к входной щине кодов интервалов, входы управления подключены к третьей группе выходов запоминающего устройства, а выходы коммутатора кодов подключены к информационным входам второй дис кретной линии задержки, вход тактовых импульсов которой подключен к входной щине тактовых импульсов, вход запуска подключен к выходу первой дискретной линии задержки, вход начальной установки

Q подключен к выходу логического элемента ИЛИ, а выход подключен к вторым входам с первого по N- и (М+3)-й логических элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный таймер | 1986 |

|

SU1345326A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1104667A1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1674132A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Устройство для воспроизведения функций | 1987 |

|

SU1411787A1 |

Изобретение относится к области радиоэлектроники и может быть использовано в устройствах обработки дискретной информации. Цель изобретения - повышение точности формирования малых временных интервалов между выходными импульсами. Таймер содержит дискретную линию 1 задержки, запоминающее устройство 2, счетчик 3 управления, элементы И 4.1,..., 4(N+3), триггеры 5.1,..., 5.N и элемент ИЛИ 6. Введение дискретной линии 7 задержки, коммутатора 8 кодов и образование новых функциональных связей уменьшает время восстановления таймера. 2 ил.

| Многоканальный таймер | 1979 |

|

SU813737A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальный таймер | 1986 |

|

SU1345326A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-07—Публикация

1986-09-02—Подача