(О

Фи.1

функций. Цель изобретения - расширение функциональных возможностей в части вычисления широкого класса функций, аппроксимироваиньк в виде цепной Дроби, Устройство содержит входы 1.1, 1.2, 1.3, 1.4 начальных значений соответственно первого,, второго, тре- tbero и четвертого итерационных ко- зффициентов, вход 1„5 числа итерации, Вход 1.6, аргумента, регистры 2.1, 4.2, 2.3, 2.4, 2.5 соответственно 4 первого по пятый, умножители 3.1, 3.2, 3.3, 3.4 соответственно с перво-. Ро по четверт ый, первый 4,1 и второй 4.2 сумматоры, блок 5 синхронизации,, Счетчик 6, блок 7 дсшения, схему 8 Сравнения, первый 9.1 и второй 9.2 блоки формирования итерационных коэффициентов, выход 10 результата. Вычисление цепной дроби осуществляется за п тактов работы устройства, количество которых без одного поступает на вход схемы сравнения, выход которой управляет схемой синхронизации. Ввд реализуемой функции опреде- ляется выражениями на каждом шаге работы устройства, реализуемыми первым и вторым блоками вычисления итерационных коэффициентов Время работы устройства зависит от количества элементов цепной дроби п и от времени вычисления промежуточных данных на каждом шаге. Увеличение точности осуществляется путем увеличения числа тактов работы устройства. 2 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1434427A1 |

| Устройство для перемножения матриц | 1989 |

|

SU1839262A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

Изобретение относится к области вычислительной техники, предназначено для вычисления различных функций и может быть использовано в микропроцессорных системах в качестве арифметического расширителя. Известные устройства, осуществляющие вычисление функции в асинхронном режиме, имеют ограниченный набор реализуемьпс

1

Изобретение относится к вычислительной технике и предназначено для вычисления различных функций и может быть использовано в микропроцессор- .ных системах в качестве арифметического расширителя.

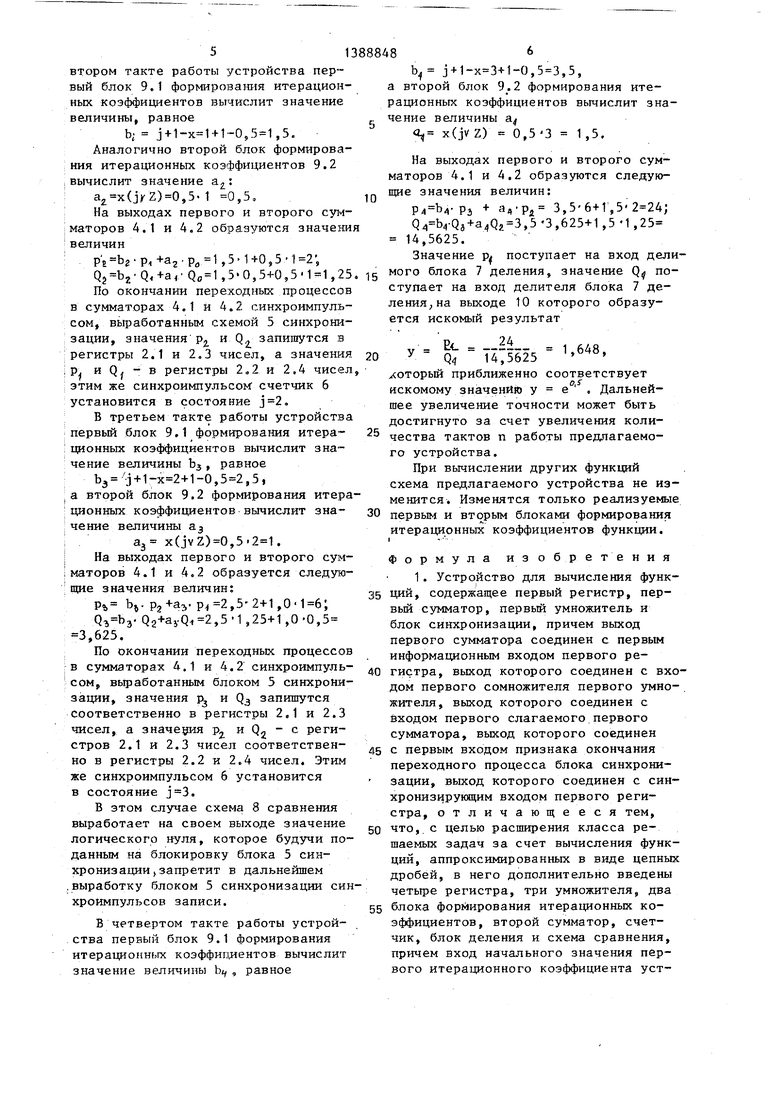

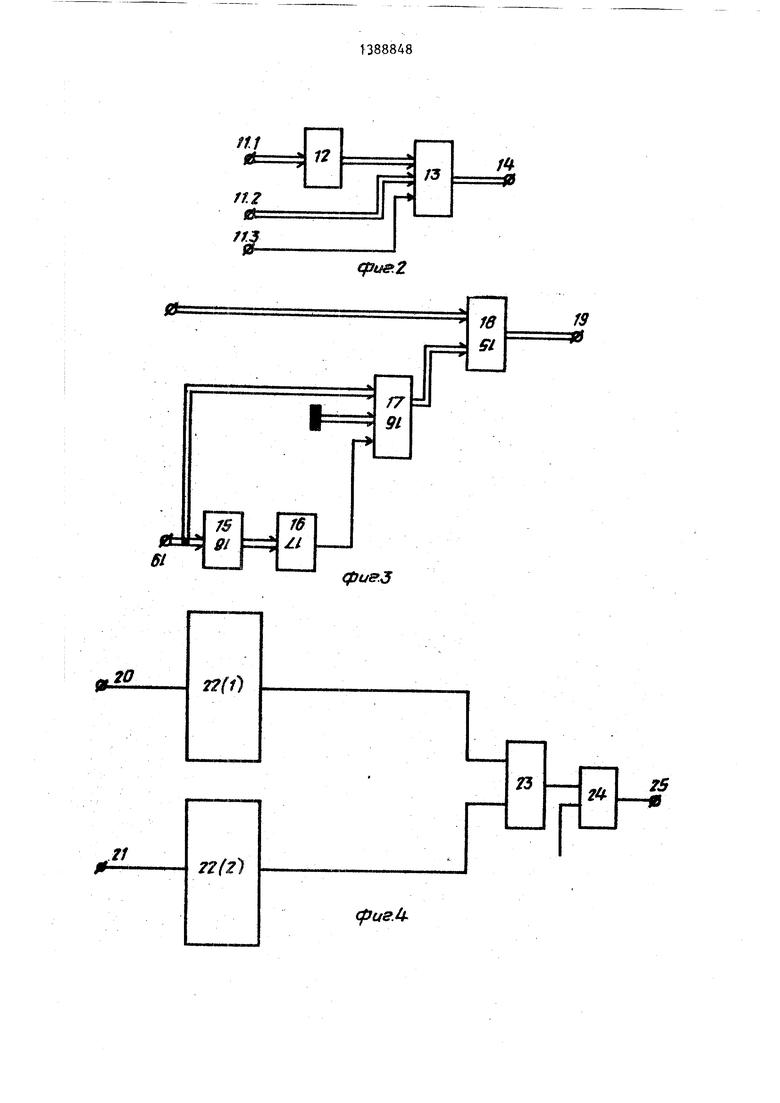

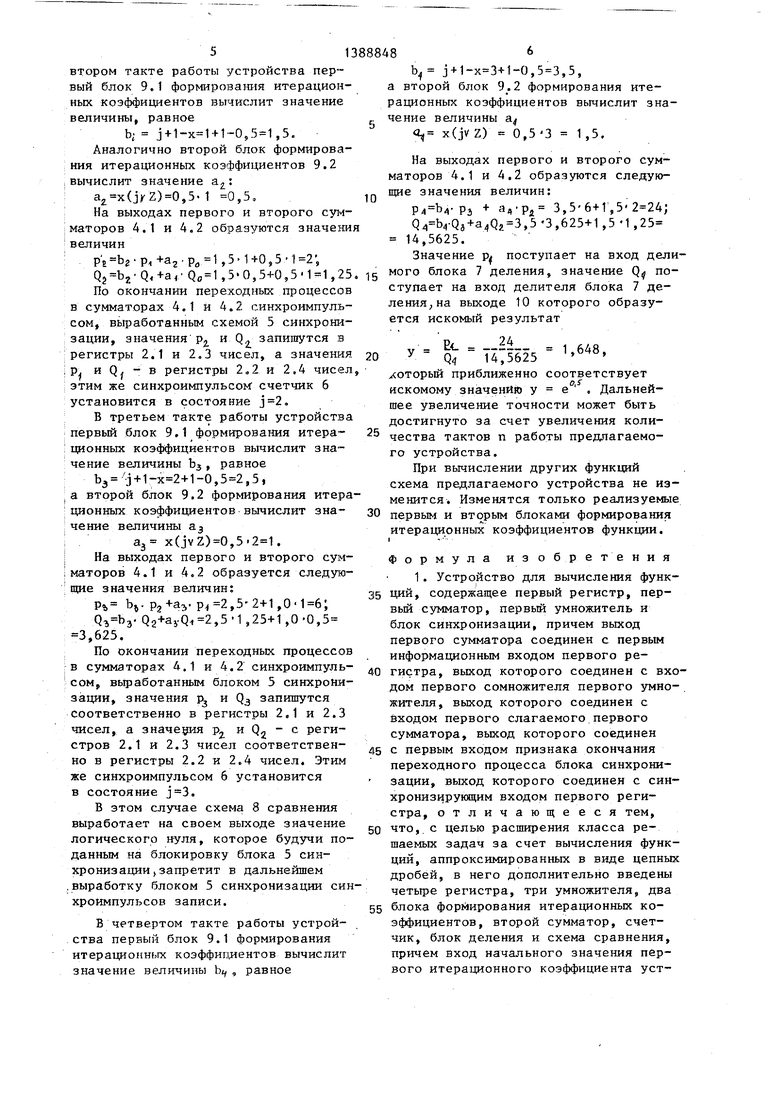

Целью изобретения является расширение класса решаемых задач за счет вычисления функций, аппроксимирован- ых в виде цепных дробей На фиг. 1 представлена функцио- альная схема предлагаемого устрой- iTBa; на фиг. 2 - схема первого бло- Аа формирования итерационных коэффициентов; на фиг. 3 - схема второго блока формирования итерационных коэффициентов; на фиг. 4 - схема блока Синхронизации.

Устройство содержит входы 1.1, 1.2, 1.3, 1.4 начальшлх значений первого, второго, третьего и четвертого итерационных коэффициентов, вход 1.5 числа итерации, вход 1,6 аргумента, регистры 2.1, 2.2, 2,3, 2.4, 2.5 соответственно с первого по пятый, ножители 3.1, 3.2, 3.3, 3.4 соответственно с первого по четвертый, первый 4„1 и второй 4.2 сумматоры, блок 5 синхронизации, счетчик 6, блок 7 деления, схему 8 сравнения, первьиа 9.1 и второй 9.2 блоки формирования

терационных коэффициентов, вход 10 езультата.

Первый блок формирования итерационных переменных содержит первый 11.1 второй 11.2 информационные входы, йход 11.3 задания константы, преобразователь 12 прямого кода в дополнительный, сумматор 13, выход 14.

Второй блок формирования итераци- онных переменных содержит элементы НЕ 15 группы, элемент И 16, элемент ИЛИ 17 группы, умножитель 18, вы и ход 19.

Схема синхронизации содержит пер- вый 20 и второй 21 входы признака окончания переходного процесса, первый 22.1 и второй 22.2 формироватеи импульсов, элемент ШШ-НЕ 23, элемент И 24, выход 25.

Устройство функционирует следующим образом.

Вычисление функции, аппроксимированной в виде цепной дроби

,+

ь:,--§i.--

ь + SJ-:-

Z. b + .. . + а„

ь:

(1)

осуществляется на предлагаемом устройстве за п тактов работы, где п 3 1388848

число звеньев цепной дроби, в соот-Z - определяется следуннцей функветствии с рекурентным соотношением :цией:

Z 2- LLb--JL t -Ek.-i- , (2)г Ь если j 0;

Q. b,.Q., +a-.Q. 5 z , (6).

где i 1,2,..., п.CO, если ,

Вход 1.1 предназначен для заданиязнак v определяет поразрядную дизьюнкзначения р,,, а вход 1.2 - для зада-ц ю двух величин j и Z.

ния :значения р.,, вход 1.3 предназна-ю Рассмотрим вычисление функции

чей для задания значения Q, а.-вход„а конкретном примере при ,5. В

цепной дроби (1) принимают следующиер j, g регистр 2.2 числа с вхозначения:15 да 1.2 заносится величина Р. 1. В

р |.j . Q . р Q Qрегистр 2.3 числа входа 1,3 заносит - 1(,д величина Qg 1 . В регистр числа

и в процессе подготовки устройства2.4 с входа 1.4 заносится величина

к работе заносятся в соответствующиеQ 0. Значение аргумента х постурегистры чисел 2.1-2.4.зо пает на вхЬд 1.6 устройства и по синРегистр 2.5 служит Для храненияхроимпульсу, поступающего на вход 1.7

переменной X, на основании которойзаносится в регистр 2.5 числа. Однов первом блоке 9.1 формирования ите-временно по указанному синхроимпульрационньк коэффициентов определяет- у счетчик 6 устройства устанавливася значение коэффициента Ь, во вто-25 ется в нуль. На вход устройства 1.5

ром блоке 9.2 .формирования итераци-поступает величина равная .

онных коэффициентов определяется зна-первый блок 9.1 формирования итечение коэффициента а, где индекс iрационных коэффициентов вычислит знаопределяется состоянием счетчика 6.чение величины, равное:

Вход устройства 1.6 предназначен длязо b j+1-x 0+1-0 5,

задания переменной X. Вход 1.5 пред- рой формирователь Ч. 2 итерациназначен для задания числа п-1.„„jj ix коэффициентов вычислит зйаченйе

Работу схемы предлагаемого устрой-величины, равное

ства проиллюстрируем на примере вьм:, g x(jvZ)0 5

числения функции у е, представлен- так как .

ной в виде цепной дроби На выходах умножителей З.ЬЗ.4

X образуются следукхцие величины: на

у-1+ -выходе умножителя 3.1: Ъ ,5«1

1-х + (3) 0,5j на выходе умножителя 3.2:

2-х -ь +:(. 0,5-1 0,5; на выходе умно3-Х+..---- -жителя 3.3: Ъ,- Qo 0,5-1 0,5; на

выходе умножителя 3.4: Q О,5«0в

при П 4. О.

В соответствии с этим первый блокНа выходе первого сумматора 4.1

циентов определяет значения коэффи-+ р 0,5+0,5 1, а на выходе

циентов bj- на основании выражения. второго сумматора 4.2 образуется

значение Q, а. Q 0,5.

-J На этом первый такт ра боты устрой- а второй блок 9.2 формирования итера- во ства закончен. По окончании процесционных коэффициентов реализует выра-сов в сумматорах 4.1 и 4.2 схема 5

жениесинхронизации выработает синхроим,пульс, который установит счетчик 6 в

i- xvjv/c;, }единичное состояние (j 1) и произвегде j - состояние счетчика 6, ( запись величины р в регистр

0..., п-1),2.1 числа, а значение величины р X - значение аргумента, поступаю-в регистр 2.2 числа, величины - Qj

щее на вход 1.6 предлагаемогов регистр 2.3 числа, а значение веустройства, -личины Q., в регистр 2.4 числа. На

втором такте работы устройства первый блок 9.1 фop иpoвaния итерационных коэффициентов вычислит значение величины, равное

Ь; j+1-x 1-H-0,,5.

Аналогично второй блок формирования итерационных коэффициентов 9.2 вычислит значение а,:

(1г2)0,5 1 0,5,

На выходах первого и второго маторов 4.1 и 4.2 образуются значения величин

.+аг-р,1,5 иО,

Qj b2 Q4+a4 Qo 1,50,5+0,,25,

По окончании переходных процессов в сумматорах 4.1 и 4.2 синхроимпульсом, выработанным схемой 5 синхронизации, значения р. запишутся JB регистры 2.1 и 2,3 чисел, а значения р. и Q, - в регистры 2,2 и 2.4 чисел,

;ЭТИМ же синхроимпульсом счетчик 6 установится в состояние ,

; в третьем такте работы устройства

:первый блок 9.1 формирования итера; ционных коэффициентов вычислит значение величины Ъз, равное + 1-х 2+1-0,,5,

,а второй блок 9.2 формирования итера;ционных коэффициентов вычислит зна; чение величины а.

. а x(jvZ)0,.

I На выходах первого и второго сум; маторов 4.1 и 4.2 образуется следую: щие значения величин;

Р% Ц.pг+aзp 2,, Q,b3- Q2+aj.,51 ,25+1,0-0,5 3,625.

По окончании переходных процессов

:В сумматорах 4.1 и 4.2 синхроимпуль- coMj выработанным блоком 5 синхронизации, значения р и Q запишутся соответственно в регистры 2,1 и 2.3 чисел, а значения р и Qj - с регистров 2.1 и 2.3 чисел соответственно в регистры 2.2 и 2.4 чисел. Этим же синхроимпульсом 6 установится в состояние .

В этом случае схема 8 сравнения выработает на своем выходе значение логического нуля, которое будучи поданным на блокировку блока 5 синхронизации запретит в дальнейшем

.выработку блоком 5 синхронизации синхроимпульсов записи.

В четвертом такте работы устройства первый блок 9.1 формирования итерационных коэффипиентов вычислит значение величины Ц, равное

Ь j + 1-x 3-H-0,,5, а второй блок 9.2 формирования итерационных коэффициентов вычислит значение величины а

0 x(jv Z) 0,53 1 ,5,

На выходах первого и второго сумматоров 4.1 и 4.2 образуются следующие значения величин:

Р4 Ь4-РЭ + a,.pj 3,5 6-И,

Q4 b4-Q8+a4Q2 3,53,625+1,5 -1,25 14,5625.

Значение р поступает на вход делимого блока 7 деления, значение Q поступает на вход делителя блока 7 де- лениЯ;На выходе 10 которого образуется искомый результат

20

1475625

х оторый приближенно соответствует искомому значению у е . Дальнейшее увеличение точности может быть достигнуто за счет увеличения количества тактов п работы предлагаемого устройства.

При вычислении других функций схема предлагаемого устройства не изменится. Изменятся только реализуемые

первым и вторым блоками формирования

итерационных коэффициентов функции.

Формула изобретения

с первым входом признака окончания переходного процесса блока синхронизации, выход которого соединен с синхронизирующим входом первого регистра, отличающееся тем,

что,, с целью расширения класса решаемых задач за счет вычисления функций, аппроксимированных в виде цепных дробей, в него дополнительно введены четыре регистра, три умножителя, два

блока формирования итерационных коэффициентов, второй сумматор, счетчик, блок деления и схема сравнения, причем вход начального значения первого итерационного коэффициента устройства соединен с вторым информационным входом первого регистра, входы начальных значений второго, третьего и четвертого итерационных коэф- фивдентов устройства соединены с первыми информационными входами соответственно второго, третьего и четвертого регисфров, вход аргумента устройства соединен с информацион- ньм входом пятого регистра, вькод которого соединен с первыми информационными входами первого и второго блоков формирования итерационных коэффициентов, выходы которых соединены соответственно с входом второго сомножителя первого умножителя и с входом первого сомножителя второго умножителя, вход второго сомножителя которого соединен с выходом второго реги- стра, второй информационный вход которого соединен с выходом первого регистра, выход второго умножителя соединен с входом второго слагаемого

первого сумматора, выход которого со- 25 с входом первого слагаемого сумматоединен с входом делимого блока деления, вход делителя которого соединен с выходом второго сумматора, входы первого и второго слагаемых которого соединены соответственно с выходами третьего и четвертого умножителей, входы первых сомножителей которых соединены с выходами соответственно первого и второго блоков формирования итерационных коэффициентов входы вторых сомножителей третьего и четвертого умножителей соединены с выходами соответственно третьего и четвертого регистров, информационный вход четвертого регистра соединен с выходом третьего регистра, второй информационный вход которого соединен с выходом второго сумматора, вторые информационные входы первого и второго блоков формирования итерационных коэффициентов объединены с входами первого аргумента схемы сравнения и соединены с выходом счётчика, счетный вход которого соединен с выходом блока синхронизации, второй вход признака окончания переходного процесса которого соединен с выходом второго сумматора, вход ос танова блока синхронизации соединен с выходом признака Равно схемы сравнения, вход второго аргумента которой соединен с входом числа итерации устройства, выход блока синхронизации соединен с синхронизирующими входами регистров с первого по четвертый, вход сброса счетчика соединен с установочным входом устройства и синхронизирующим входом пятого регистра, выход блока деления является выходом результата устройства.

2, Устройство по п. 1, о т л и- чающееся тем, что, с целью

к

вычисления выражения У Е , первый блок формирования итеращюнных коэффициентов содержит преобразователь прямого кода в дополнительный и сумматор, причем первый и второй информационные входы блока соединены соответственно с входом преобразователя прямого кода в дополнительный и

0

5

ра, входы второго и третьего слагаемых которого соединены соответственно с выходом преобразователя прямого кода .в дополнительный и с входом задания константы блока, выход сумматора соединен с выходом блока.

Q первого сомножителя умножителя, вход второго сомножителя которого соединен с выходами элементов ИЛИ группы, первые входы элементов ИЛИ группы соединены с вторым информационным

с входом блока и с входами элементов НЕ группы, выходы которых соединены с входами элемента И, выход которого соединен с первым входом второй группы входов элементов ИЛИ группы, второй вход второй группы входов элементов ИЛИ группы соединен с шиной логического нуля.

O

0

rs

91

Г6 Zl

61

20

72(ll

cpus-.Z

18 Si

19

че

/7 91

фи&.3

| Смолов В.Б | |||

| Функциональные преобразователи информахщи | |||

| Л.: Энерго- йздат, 1981, с | |||

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для решения алгебраических уравнений | 1984 |

|

SU1259286A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-06-16—Подача