Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах.

Цель изобретения - увеличение быстродействия за счет одновременного доступа к памяти и реализации сеансов обмена с учетом приоритета машин и операций о

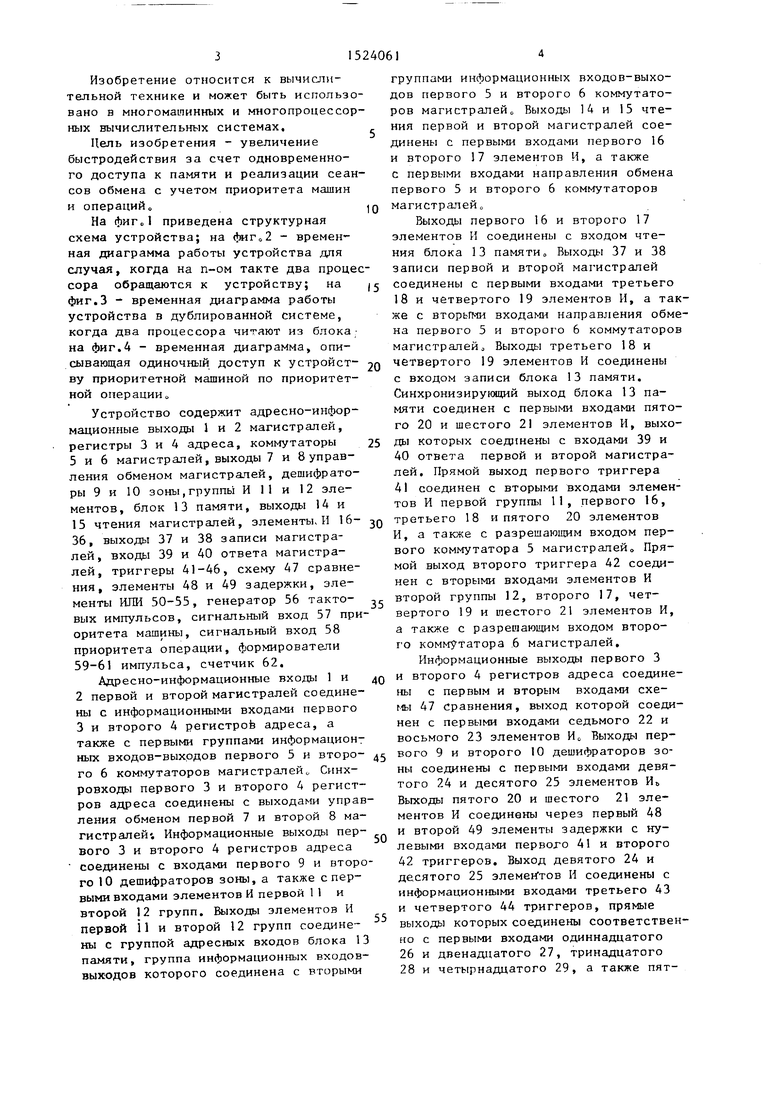

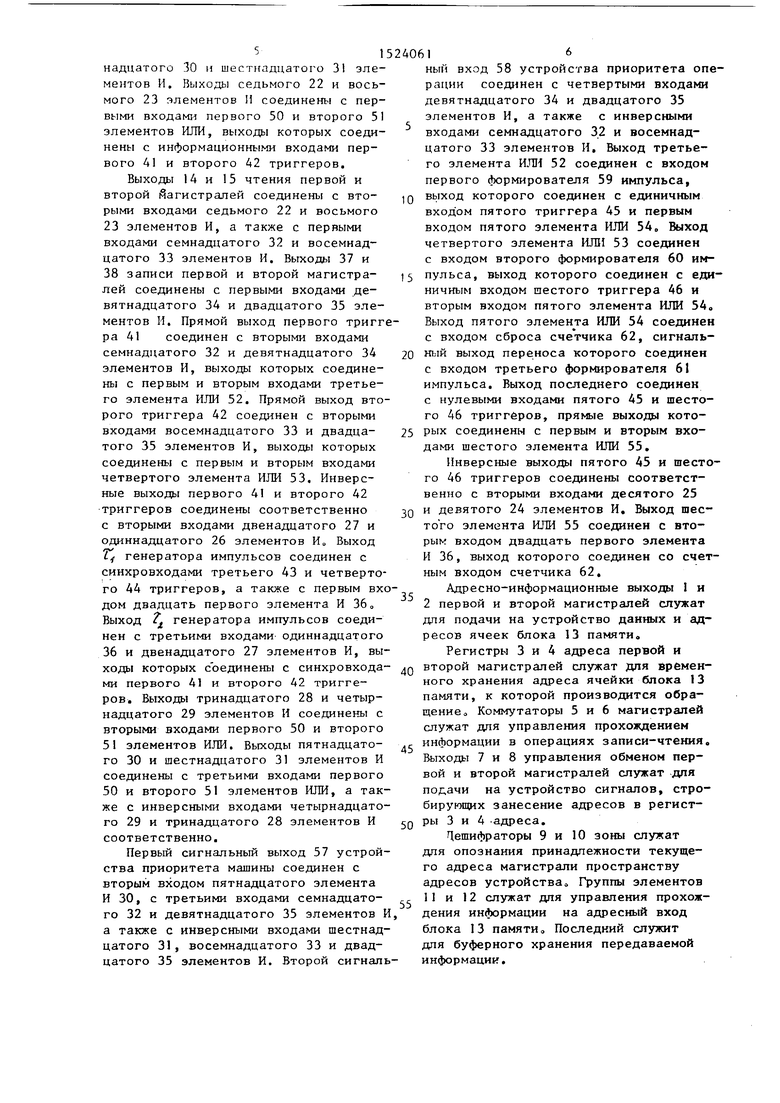

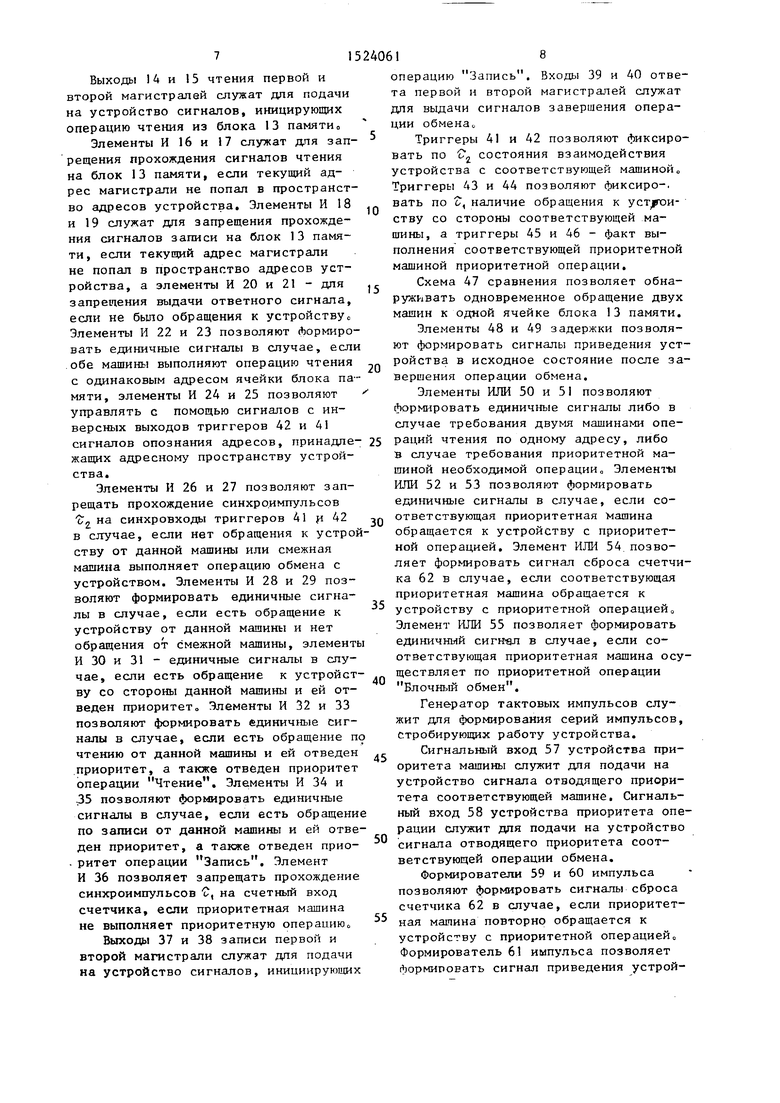

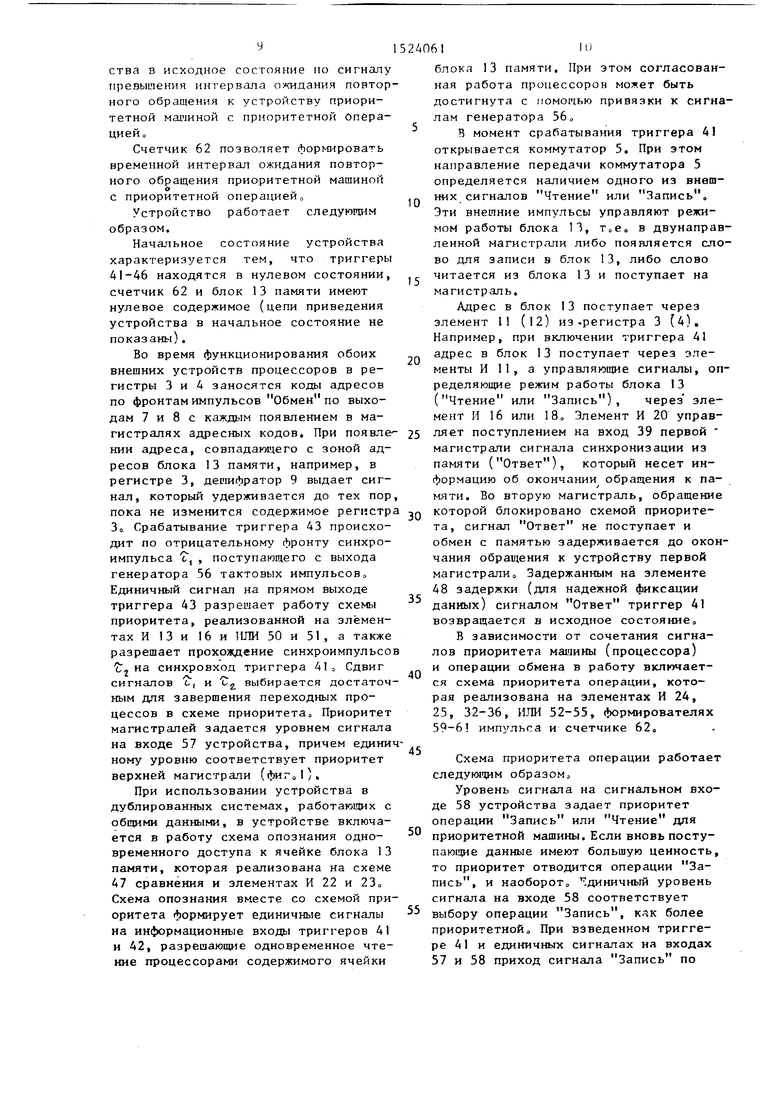

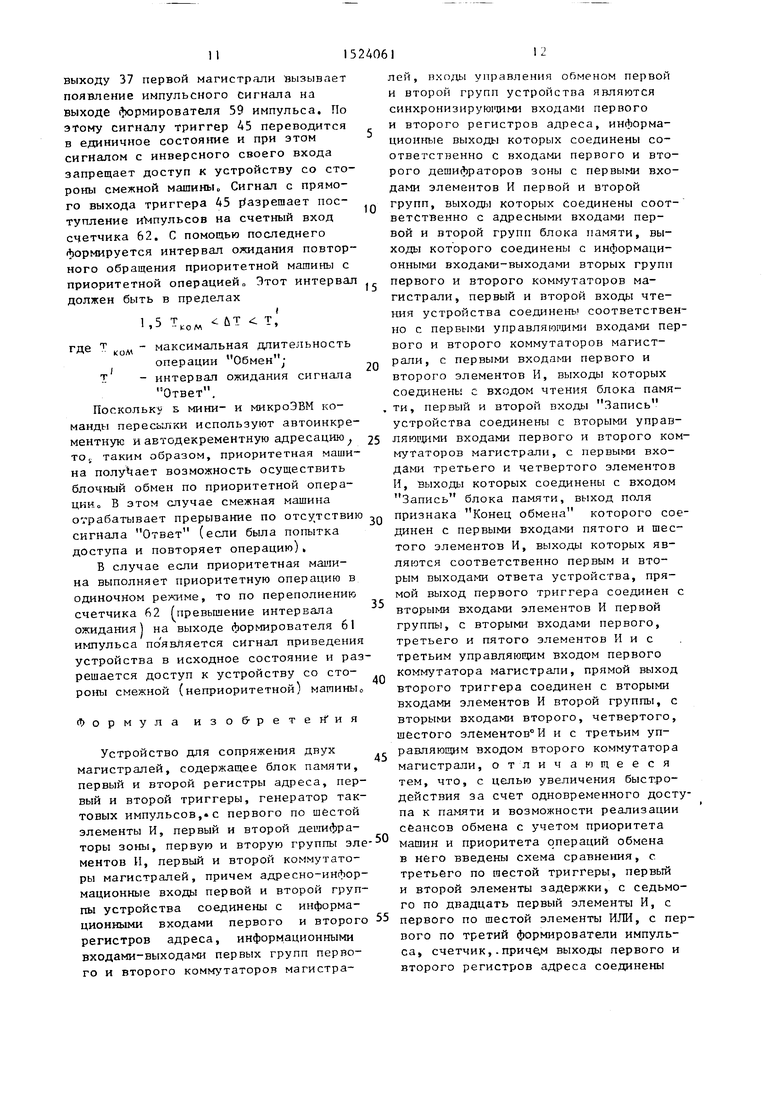

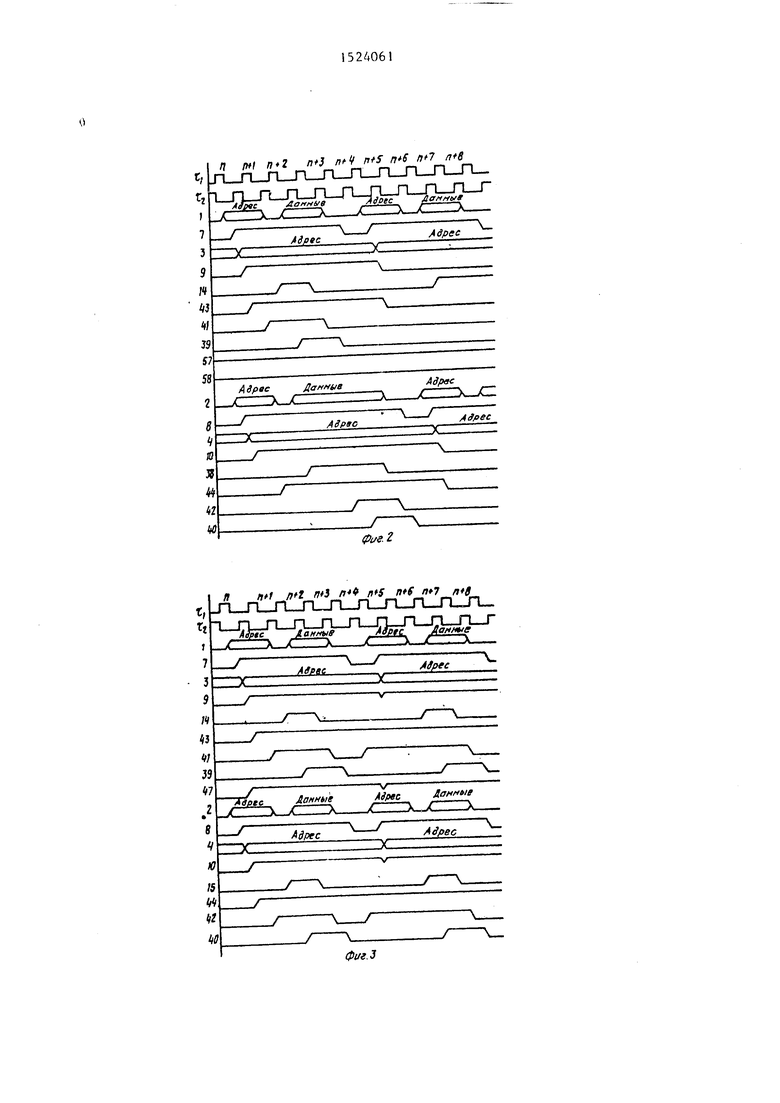

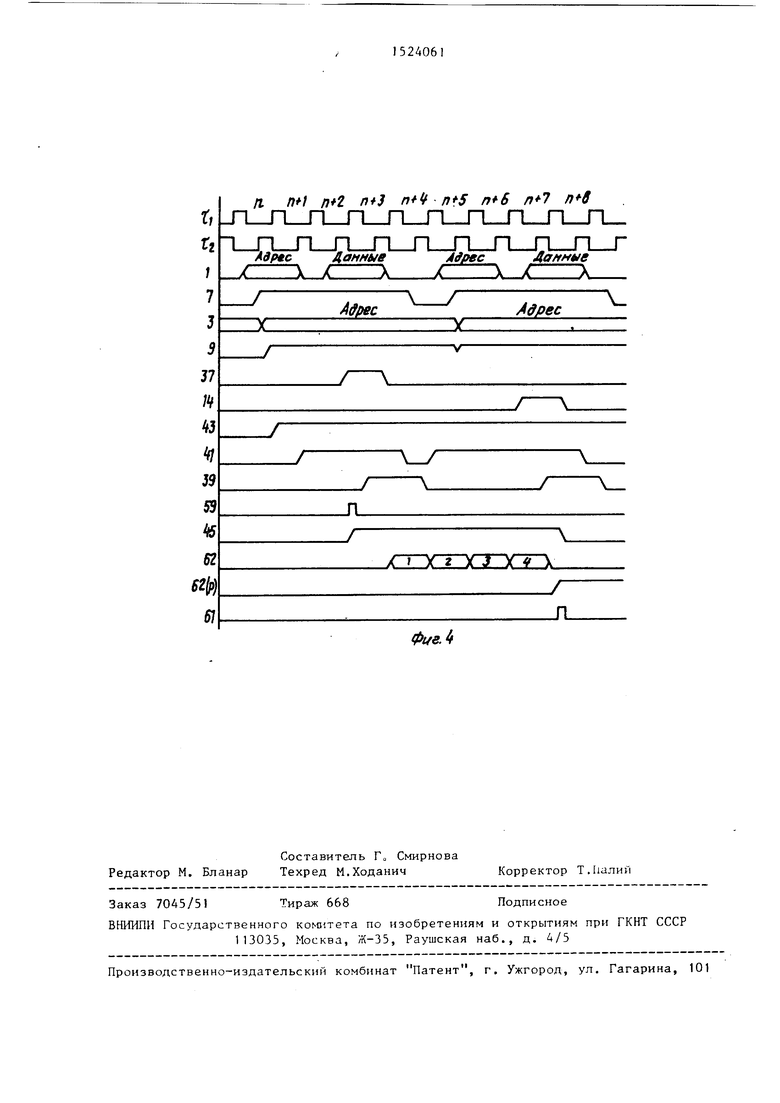

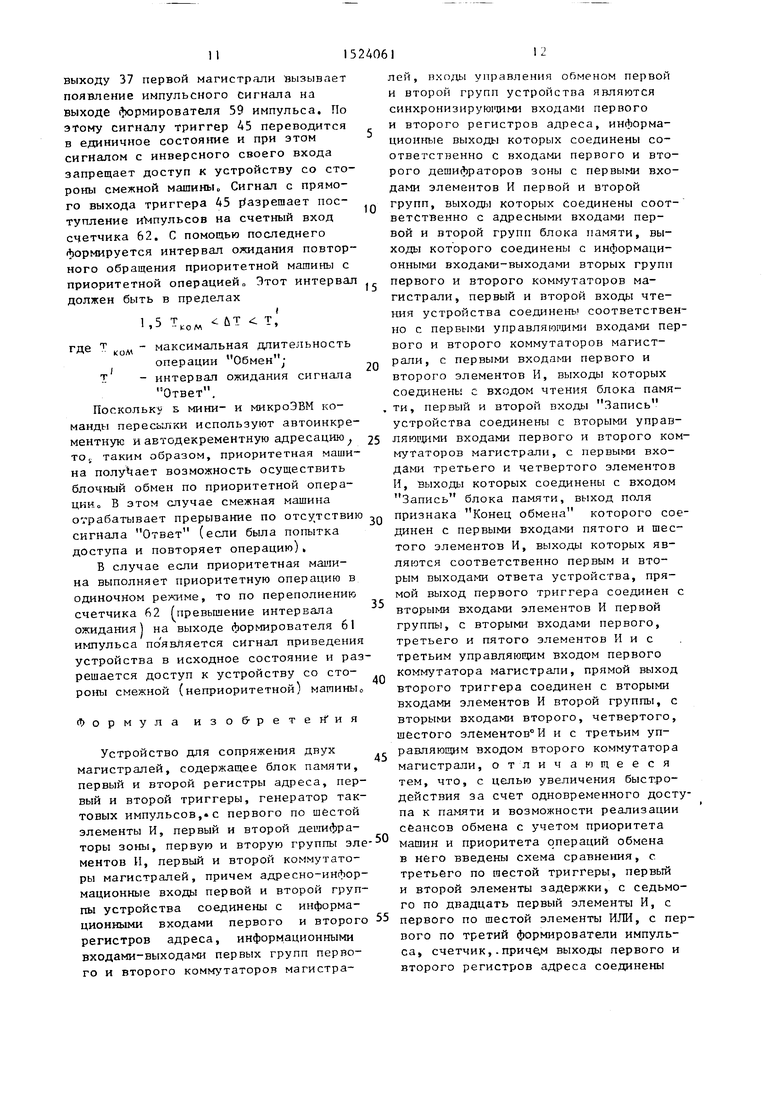

На фиго приведена структурная схема устройства; на фиго2 - временная диаграмма работы устройства для случая, когда на п-ом такте два процессора обращаются к устройству; на фиг.З - временная диаграмма работы устройства в дублированной системе, когда два процессора читают из блока- на фиг.4 - временная диаграмма, опи

группами информационных входов-выходов первого 5 и второго 6 коммутаторов магистралей Выходы 14 и 15 чтения первой и второй магистралей соединены с первыми входами первого 16 и второго 17 элементов И, а также с первыми входами направления обмена первого 5 и второго 6 коммутаторов магистралей

Выходы первого 16 и второго 17 элементов И соединены с входом чтения блока 13 памяти Выходы 37 и 38 записи первой и второй магистралей соединены с первыми входами третьего 18 и четвертого 19 элементов И, а также с вторыми входами направления обмена первого 5 и второго 6 коммутаторов магистралей Выходы третьего 18 и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Микропроцессор | 1980 |

|

SU955077A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1522224A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - увеличение быстродействия за счет одновременно доступа к памяти и возможности реализации обмена с учетом приоритета машин и приоритета операций обмена. Поставленная цель достигается тем, что устройство содержит адресно-информационные выходы 1 и 2 магистралей, регистры 3 и 4 адреса, коммутаторы 5 и 6 магистралей, выходы 7 и 8 управления обменом магистралей, дешифраторы 9 и 10 зоны, группы 11 и 12 элементов И, блок 13 памяти выходы 14 и 15 чтения магистралей, элементы И 16-36, выходы 37 и 38 записи магистралей, входы 39 и 40 ответа магистралей, триггеры 41-46, схему 47 сравнения, элементы 48 и 49 задержки, элементы ИЛИ 50-55, генератор 56 тактовых импульсов, вход 57 приоритета машины, вход 58 приоритета операции, формирователи импульса 59-61, счетчик 62. 4 ил.

сывающая одиночный доступ к устройст- 20 четвертого 19 элементов И соединены ву приоритетной машиной по приоритет- с входом записи блока 13 памяти.

ной операции

Устройство содержит адресно-информационные выходы 1 и 2 магистралей, регистры 3 и 4 адреса, коммутаторы 5 и 6 магистралей, выходы 7 и 8 управления обменом магистралей, дешифраторы 9 и 10 зоны,группы И 11 и 12 эле1Iсоединен с вторыми входами элемен тов И первой группы 11, первого 16,

ментов, блок 13 памяти, выходы 14 и 15 чтения магистралей, элементыЛ 16- о третьего 18 и пятого 20 элементов 36, выходы 37 и 38 записи магистра- И, а также с разрешающим входом первого коммутатора 5 магистралей Прямой выход второго триггера 42 соедилей, входы 39 и 40 ответа магистралей, триггеры 41-46, схему 47 сравнения, элементы 48 и 49 задержки, элементы ИЛИ 50-55, генератор 56 такто- 5 второй группы 12, второго 17, чет- вых импульсов, сигнальный вход 57 при- вертого 19 и шестого 21 элементов И, оритета машины, сигнальный вход 58 приоритета операции, формирователи 59-61 импульса, счетчик 62.

Адресно-информационные входы 1 и 4Q

2первой и второй магистралей соединены с информационными входами первого

3и второго 4 регистроЬ адреса, а также с первыми группами информационных входов-выходов первого 5 и второ- д вого 9 и второго 10 дешифраторов зо- го 6 коммутаторов магистралей, Синх- ны соединены с первыми входами девя- ровходы первого 3 и второго 4 регистров адреса соединены с выходами управ

ления обменом первой 7 и второй 8 магистралей-. Информационные выходы пер- и второй 49 элементы задержки с ну- Вого 3 и второго 4 регистров адреса левыми входами первого 41 и второго соединены с входами первого 9 и второго 10 дешифраторов зоны,а также с первыми входами элементов И первой 1 1 и второй 12 групп. Выходы элементов И первой 11 и второй 12 групп соединены с группой адресных входов блока 13 памяти, группа информационных входов- выходов которого соединена с вторыми

55

нен с вторыми входами элементов И

а также с разрешающим входом второго коммутатора 6 магистралей.

Информационные выходы первого 3 и второго 4 регистров адреса соедине ны с первым и вторым входами схемы 47 Сравнения, выход которой соеди нен с первыми входами седьмого 22 и восьмого 23 элементов Ио Выходы пертого 24 и десятого 25 элементов Иь Выходы пятого 20 и шестого 21 элементов И соединены через первый 48

42 триггеров. Выход девятого 24 и десятого 25 элемен тов И соединены с информационными входами третьего 43 и четвертого 44 триггеров, прямые выходы которых соединены соответствен но с первыми входами одиннадцатого 26 и двенадцатого 27, тринадцатого 28 и четырнадцатого 29, а также пятСинхронизирующий выход блока 13 памяти соединен с первыми входами пятого 20 и шестого 21 элементов И, выхо- ды которых соединены с входами 39 и

40ответа первой и второй магистралей. Прямой выход первого триггера

1Iсоединен с вторыми входами элементов И первой группы 11, первого 16,

третьего 18 и пятого 20 элементов И, а также с разрешающим входом первого коммутатора 5 магистралей Прямой выход второго триггера 42 соедивторой группы 12, второго 17, чет- вертого 19 и шестого 21 элементов

нен с вторыми входами элементов И

второй группы 12, второго 17, чет- вертого 19 и шестого 21 элементов И,

вого 9 и второго 10 дешифраторов зо- ны соединены с первыми входами девя-

а также с разрешающим входом второго коммутатора 6 магистралей.

Информационные выходы первого 3 и второго 4 регистров адреса соединены с первым и вторым входами схемы 47 Сравнения, выход которой соединен с первыми входами седьмого 22 и восьмого 23 элементов Ио Выходы первого 9 и второго 10 дешифраторов зо- ны соединены с первыми входами девя-

и второй 49 элементы задержки с ну- левыми входами первого 41 и второго

того 24 и десятого 25 элементов Иь Выходы пятого 20 и шестого 21 элементов И соединены через первый 48

и второй 49 элементы задержки с ну- левыми входами первого 41 и второго 5

42 триггеров. Выход девятого 24 и десятого 25 элемен тов И соединены с информационными входами третьего 43 и четвертого 44 триггеров, прямые выходы которых соединены соответственно с первыми входами одиннадцатого 26 и двенадцатого 27, тринадцатого 28 и четырнадцатого 29, а также пятнадцатого 30 и шестнадцатого 31 элементов И, Выходы седьмого 22 и восьмого 23 элементов И соединены с первыми входами первого 50 и второго 51 элементов ИЛИ, выходы которых соединены с информационными входами первого 41 и второго 42 триггеров.

Выходь 14 и 15 чтения первой и второй йагистралей соединены с вто- рыми входами седьмого 22 и восьмого 23 элементов И, а также с первыми входами семнадцатого 32 и восемнадцатого 33 элементов И. Выходы 37 и 38 записи первой и второй магистра- лей соединены с первыми входами девятнадцатого 34 и двадцатого 35 элементов И. Прямой выход первого триггра 41 соединен с вторыми входами семнадцатого 32 и девятнадцатого 34 элементов И, выходы которых соединены с первым и вторым входами третьего элемента ИЛИ 52. Прямой выход второго триггера 42 соединен с вторыми входами восемнадцатого 33 и двадца- того 35 элементов И, выходы которых соединены с первым и вторым входами четвертого элемента ИЛИ 53. Инверсные выходы первого 41 и второго 42 триггеров соединены соответственно с вторыми входами двенадцатого 27 и одиннадцатого 26 элементов Ио Выход L генератора импульсов соединен с синхровходами третьего 43 и четвертого 44 триггеров, а также с первым входом двадцать первого элемента И 36 Выход генератора импульсов соединен с третьими входами одиннадцатого 36 и двенадцатого 27 элементов И, выходы которых соединены с синхровхода- ми первого 41 и второго 42 триггеров. Выходы тринадцатого 28 и четырнадцатого 29 элементов И соединены с вторыми входами первого 50 и второго 51 элементов ИЛИ. Выходы пятнадцато- го 30 и шестнадцатого 31 элементов И соединены с третьими входами первого 50 и второго 51 элементов ИЛИ, а также с инверсными входами четырнадцатого 29 и тринадцатого 28 элементов И соответственно.

Первый сигнальный выход 57 устройства приоритета машины соединен с вторым входом пятнадцатого элемента И 30, с третьими входами семнадцато- го 32 и девятнадцатого 35 элементов И а также с инверсными входами шестнадцатого 31, восемнадцатого 33 и двадцатого 35 элементов И. Второй сигнапь

Q 5 0 5 о Q Q

5

ный вход 58 устройства приоритета операции соединен с четвертыми входами девятнадцатого 34 и двадцатого 35 элементов И, а также с инверсными входами семнадцатого 32 и восемнадцатого 33 элементов И, Выход третьего элемента ИЛИ 52 соединен с входом первого формирователя 59 импульса, вь1ход которого соединен с единичным входом пятого триггера 45 и первым входом пятого элемента ИЛИ ЗА. Выход четвертого элемента ИЛИ 53 соединен с входом второго формирователя 60 импульса, выход которого соединен с единичным входом шестого триггера 46 и вторым входом пятого элемента ИЛИ 54 Выход пятого элемента ИЛИ 54 соединен с входом сброса счетчика 62, сигнальный выход переноса которого соединен с входом третьего формирователя 61 импульса. Выход последнего соединен с нулевыми входами пятого 45 и шестого 46 триггеров, прямые выходы которых соединены с первым и вторым входами шестого элемента ИЛИ 55,

Инверсные выходы пятого 45 и шестого 46 триггеров соединены соответственно с вторыми входами десятого 25 и девятого 24 элементов И, Выход шестого элемента ИЛИ 55 соединен с вторым входом двадцать первого элемента И 36, выход которого соединен со счетным входом счетчика 62,

Адресно-информационные выходы I н 2 первой и второй магистралей служат для подачи на устройство данных и адресов ячеек блока 13 памяти.

Регистры 3 и 4 адреса первой и второй магистралей служат для временного хранения адреса ячейки блока 13 памяти, к которой производится обращение,, Коммутаторы 5 и 6 магистралей служат для управления прохождением информации в операциях записи-чтения. Выходы 7 и 8 управления обменом первой и второй магистралей служат для подачи на устройство сигналов, стро- бирующих занесение адресов в регистры 3 и 4 адреса,

Цешифраторы 9 и 10 зоны служат для опознания принадлежности текущего адреса магистрали пространству адресов устройства Группы элементов 11 и 12 служат для управления прохождения информации на адресный вход блока 13 памяти Последний служит дпя буферного хранения передаваемой информации.

Выходы 14 и 15 чтения первой и второй магистралей служат для подачи на устройство сигналов, иницирующих операцию чтения из блока 13 памяти

Элементы И 16 и 17 служат для запрещения прохождения сигналов чтения на блок 13 памяти, если текущий адрес магистрали не попал в пространство адресов устройства. Элементы И 18 и 19 служат для запрещения прохождения сигналов записи на блок 13 памяти, если текущий адрес магистрали не попал в пространство адресов устройства, а элементы И 20 и 21 - для запрещения выдачи ответного сигнала, если не бьшо обращения к устройству о Элементы И 22 и 23 позволяют формировать единичные сигналы в случае, если обе машины выполняют операцию чтения с одинаковым адресом ячейки блока памяти, элементы И 24 и 25 позволяют управлять с помощью сигналов с инверсных выходов триггеров 42 и 41

сигналов опознания адресов, принадле- 25 раций чтения по одному адресу, либо

жащих адресному пространству устройства.

Элементы И 26 и 27 позволяют запрещать прохождение синхроимпульсов о на синхровходы триггеров 41 {i 42 в случае, если нет обращения к устройству от данной машины или смежная машина выполняет операцию обмена с устройством. Элементы И 28 и 29 позволяют формировать единичные сигналы в случае, если есть обращение к устройству от данной машины и нет обращения от смежной машины, элементы И 30 и 31 - единичные сигналы в случае, если есть обращение к устройству со стороны данной машины и ей отведен приоритет Элементы И 32 и 33 позволяют формировать единичные сигналы в случае, если есть обращение по чтению от данной машины и ей отведен .приоритет, а также отведен приоритет операции Чтение. Эле,менты И 34 и 35 позволяют формировать единичные сигналы в случае, если есть обращение по записи от данной машины и ей отведен приоритет, а также отведен прио- - ритет операции Запись. Элемент И 36 позволяет запрещать прохождение синхроимпульсов С, на счетный вход счетчика, если приоритетная машина не выполняет приоритетную операцию

Выходы 37 и 38 записи первой и второй магистрали служат для подачи на устройство сигналов, инициирующих

15240618

операцию Запись. Входь 39 и 40 отве

5

0

та первой и второй магистралей служат для выдачи сигналов завершения операции обмена

Триггеры 41 и 42 позволяют фиксировать по oj состояния взаимодействия устройства с соответствующей машинойо Триггеры 43 и 44 позволяют фиксиро-. вать по б , наличие обращения к ству со стороны соответствующей машины, а триггеры 45 и 46 - факт выполнения соответствующей приоритетной машиной приоритетной операции.

Схема 47 сравнения позволяет обнаруживать одновременное обращение двух машин к одной ячейке блока 13 памяти.

Элементы 48 и 49 задержки позволяют формировать сигналы приведения устройства в исходное состояние после завершения операции обмена.

Элементы ИЛИ 50 и 5I позволяют формировать единичные сигналы либо в случае требования двумя машинами one0

5

0

в случае требования приоритетной машиной необходимой операции Элементы ИЛИ 52 и 53 позволяют формировать единичные сигналы в случае, если соответствующая приоритетная машина обращается к устройству с приоритетной операцией. Элемент ИЛИ 54 позволяет формировать сигнал сброса счетчика 62 в случае, если соответствующая приоритетная машина обращается к устройству с приоритетной операцией Элемент 11ПИ 55 позволяет формировать единичный сигнал в случае, если соответствующая приоритетная машина осуществляет по приоритетной операции Блочный обмен.

Генератор тактовых импульсов служит для формирования серий импульсов, стробирующих работу устройства.

Сигнальный вход 57 устройства приоритета машины служит для подачи на устройство сигнала отводящего приоритета соответствующей машине. Сигнальный вход 58 устройства приоритета операции служит дпя подачи на устройство сигнала отводящего приоритета соответствующей операции обмена.

Формирователи 59 и 60 импульса позволяют формировать сигналы сброса счетчика 62 в случае, если приоритет- ная машина повторно обращается к

устройству с приоритетной операцией Формирователь 61 импульса позволяет формировать сигнал приведения устрой5

0

у

ства в исходное состояние по сигналу превышения интервала ожидания повторного обращения к устройству приоритетной ма1ииной с приоритетной Операцией „

Счетчик 62 позволяет формировать временной интервал ожидания повторного обращения приоритетной машиной

а

С приоритетной операцией

Устройство работает следуюгхим образом.

Начальное состояние устройства характеризуется тем, что триггеры 41-46 находятся в нулевом состоянии, счетчик 62 и блок 13 памяти имеют нулевое содержимое (цепи приведения устройства в начальное состояние не показаны).

Во время функционирования обоих внешних устройств процессоров в регистры 3 и 4 заносятся коды адресов по фронтам импульсов Обмен по выходам 7 и 8 с каждым появлением в магистралях адресных кодов При появле НИИ адреса, совпадающего с зоной адресов блока 13 памяти, например, в регистре 3, дешифратор 9 выдает сигнал, который удерживается до тех пор пока не изменится содержимое регистр Зо Срабатывание триггера 43 происходит по отрицательному фронту синхроимпульса Т, , поступающего с выхода генератора 56 тактовых импульсов Единичный сигнал на прямом выходе триггера 43 разрешает работу схемы приоритета, реализованной на элементах И 13 и 16 и 1ШИ 50 и 51, а также разрешает прохождение синхроимпульсо t , на синхровход триггера 41 о Сдвиг

/

сигналов с, и с-2 выбирается достаточным для завершения переходных процессов в схеме приоритета. Приоритет магистралей задается уровнем сигнала на входе 57 устройства, причем едининому уровню соответствует приоритет верхней магистрали (фигс,).

При использовании устройства в дублированных системах, работающих с общими данными, в устройстве включается в работу схема опознания одновременного доступа к ячейке блока 13 памяти, которая реализована на схеме 47 сравнения и элементах И 22 и 23 Схема опознания вместе со схемой приоритета формирует единичные сигналы на информационные входы триггеров 41 и 42, разрешающие одновременное чтение процессорами содержимого ячейки

10

24061It)

блока 13 памяти. При этом согласованная работа процессоров может быть достигнута с помощью привязки к сигналам генератора 56о

В момент срабатывания триггера 41 открывается коммутатор 5, При этом направление передачи коммутатора 5 определяется наличием одного из внешних сигналов Чтение или Запись, Эти внешние импульсы управляют режимом работы блока 13, Тое в двунаправленной магистрали либо появляется слово для записи в блок 13, либо слово

j читается из блока 13 и поступает на магистраль.

Адрес в блок 13 поступает через элемент 11 (12) из-регистра 3 (4), Например, при включении триггера 41 адрес в блок 13 поступает через элементы И 11, а управляющие сигналы, определяющие режим работы блока 13 (Чтение или Запись), через элемент И 16 или 18о Элемент И 20 управ25 ляет поступлением на вход 39 первой магистрали сигнала синхронизации из памяти (Ответ), который несет информацию об окончании обращения к памяти. Во вторую магистраль, обращение

2Q которой блокировано схемой приоритета, сигнал Ответ не поступает и обмен с памятью задерживается до окончания обращения к устройству первой магистрали Задержанным на элементе 48 задержки (для надежной фиксации данных) сигналом Ответ триггер 41 возвращается в исходное состояние

В зависимости от сочетания сигналов приоритета мшяины (процессора) и операции обмена в работу вкппчает20

0

ся схема приоритета операции, которая реализована на элементах И 24, 25, 32-36, ИЛИ 52-55, формирователях 59-61 импульса и счетчике 62.

Схема приоритета операции работает следую1 шм образом.

Уровень сигнала на сигнальном входе 58 устройства задает приоритет операции Запись или Чтение для

приоритетной машины. Если вновь поступающие данные имеют большую ценность, то приоритет отводится операции Запись, и наоборот .диничный уровень сигнала на входе 58 соответствует

выбору операции Запись, как более приоритетной При взведенном триггере 41 и единичньгх сигналах на входах 57 и 58 приход сигнала Запись по

выходу 37 первой магистрали вызывает появление импульсного сигнала на выходе формирователя 59 импульса. По этому сигналу триггер А5 переводится в единичное состояние и при этом сигналом с инверсного своего входа запрещает доступ к устройству со стороны смежной машины Сигнал с прямого выхода триггера 45 {Разрешает поступление и мпульсов на счетный вход счетчика 62. С помощью последнего формируется интервал ожидания повторного обращения приоритетной машины с приоритетной операцией Этот интервал

должен быть в пределах

( 1ST ЛТ т

- U - -,

где Т ,цд, - максимальная длительность

операции Обмен ; Т - интервал ожидания сигнала

Ответ.

Поскольку S мини- и микроэвм команды пересылки используют автоинкрементную и автодекрементную адресацию TOj таким образом, приоритетная машина возможность осуществить блочный обмен по приоритетной операции В этом случае смежная машина О7рабатывает прерывание по отсутстви сигнала Ответ (если была попытка доступа и повторяет операцию),

В случае если приоритетная магчи- на выполняет приоритетную операцию в одиночном режиме, то по переполнению счетчика 62 (превьшение интервала ожидания) на выходе формирователя 61 и myльca появляется сигнал приведени устройства в исходное состояние и рарешается доступ к устройству со сто

роны смежной (неприоритетной) матины

Формула

и 3

об-ретен ия

,

Устройство для сопряжения двух магистралей, содержащее блок памяти, первый и второй регистры адреса, первый и второй триггеры, генератор тактовых импульсов,«с первого по шестой элементы И, первый и второй дешифраторы зоны, первую и вторую группы эле ментов И, первый и второй коммутаторы магистралей, причем адресно-информационные входы первой и второй группы устройства соединены с информационными входами первого и второго регистров адреса, информационными входами-выходами первых групп первого и второго коммутаторов магистра10

15

20

25 Q

35

40

45

50

55

лей, иходы управления обменом первой и второй групп устройства являются синхронизирующими входами первого и второго регистров адреса, информационные выходы которых соединены соответственно с входами первого и второго дешифраторов зоны с первыми входами элементов И первой и второй групп, ВЫХОД, которых соединены соответственно с адресными входами первой и второй групп блока памяти, выходы которого соединены с информационными входами-выходами вторых групп первого и второго коммутаторов магистрали, первый и второй входы чтения устройства соединень соответственно с первыми управляюпд1ми входами первого и второго коммутаторов магистрали, с первыми входами первого и второго элементов И, выходы которых соединены с входом чтения блока памяти, первый и второй входы Запись устройства соединены с вторыми управ- ляюищми входами первого и второго коммутаторов магистрали, с первыми входами третьего и четвертого элементов И, Выходы которых соединены с входом Запись блока памяти, выход поля признака Конец обмена которого соединен с первыми входами пятого и шестого элементов И, выходы которых являются соответственно первым и вторым выходами ответа устройства, прямой выход первого триггера соединен с вторыми входами элементов И первой группы, с вторыми входами первого, третьего и пятого элементов И и с третьим управляющим входом первого коммутатора магистрали, прямой выход второго триггера соединен с вторыми входами элементов И второй группы, с вторыми входами второго, четвертого, шестого элементов И и с третьим управляющим входом второго коммутатора магистрали, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия за счет одновременного доступа к памяти и возможности реализации сеансов обмена с учетом приоритета машин и приоритета операций обмена в него введены схема сравнения, с третьего по шестой триггеры, первый и второй элементы задержки, с седьмого по двадцать первый элементы И, с первого по шестой элементы ИЛИ, с первого по третий формирователи импульса, счетчик,. приче м выходы первого и второго регистров адреса соединены

соответственно с входами первой и втрой групп схемы сравнения, выход которой соединен с первыми входами седмого и восьмого элементов И, ВЫХОДЬ

которых соединены соответственно с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с информационными входами первого и второго триггеров, выходы первого и второго дешифраторов зоны соединены соответственно с первыми входами девятого и десятого элементов И, выходы которых соединены соответственно с информационными входами третьего и четвертого триггеров, входы синхронизации которых соединены с первым выходом тактового генератора, второй выход которого соединен с первыми входами одиннадцатого и двенадцатого элементов И, выход третьего триггера соединен с вторым входом одиннадцатого элемента И, с первыми входами тринадцатого и четырнадцатого элементов И, выходы которых соединены соответственно с вторым и третьим входами первого элемента ИЛИ, выход четвертого триггера соединен с вторым входом двенадцатого элемента И, с первыми входами пятнадцатого и шестнадцатого элементов И, выходы которых соединены соответственно с вторым и третьим входами второго элемента ИЛИ, второй вход тринадцатого элемента И соединен с выходом пятнадцатого элемента И, второй вход шестнадцатого элемента И соединен с выходом четыр Надца- того элемента,И, второй вход четырнадцатого элемента И соединен с вторым входом пятнадцатого элемента И, соединен с первыми входами семнадцатого, восемнадцатого, девятнадцатого, двадцатого элементов И и с входом Приоритет машины, третий вход одиннадцатого элемента И соединен с инверсным выходом второго триггера, прямой выход которого соединен с вторыми входами девятнадцатого, двадцатого элементов И, третий вход двенадцатого элемента И соединен с инверсным выходом первого триггера, прямой выход которого соединен с вторыми входами семнадцатого и восемнадцатого элементов И, выход одиннадца- того элемента И соединен со входом синхронизации первого триггера, вход сброса которого соединен с выходом первого элемента задержки, вход кото0

5

0

5

0

5

0

5

0

5

рого соединен с выходом.пятого элемента И, выход двенадцатого элемента И соединен с синхронизирующим входом второго триггера, вход сброса которого соединен с выходом второго элемента задержки, вход которого соединен с выходом шестого элемента И, первый вход чтения устройства соединен с вторым входом седьмого элемента И, с третьим входом восемнадцатого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход чтения устройстча соединен с вторым входом восьмого элемента И и с третьим входом девятнадцатого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, первый вход записи устройства соединен с третьим входом семнадцатого элемента И, второй вход записи устройства соединен с третьим входом двадцатого элемента И, выход Приоритет операции устройства соединен с четвертыми входами семнадцатого, восемнадцатого, девятнадцатого и двадцатого элементов И, выход семнадцатого элемента И соединен с вто- рым входом третьего элемента ШШ, выход которого соединен с входом первого формирователя импульса, выход которого соединен с первым входом пятого элемента ИЖ, с информационным входом пятого триггера, инверсный выход которого соединен с вторым входом десятого элемента И, выход двадцатого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом второго формирователя импульса, выход которого соединен с вторым входо пятого элемента ИЛИ и с информационным входом шестого триггера, инверсный выход которого соединен с вторым вхо;с;ом девятого элемента И, выход пятого элемента ИЛИ соединен с входом сброса счетчика, выход которого соединен с входом третьего формирователя импульса,выход которого соединен с входами сброса пятого ншестого триггеров, прямые выходы которых соединены соответственно с первым и и вторым входами шестого элемента ИЛИ, выход которого соединен с первым входом двадцать первого элемента И, выход которого соединен со счетньпч входом счетчика, второй вход двадцать первого элемента И соединен с синхронизирующим входом четвертого триггера.

П mt nf f jt7

Aiflfc

AврвеДанмив

Аврв

Л / пП тЗ /т

tfp.

Адрес

Адрес

АанныеАдресЛан не

Адрес

Адрес

Адрас

Аврво

АЗрес

Адрес

Адрес

Г,

Гг

;

7

3

3

J7

Jtf

«3

«/ J9 5Э и 6Zlp)

6

П /7#2 n /7

Affj)ec

Адрес

У

П

П

Адрес

У

П

ф1/гЛ

| Двухпортовое устройство сопряжения в вычислительной системе | 1982 |

|

SU1156080A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-02—Подача