Изобретение относится к вычисли- тельной и цифровой измерительной технике и может быть использовано для преобразования аналоговых велн чин в цифровые,

Цель - повышение быстродействия аналого-цифрового преобразования,

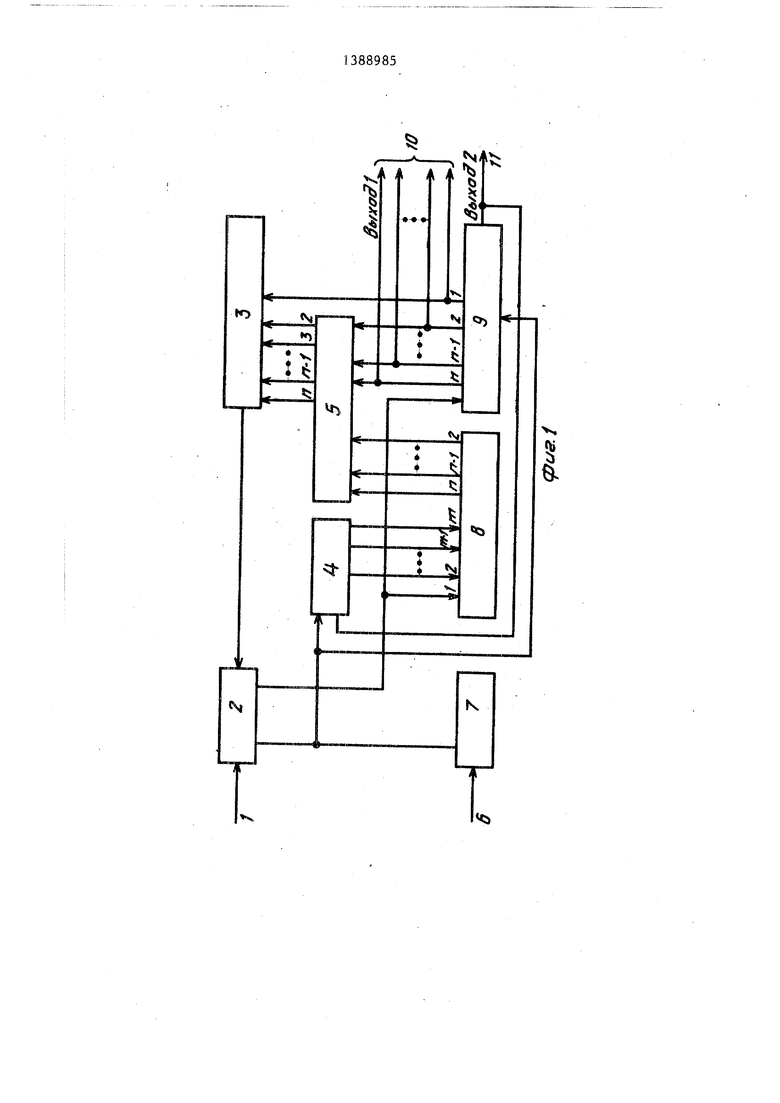

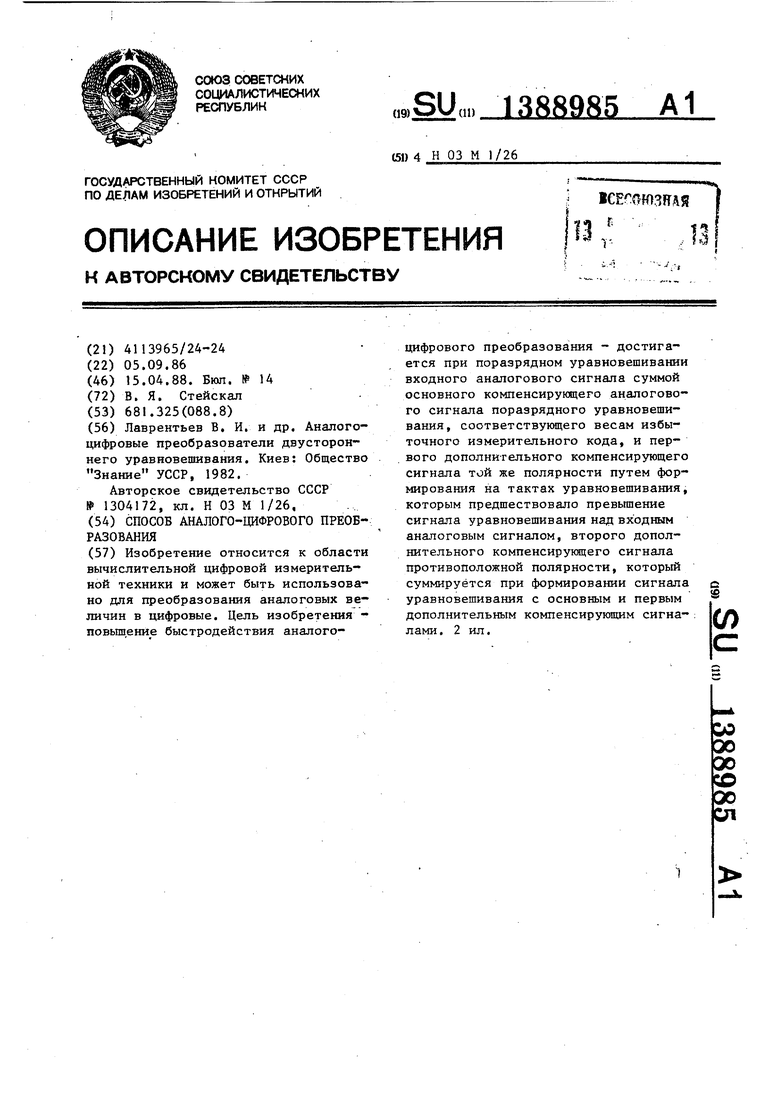

На фиг, 1 приведена функциональ нал схема устройства, которое может быть использовано для реализации способа аналого-цифрового преобразования; на Фиг, 2 - временная диаграмма компенсирующего сигнала.

Аналого-цифровой преобразователь (фиг, 1), реализующий данный способ содержит аналоговый вход 1, строби- руемый блок 2 сравнения, цифро-аналоговый преобразователь 3 (ЦАП 3), счетчик 4 адреса, блок 5 логических элементов ИЛИ, управляющий вход 6 Запуск, генератор 7 импульсов, блок 8 постоянной памяти, регистр 9 последовательного приближения, группу выходов 10, являющихся первым вы : ходом устройства, и выход 11, являющийся вторым выходом устройства,

Изобретение основано на использовании при кодировании входной аналоговой величины избыточных измерительных кодов,

: Известно, что под динамической I погрешностью А1Щ поразрядного коди- Iрования при изменяющихся во времени параметрах входного А„(t:) и комВХ

пенсирующего A|(t;) сигналов понимается разность До. между ними в момент времени t, соответствующей концу кодирования без учета статичекой погрешности и погрешности дискретизации, т,е.

йа А ft,,, ) Вх 1+

4,(S,J.

Известно также, что необходимым условием возникновения динамической погрешности второго рода Д является изменение А (t;)

вх

за время кодирования Т более чем на величину, например, младшего разряда q. Необходимым условием возникновения динамической погрешности первого рода д,Q , обусловленной инерционностью узлов АЦП, является уменьшение длительности такта кодирования t меньше предельного значения равного

t . Inl/S,

где с - постоянная времени эквивалентной схемы цепи сравнения

mirf

S - максимальное значение погрешности установления A(t) за время t.,

Допустим, 0, т,е, Agjj(t;) «Ag const. Тогда достаточным условием возникновения Л(о будет изменение к моменту определения состояния некоторого, допустим 1-го разряда сигнала А (tj) настолько, что нарушится неравенство

п А (tj)-q А, A,(t.) + Ц Q:,

;-е+ (1)

выполнение которого на каждом такте кодирования при использовании способа поразрядного кодирования гарантирует уравновешивание А

вх

сигналом

AK(tn+,) с погрешностью не более q, При этом в двоичном АЦП, для разрядов

которого характерно соотношение

п Qp У Q, появление на любом такте

ошибок кодирования типов неправиль- ное включение разряда (в дальнейшем включение) или неправильное выключение разряда (в дальнейшем выключение) неминуемо приводит к нарушению неравенства (1 и появлению

0

5

0

5

0

1 о.

в АЦП на основе избыточных из- ме15ительных кодов (ИИК), для разрядов которого характерно соотношение

п Qp ZLQ; появление ошибок кодиро.ve+i

вания типа включение (не следующих непосредственно друг за другом) не приводит к нарушению неравенства (1) вследствие автокомпенсации этой ошибки последующими разрядами. Поэтому для осуществления правильного аналого-цифрового .преобразования при наличии погрешностей установления A(t;), т,е, при t tj. , необходимо исключить появление ошибок кодирования типа включение, В известном способе это реализуется воздействием на процесс уравновешивания дополнительным аналоговым сигналом Aa(tg), формируемым от момента включения и до момента определения состояния 1-го разряда. При этом относительное значение Aa(tg) к весу 1-го разряда постоянно на любом такте и равно для случая сб 1,618:

55

Aj(tj) ei-V2,

t)

где ot - основание кода золотой пропорции.

.31

Независимость S AoCt , ) от характера процесса формирования A(t;), т.е. от результатов сравнения входного и компенсирующего аналоговых сигналов, не позволяет максимально использовать избыточность, заложенную в АЦП, для повышения быстродействия. Так быстродействие известного способа аналого-цифрового (А-Ц) преобразо- вания зависит от предельного значения погрешности установления компенсирующего сигнала на каждом такте, которое определяется отсутствием оши

15

20

25

бок кодирования типа включение и следующих непосредственно друг за- другом ошибок кодирования типа выключение (в дальнейшем соседних ошибок кодирования). Отметим, что возникновение на любом такте первой из названных ошибок возможно только при условии увеличения компенсирующего сигнала на этом такте по сравнению со значением этого сигнала на предыдущем такте, т.е. при AK(tj) A(tj.,), что эквивалентно факту невыключения (1-1)-го разряда. Возникновение на любом 1-м такте ошибок кодирования типа включение (в том числе и соседних) возможно только при условии уменьшения компенсирующего сигнала на этом такте по сравнению со значением этого сигнала на предьщущем такте, т.е.

при AK(te) Aj(te,), что эквивалент- .. , , но факту выключения (l-l)-ro разрй- 35 Q,5 + (A(t3,)+Q,j)55 +(А(ц) + да. В общем случае вероятность воз- никновения ошибки кодирования типа

30

A|,(te.,), позволит увеличить знач ние 8 и, следовательно, быстродей ствие А-Ц преобразования. Докажем это путем рассмотрения процесса ф мирования компенсирующего сигнала Пусть на первом такте кодирования присутствует такой Aa.(t, ),. что пр длительности такта кодирования, р ной минимально возможной, произой полная компенсация недоустановлен компенсирующего сигнала, т.е.

A,(t,) (A(t,)+Q,)S Q,, (

Q

где S 1-S.

Учитывая, что значение компенсиру щего сигнала, на любом 1-м такте равно:

е-| A(tg) A,(tj.,)8-«- Ц

+A(te) + Qe)5,,,

где a;e о, l - цифра результата у

новешивания,

а также принимая а/ О (,2,., получим:

A,(t)A,(t, )S +(A,(t2)-bQ,)iy Q,S + (A (tj).+Q,)5 ;

Q

l,(t,)A,(t2)i + (A5(t,)+Q,)

+Qi)S ;

A(te)A,(te.,)5+(Ac,(tg)+Qg)5 q, +(A.(t,)+Q,V&t«- +... ... + (A.(te.,)+Qe..)S S +(A (tg) +

включение можно уменьшить, увеличив An(tg). При этом компенсирующий сигнал, состоящий из суммы дополнительного и основного компенсирукице- го (избыточного набора эталонных сигналов) аналоговых сигналов, увеличится, что уменьшит абсолютную погрешность его установления. Однако в этом случае увеличится и вероятность появления соседних ошибок кодирования типа выключение. Данное обстоятельство не позволяет увеличивать S Ал (t g) вьш1е значения, определяемого из (2), и ограничивает быстродействие А-Ц преобразования на уровне, задаваемом значением S , равном в этом случае о oi т.е. 23,6%,

Учитывая изложенное, можно пред- положить, что изменение алгоритма формирования дополнительного сигнала, а именно уменьшение Aa(tf) до

о

Q

значения Aa(tf)- на тех тактах/ для которых A(te) A(tj., ), и увеличение AnCtf) до значения Aa(tg) на тех тактах, для которых A(tp);

5

0

5

.. , , 5 Q,5 + (A(t3,)+Q,j)55 +(А(ц) +

0

A|,(te.,), позволит увеличить значение 8 и, следовательно, быстродействие А-Ц преобразования. Докажем это путем рассмотрения процесса формирования компенсирующего сигнала. Пусть на первом такте кодирования присутствует такой Aa.(t, ),. что при длительности такта кодирования, равной минимально возможной, произойдет полная компенсация недоустановления компенсирующего сигнала, т.е.

A,(t,) (A(t,)+Q,)S Q,, (3)

Q

где S 1-S.

Учитывая, что значение компенсирующего сигнала, на любом 1-м такте равно:

е-| A(tg) A,(tj.,)8-«- Ц

+A(te) + Qe)5,,,

где a;e о, l - цифра результата урав1),

новешивания,

а также принимая а/ О (,2,., получим:

A,(t)A,(t, )S +(A,(t2)-bQ,)iy Q,S + (A (tj).+Q,)5 ;

Q

l,(t,)A,(t2)i + (A5(t,)+Q,)

.. , , Q,5 + (A(t3,)+Q,j)55 +(А(ц) +

+Qi)S ;

A(te)A,(te.,)5+(Ac,(tg)+Qg)5 q, +(A.(t,)+Q,V&t«- +... ... + (A.(te.,)+Qe..)S S +(A (tg) +

+Qe)-- .

Компенсирующий сигнал, описываемый данными уравнениями, показан на фиг. 2. Отметим, что с учетом сделанного допущения об отсутствии ошибки кодирования на первом такте для доказательства правильности А-Ц преобразования необходимо показать, что в этом случае при(значении дополнительного сигнала, равного Afl(tg).) при любом входном сигнале не произойдет появления соседних ошибок кодирования типа выключение, Последнее будет возможным, если значение компенсирующего сигнала на любом 1-м такте не превысит предельного значения входного сигнала, равного

Вк .np

AK(te) A

QB-..

(A)

ex. np

выключение (1-0т.е.

При Ae, - в,.„р И 1-го разрядов не может быть ском- Йенсировано включением младших раз- ряцов, т.к. h .

QE-. .Z1 Q, - Qp., -сСа ,

.

Очевидно, что ингзш значения А рассматривать нецелесообразно потому, -Отопри увеличивается веро jiiTHocTb включения Qg, а при А ;

ЧА

ь.пр включение 1-го разряда не йриводит к неуравновешиванию Ац сиг Йалом Ак(1„,). Для доказательства от йутствия на 1-м такте соседней ошиб йи кодирования типа включение (пер йая произошла на (1-1)-м такте) пре- фбразуем полученное выражение для A,((tg). Выразим в последнем Q, че- )ез Qg и просуммируем все остальные Слагаемые, представляющие убывающую еометрическую прогрессию со знаменателем odS 1. Получим:

чвA,(te)Qg(r4(A(t,,)Qg) Приравнивая первое слагаемое

Р-(

A(tg) к нулю, т.к. (fl/8) « 1, а факже положив, исходя из (4), A(tg) Qf-(« определим S, Итак:

S

Qe., (An(te)fQe) у;--5или

об (jA,(t,)-fI) |,

S AoCtg). - относительное значение сигнала Aa(tg)... Отсюда

о 2L..l-:. -S A(tg)

Подставим найденное значение 5 в йыражение (3), определим Aa(tp):

(5)

&A.(tg) oi -5A,(tg) ,

d причем

(6)

Qi A.(tj) /2.

(6a)

Вышеприведенные выражения (5), (6), (6a) позволяют по заданному значению А,, (tn ) определить остальные

A(t;) фиксируется в блоке 2 по за нему фронту импульса, поступающему от Генератора 7 (по переднему фрон этого же импульса происходит модиф кация содержимого счетчика 4 и регистра 9) .

На втором такте кодирования с

параметры кодирования (S и5A„,(tp). ) приходом импульса от генератора 7

для любого варианта предложенного способа А-Ц преобразования. Отличительной особенностью последнего яв

ляется адаптивность, заключающаяся в том, что формирование дополнительного сигнала на каждом 1-м такте осуществляется не только с учетом номера такта, но и в зависимости от входного и погрешностей установления компенсирующего сигнала., т.е. от результантов сравнения входного и

компенсирующего сигналов на предыдущих (1,2,..., (1-1)-м) тактах.. Отметим универсальность предложенного адаптивного способа А-Ц преобразования. Так, при S AnCtg ) oilV2 получим

A,(te)Aj(tp) ot-V2 и S Ы- что совпадает с параметрами известного способа А-Ц преобразования при ы, 1,618.

Работа устройства происходит следующим образом.

Начинается цикл А-Ц поразрядного кодирования после прихода сигнала Запуск. При этом на выходе регистра 9 устанавливается в единичное состояние старший первый разряд (ос- . тальные разряды имеют нулевое значение) и на выходе блока 8 устанавливается кодовая комбинация Кд , полученная на основании выражения (6) и записанная в блок 8 на этапе изготовления. Через блок 5 логических элементов ИЛИ коды выходов регистра 9 и блока 8 поступают на вход ЦАП 3, на выходе которого при этом появляется компенсирующий аналоговый сиг-нал, соответствующий сумме основного компенсирующего и дополнительного аналоговых сигналов и имеющий значение, равное к концу первого такта A(t,). Сигнал A(t, ) сравнивается с входным сигналом при помощи блока 2, выходной сигнал Y которого подчиняется следующему соотношению:

Y:

О, А,, AJt;);

,1

4(ti). Каждый результат сравнения А

5Х

A(t;) фиксируется в блоке 2 по заднему фронту импульса, поступающему от Генератора 7 (по переднему фронту этого же импульса происходит модификация содержимого счетчика 4 и регистра 9) .

На втором такте кодирования с

приходом импульса от генератора 7

на выходе регистра 9 устанавливается в единичное состояние следующий второй разряд. Состояние первого разY l, то первый разряд остается включенным, если Y, О - выключается. Аналогично от результата сравнения, полученного на предыдущем такте (в данном случае Y, ) зависит и кодовая комбинация на адресных входах блока 8, младшие m разрядов которой (т logjn) задаются счетчиком 4 и определяют номер такта кодирования, а старший т-й разряд является выхо дом блока 2 и определяет относительное значение дополнительного сигнала

S AaCt;). или SAa(t;-) . В ЭТОМ СЛучаВ

при Y,0 на выходе блока 8 устанавливается кодовая комбинация, синтезированная на этапе изготовления с учетом выбранного значения ) и соотношения (6а) , а при Y, 1 -. кодовая комбинация, синтезированная

из выражения (6).

I.

Работа устройства на любом j-м такте происходит аналогично и заканчивается на (п+1)-м |такте поразряд- кого кодирования. При этом сигнал АВУ уравновешен компенсирующим сигналом ЦАП 3 с точностью до единицы младшего п-го разряда, на первом выходе 10 устройства находятся вы- ходной код, являющийся цифровым эквивалентом А, а на втором выходе

I1устройства присутствует сигнал окончания преобразования.

Формула изобретен и я

Способ аналого-цифрового преобразования, основанный на поразрядном уравновешивании входного аналогового сигнала, заключающийся в том, что

нал уравновешивания, равный сумме основного компенсирующего сигнала поразрядного уравновешивания и первого дополнительного компенсирующего сигнала той же полярности, и осуществляют сравнение входного аналогового сигнала с сигналом уравновешивания, по результатам сравнения на всех тактах осуществляют формирование выходного кода, отлич аю- щ и и с я тем, что, с целью повьш1 е- ния быстродействия, по результату сравнения на i-м такте входного аналогового сигнала с сигналом уравновешивания э случае превьшения сигнала уравновешивания над входным аналоговым сигналом осуществляют на (i+l)-M такте до формирования сигнала уравновешивания формирование второго дополнительного компенсирующего сигнала противоположной первому полярности, который при формировании сигнала уравновешивания суммир5гют с основным и первым дополнительным компенсирующими сигналами данного такта, при этом в.еличину первого дополнительного компенсирующего сигнала выбирают равной:

A.(i) Q,( /2

+ К),

а величину второго дополнительного компенсирующего сигнала равной

V

q i . 2К,

где fli - основание избыточного измерительного кода; Q - вес i-ro разряда кода;

0 .

V,

9(t,)x

A8xf

Мх.прг -/--

Абх.пр.З

Ш.пр.(t2

.(ti),

AK(tif)A8x.np.3

5 Такты

1-

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Способ аналого-цифрового преобразования | 1985 |

|

SU1304172A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| ТЕХНИЧЕСКАЯ "W БИБЛИОТЕКАГ. В. Москаленко | 1969 |

|

SU253457A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1977 |

|

SU737965A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразовательпОРАзРядНОгО уРАВНОВЕшиВАНия | 1979 |

|

SU818003A1 |

| Функциональный преобразователь напряжения в код | 1979 |

|

SU928634A2 |

Изобретение относится к области вычислительной цифровой измерительной техники и может быть использовано для преобразования аналоговых величин в цифровые. Цель изобретения - повышение быстродействия аналогоцифрового преобразования - достигается при поразрядном уравновешивании входного аналогового сигнала суммой основного компенсирующего аналогового сигнала поразрядного уравновешивания, соответствующего весам избыточного измерительного кода, и первого дополнительного компенсирующего сигнала той же полярности путем формирования на тактах уравновешивания, которым предшествовало превышение сигнала уравновешивания над входным аналоговым сигналом, второго дополнительного компенсирукщего сигнала противоположной полярности, который суммируется при формировании сигнала уравновешивания с основным и первым дополнительным компенсирующим сигналами. 2 ил. с S сл

1 -аналоговый сигнал фиг. 2

| Лаврентьев В | |||

| И | |||

| и др | |||

| Аналого- цифровые преобразователи двустороннего уравновешивания | |||

| Киев: Общество Знание УССР, 1982 | |||

| Способ аналого-цифрового преобразования | 1985 |

|

SU1304172A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-05—Подача