11

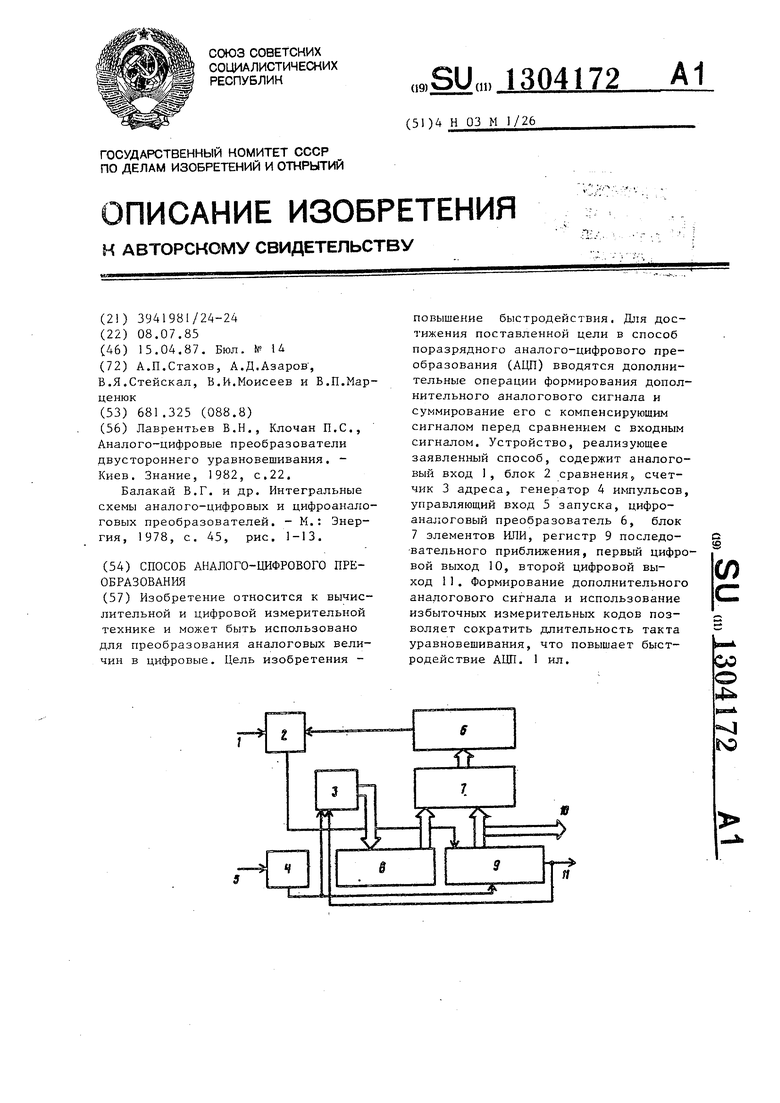

Изобретение относится к автоматике и цифровой измерительной технике и может быть использовано для пре- образования аналоговых величин в цифровые.

Цель изобретения - повышение быстродействия аналого-цифрового преобразования.

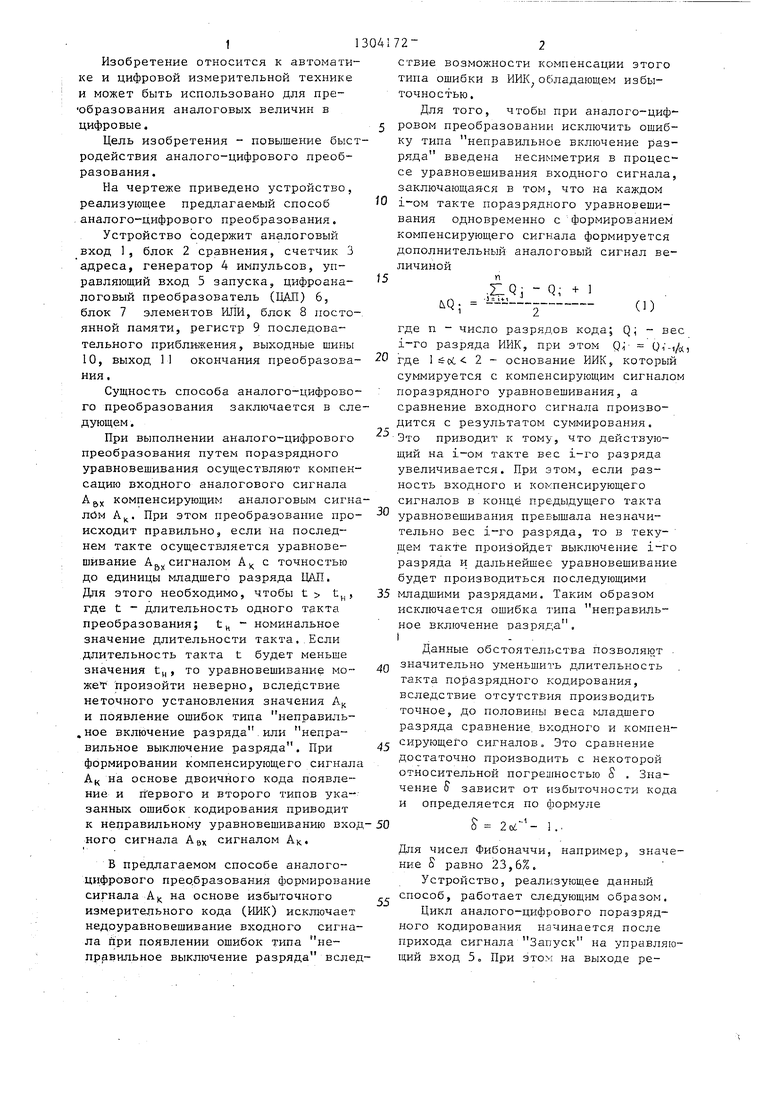

На чертеже приведено устройство, реализующее предлагаемый способ .аналого-цифрового преобразования.

Устройство содержит аналоговый вход 1, блок 2 сравнения, счетчик 3 адреса, генератор 4 импульсов, управляющий вход 5 запуска, цифроана- логовый преобразователь (ЦАП) 6, блок 7 элементов ИГШ, блок 8 постоянной памяти, регистр 9 последовательного приближения, выходные шины 10, выход 11 окончания преобразова- ния.

Сущность способа аналого-цифрово- го преобразования заключается в следующем .

При выполнении аналого-цифрового преобразования путем поразрядного уравновешивания осуществляют компенсацию входного аналогового сигнала Agx компенсирующим аналоговым сигналим Ац. При этом преобразование про исходит правильно, если на последнем такте осуществляется уравновешивание Аg,,,. сигналом А у, с точностью до единицы младшего разряда ЦАП. Для этого необходимо, чтобы t t.,, где t - длительность одного такта преобразования; t - номинальное значение длительности такта..Если длительность такта t будет меньше значения t,.,, то уравновешивание мо- жет произойти неверно, вследствие неточного установления значения А, и появление ошибок типа неправиль- .ное включение разряда.или неправильное выключение разряда. При формировании компенсирующего сигнал Ац на основе двоичного кода появление и Цервого и второго типов указанных ошибок кодирования приводит к неправильному уравновешиванию вхо кого сигнала АВХ сигналом АК.

В предлагаемом способе аналого- цифрового прео.бразования формирован сигнала А) на основе избыточного измерительного кода (ШК) исключает недоуравновешивание входного сигнала при появлении ошибок типа неправильное выключение разряда всле

72-2

ствие возможности компенсации этого типа ошибки в ИИК обладающем избыточностью.

Для того, чтобы при аналого-цифровом преобразовании исключить ошибку типа неправильное включение разряда введена несимметрия в процессе уравновешивания входного сигнала, заключающая-ся в том. что на каждом i-OM такте поразрядного уравновешивания одновременно с формированием компенсирующего сигнала формируется дополнительный аналоговый сигнал величиной

25

, 0

: 3540 45 - 50

е г с

30

,}lQj - Q; + 1

™--2 (О

где п - число разрядов кода; Q; - вес i-ro разряда ИИК, при этом Q Ui -i/c() где 2 - основание ИИК, который суммируется с компенсирующим сигналом поразрядного уравновешивания, а сравнение входного сигнала производится с результатом суммирования. Это приводит к тому, что действующий на L-OM такте вес i-ro разряда увеличивается. При этом, если разность входного и компенсирующего сигналов в конце предыдущего такта уравновешивания превышала незначительно вес i-ro разряда, то в текущем такте произойдет выключение i-ro разряда и дальнейшее уравновешивание будет производиться последующими lлaдшими разрядами. Таким образом исключается ошибка типа неправильное включение разряда. i . Данные обстоятельства позволяю/ .

значительно уменьшить длительность такта поразрядного кодирования, вследствие отсутствия производить точное, до половины веса младшего разряда сравнение, входного и компенсирующего сигналов. Это сравнение достаточно производить с некоторой относительной погрелшостью S . Значение ff зависит от Р збыточности кода и определяется по формуле

1..

Для чисел Фибоначчи, например, значение S равно 23,6%.

Устройство, реализующее данный способ, работает следующим образом.

Цикл аналого-цифрового поразрядного кодирования начинается после прихода сигнала Запуск на управляющий вход 5. При этом на выходе ре

1

гистра 9 последовательного приближе- ния ,устанавливается в единичное состояние старший 1-й разряд -(остальные разряды имеют нулевое значение), На выходе блока 8 устанавливается ко Kf/iQi/s полученный на основании выражения (1) и записанный в блок 8 на этапе изготовления. Через блок 7 коды с выходов регистра 9 последователного приближения и блока 8 поступают на вход ЦАП 6, в котором происходит формирование и суммирование основного компенсирующего и дополнительного сигналов. На выходе ЦАП 6 появится компенсирующий аналоговый сигнал А

Сравнение сигналов А... и

ил

Q,+ bQ,

А j, производится в блоке 2, выходной сигнал yj которого подчиняется

следующему условию:

л

6Х

У; е

fo,il

о, Аас А.

А А б KV

При этом, если на первом такте уравновешивания у, 0, то 1-ьш раз- ряд устанавливается в нулевое состо- яние, если же у 1, то 1-ый разряд остается в единичном состоянии на последующих тактах уравновешивания. На втором такте аналого-цифрового преобразования по сигналу генератора 4 импульсов изменяется на единицу содержимое счетчика 3 адреса и на выходе блока 8 устанавливается код Kj/AQ /, причем K2//iQ5/ K,/AQ,/s2. Одновременно на выходе регистра 9 последовательного приближения устанавливается в единичное состояние 2-ой разряд. После очередного сравнения входного и компенсирующих сигна- лов 2-ой разряд либо устанавливается в нулевое состояние , либо ос

Редактор М,Товтин

Составитель В.Першиков

Техред ИоПопович Корректор Е.Рошко

Заказ 1324/57. Тираж 902Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

5 5

5 0 5 0

1724

тается в единичном состоянии . На последующих тактах работа устройства происходит аналогично. После окончания п тактов поразрядного уравновешивания на выхрдных шинах 10 находится код К, , являющийся цифровым эквивалентом входного аналогового сигнала А.., а на выходе 11 - сигнал окончания преобразования.

Формула изобретения Способ аналого-цифрового преобразования, основанный на поразрядном уравновешивании входного аналогового сигнала, заключающийся в том, что на каждом i-ом такте формируют компенсирующий аналоговый сигнал, осуществляют сравнение входного аналогового сигнала с компенсирующим анало- 0 говым сигналом и запоминают результат сравнения, отличающий- с я тем, что, с целью повьшения быстродействия, одновременно с формированием компенсирующего аналогового сигнала формируют дополнительный аналоговый сигнал величиной &Q,

.: Q; - Q; + 1

j L-i;;Г де п - число

разрядов кода; Q| - вес i-ro разряда, и перед сравнением с входным аналоговым сигналом суммируют компенсирующий и дополнительный аналоговые сигналы, а сравнение входного аналогового сигнала осуществляют с сигналом результата суммирования, при. этом формирование компенсирующего аналогового сигнала осзпцествляют на основе избыточного измерительного кода с весами Q. Qi,/cij где 1 2 - основание избыточного измерительного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| Способ аналого-цифрового преобразования | 1986 |

|

SU1388985A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1288913A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Цель изобретения повышение быстродействия. Для достижения поставленной цели в способ поразрядного аналого-цифрового преобразования (АЦП) вводятся дополнительные операции формирования дополнительного аналогового сигнала и суммирование его с компенсирующим сигналом перед сравнением с входным сигналом. Устройство, реализующее заявленный способ, содержит аналоговый вход 1, блок 2 сравненияS счетчик 3 адреса, генератор 4 иьшульсов, управляющий вход 5 запуска, цифро- аналоговый преобразователь 6, блок 7 элементов ИЛИ, регистр 9 последовательного приближения, первый цифровой выход 10, второй цифровой выход 11. Формирование дополнительного аналогового сигнала и использование избыточных измерительных кодов позволяет сократить длительность такта уравновешивания, что повышает быстродействие АЦП. 1 ил. о (О сл с со о 4

| Лаврентьев В.Н., Клочан П.С., Аналого-цифровые преобразователи двустороннего уравновешивания | |||

| - Киев | |||

| Знание, 1982, с.22 | |||

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы аналого-цифровых и цифроанало- говых преобразователей | |||

| - М.: Энергия, 1978, с | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-04-15—Публикация

1985-07-08—Подача