i

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Псевдолинейное корректирующее устройство | 1982 |

|

SU1103197A1 |

| Нелинейное корректирующее устройство с фазовым опережением | 1988 |

|

SU1718182A1 |

| Устройство для управления статическим тиристорным компенсатором | 1985 |

|

SU1309175A1 |

| Способ регулирования частоты вращения двигателя внутреннего сгорания и устройство для его осуществления | 1983 |

|

SU1149045A1 |

| Экстремальный регулятор для резонансного объекта | 1982 |

|

SU1035564A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| ПЕРЕМЕННОЙ СТРУКТУРОЙ | 1970 |

|

SU288083A1 |

| Устройство для измерения полного сопротивления цепи фаза-нуль | 1979 |

|

SU797354A1 |

| Устройство для измерения характеристик внутреннего трения | 1987 |

|

SU1552067A1 |

| Датчик сил упругой деформации механизма и устройство для его настройки | 1985 |

|

SU1288511A1 |

Изобретение относится к автоматическому управлению и регулированию и позволяет повысить качество работы систем. Цель изобретения - повышение точности воспроизведения формы входного сигнала при раздельной регулировке амплитудной и фазовой характеристик. Ус тройство содержит дифференциатор 1, запоминающий элемент 2, интегратор 3, первый 4 и второй 5 масштабные блоки, нуль-орг-ан 6 и сумматор 7 . 2 ил.

AV

оо х

о

СП

СО

Фид.1

5Изобретение относится к автоматическому управлению и регулированию и позволяет повысить качество работы систем.

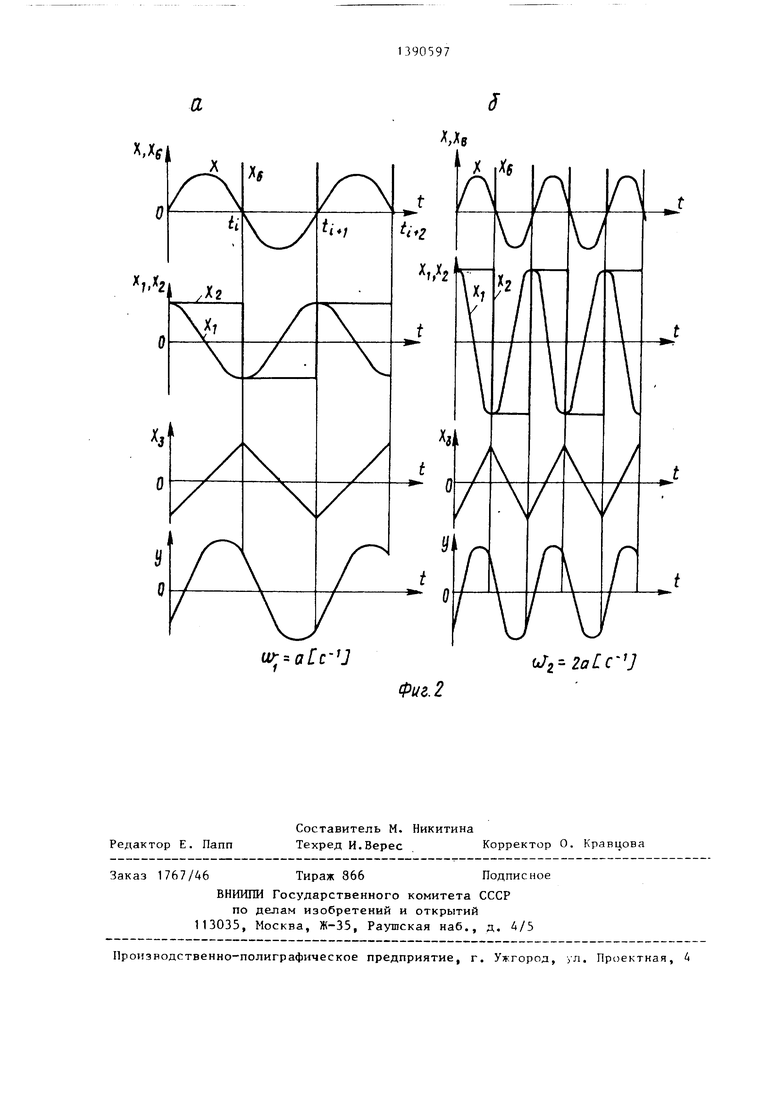

Цель изобретения - повышение точности воспроизведения формы входного сигнала при раздельной регулировке амплитудной и фазовой характеристик. На фиг. 1 представлена структурная схема корректирующего устройства; на фиг. 2 - временные диаграм о 1, иллюст- трирующие работу устройства при двух значениях частоты входного сигнала.

Устройство (фиг. 1) включает дифференциатор 1, запоминающий элемент 2, интегратор 3, первый 4 и второй 5 масштабные блоки, нуль-орган 6 и сумматор 7;

На фиг. 1 и 2 приняты следующие обозначения: X - входной сигнал; Y - выходной сигнал; Xi - сигнал на выходе дифференциатора (Х ,Х ); Х - сигнал на выходе запоминающего элемента; X 3 - сигнал на выходе интегратора; X J - выходные сигналы соответственно первого и второго масштабных блоков; Х( - выходной сигнал нуль-органа; u),, значения частоты входного сигнала.

Устройство работает следующим образом.

Входной сигнал X поступает на дифференциатор 1, нуль-орган 6 и второй масштабньш блок 5. Выходной сигнал нуль-органа 6 представляет собой последовательность импульсов, вырабатываемых в моменты времени tj, когда входной сигнал X переходит из положительной области в отрицательную, и наоборот. Эти импульсы поступают на управляющий вход запоминающего элемента 2, который фиксируе сигнал X ,Х на выходе дифференциатора в моменты t-, сохраняя постоянным зафиксированное значение амплитуды сигнала X ,Х на промежутке t ., tj+1J, В результате сигнал X, преобразуется запоминающим элементом 2 в кусочно-постоянный сигнал X , которьп после интегрирования в инте1 раторе 3 через первьп масштабньй блок 4 поступает на первый вход сумматора 7, на второй вход которого поступает входной сигнал X, прошедший через второй масштабный биок 5.

0

5

0

5

0

5

0

5

0

5

Временные диаграммы, представленные на фиг. 2, иллюстрируют работу устройства для двух случаев, отличающихся частотой входного сигнала (ы, аСс ; w, , где а const).

Из анализа работы устройства и представленных временных диаграмм видно, что амплитуда сигнала Xj на выходе интегратора 3 при изменении частоты входного сигнала X остается постоянной, так как при возрастании частоты пропорционально возрастает амплитуда сигнала X, на выходе дифференциатора 1, а следовательно, и уровень сигнала Х на выходе запоминающего элемента 2. Фаза выходного сигнала Y определяется параметрами масштабных блоков 4 и 5 и может изменяться в диапазоне 0-(-90) . Так, если коэффициент передачи второго масштабного блока равен О, а первого - не равен нулю, то фаза выходного сиг.нала равна в обратном случае фаза его равна 0. Форма выходного сигнала Y устройства практически полностью соответствует форме входного сигнала.

Формула изобретения

Корректирующее устройство, содержащее дифференциатор, вход которого является входом устройства, запомина- ЮП1ИЙ элемент, интегратор, нуль-орган, первьй масштабньй блок и сумматор, первый вход которого соединен с выходом первого масштабного блока, а выход является выходом устройства, отличающеес я тем, что, с целью повышения точности воспроизве- дения формы входного сигнала при раздельной регулировке амплитудной и фазовой характеристик, в него введен второй масштабный блок, выход которого подключен к второму входу сумматора, а вход является входом устройства и соединен с входом нуль-органа, выход которого подключен к управляющему входу запоминающего элемента, соединенного сигнальным входом с выходом дифференциатора, а выходом через интегратор - с входом первого масштабного блока.

.Xtfj

Х5

а.

bh

Дг

XT

j О

a flfc- J

//г.-

| Нелинейные корректирующие устройства в системах автоматического управления./Под ред.Ю.И.Топчеева.- М.: Машиностроение, 1971, с | |||

| Станок для изготовления из дерева круглых палочек | 1915 |

|

SU207A1 |

| Псевдолинейное корректирующее устройство | 1982 |

|

SU1103197A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-04-23—Публикация

1986-05-05—Подача