(Л

с

врго запоминающего устройства 8 в КсОкдый канал преобразования и блока oriopHbDc сигналов 2, что позволяет осуществлять преобразование мгновенных значений в моменты О, Т/4, -1/2,

ЗТ/А, где Т - период сигнала по всем каналам за один цикл изменения уравновешивающего напряжения, без остановок для опроса сработавших каналов. 1 3 , п. ф-лы, 2 И.П,

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Двухканальное устройство для акустико-эмиссионного контроля | 1988 |

|

SU1508140A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Способ определения мгновенных значений фазового сдвига электрических сигналов | 1988 |

|

SU1631458A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Система для проведения испытаний турбины | 1989 |

|

SU1636706A1 |

Изобретение относится к информационно-измерительной технике и может быть использовано при построении высокопроизводительных систем сбора и обработки аналоговых сигналов. Изобретение позволяет ПОВЫСИТЬ быстродействие И расширить функциональные возможности за счет измерения амплитуды И ортогональных составлякшщх сигнала. Это достигается введением регистро

1

Изобретение относится к информационно-измерительной технике и может быть использовано при построении высокопроизводительных систем сбора и обработки аналоговых сигналов.

Целью изобретения является повышение быстродействия и расширение функциональных возможно стей за счет Измерения амплитуды и ортогональных составляющих сигнала,

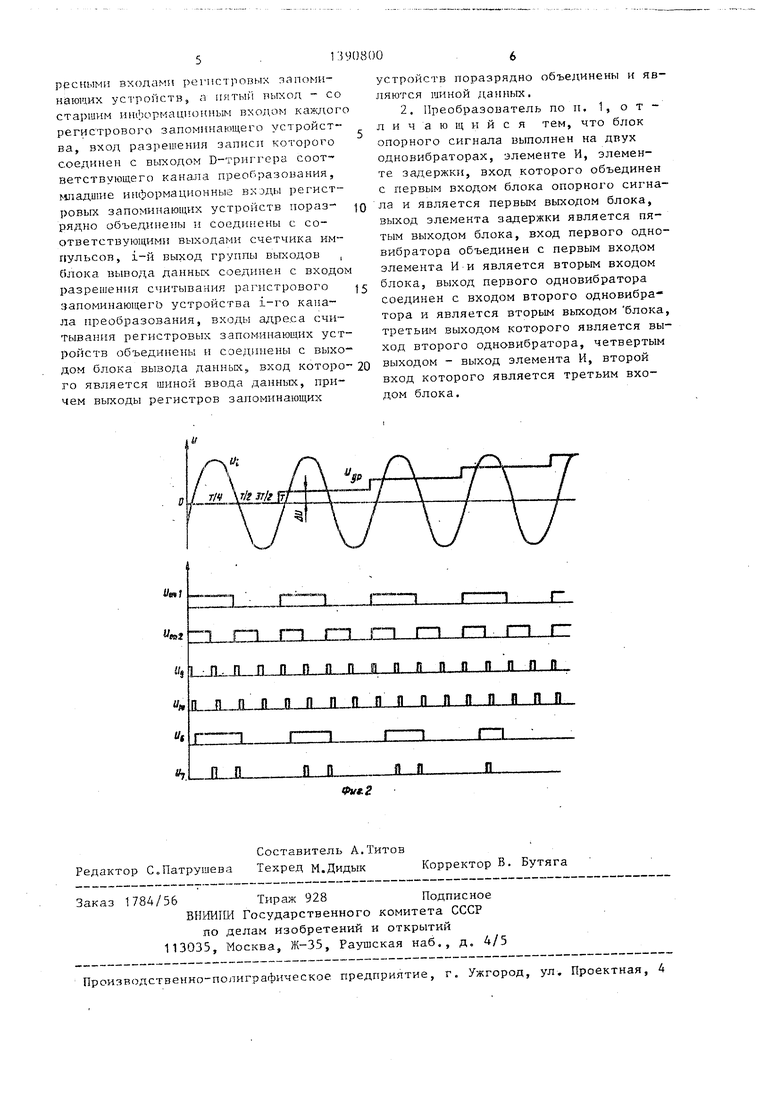

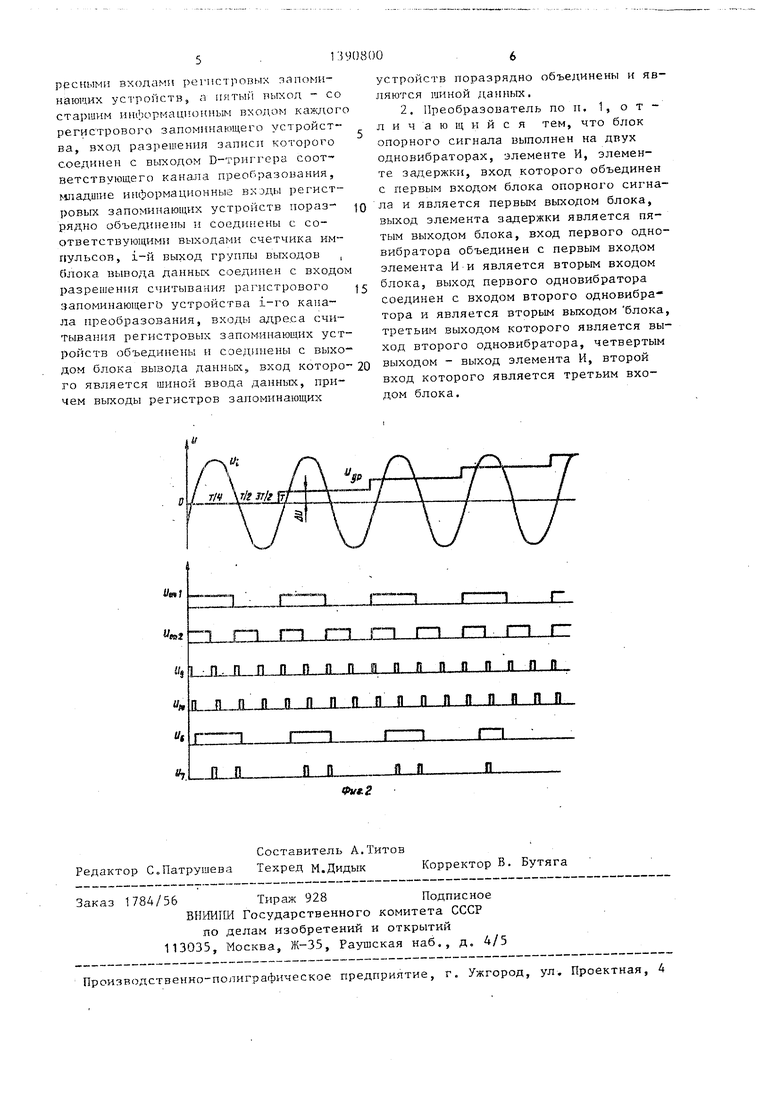

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 - времен- н|ые диаграммы работы устройства.

Устройство (фиг. 1) содержит N ка- Налов 1 преобразования аналоговых ве- личин, блок 2 опорного сигнала, счетчик 3 импульсов, ЦИфроаНсШОГОВЬЕЙ

преобразователь () А, блок 5 вывода данных. Каждьй канал 1 образован компаратором 6, D-триггером 7, регист ровым запоминающим устройством 8 (ЗУ) Влок 2 содержит одновибраторы 9 и 10, элемент И 11, элемент 12 задержки. На временной диаграмме (фиг. 2) обозначено и - напряжение на втором входе компаратора 6, и напряжения на первом и втором входах блока 2, Ug, и , Uj, и - напряжения на выходах соответствующих блоков 9 и 10, 6 и 7.

Работа данного устройства осуществляется под управлением внешнего устройства, например ЭВМ, которое вырабатывает опорные сигналы , сигнал управления Uyn, формирует ко- Вывод данных, а также имеет ОЗУ для приема и хранения данных. Логический уровень сигнала управления и определяет режим работы устройства, при уровне логической единицы - режим измерения ортогональных составляющих комплексного сигнала, а при уровне логического нуля - режим измерения ам1гпитуды.

5

0 0

5

5

В исходном состоянии D-триггер 7 каждого канала и счетчик 3 установлены в нулевое состояние. На выходы компараторов 6 каналов поступают соответствующие входные сигналы

и (t)A.sin(2«-m ), ().

Режим измерения ортогональных составляющих. Опорные сигналы ,, и опа представляют меандры, имеюи;ие соответственно частоту измеряемого сигнала f и двойную частоту fof,2 2f. С поступлением на первый и второй входы блока 2 опорных сигналов начинается уравновеишвающее преобразование. На каждом такте преобразования, равном периоду измеряемого сигнала, вырабатываются импульсы: импульс такта Ujjj, , поступающий на счетньш вход счетчика 3 и увеличивающий напряжение на выходе ЦА11 на 1U, импульсы строба UQ в моменты времени t,0, t2

Т Т ЗТ г, , , поступающие на Gвход D-триггера 7 канала 1; импульсы сброса , которые формируются по заднему фронту импульса строба: сигнал Адреса записи, который в момент t,U, имеет уровень логической единицы, а в момент , - логического нуля; с пятого- выхода блока 2 сигнал знакового разряда, который является старшим битом информационного слова регистрового запоминающего устройства 8, позволяющий устранить неоднозначность преобразования ортогональных составлякицих. На выходе D-триггера 7 формируется сигнал разрешения записи (V. ): при уровне логической единицы на выходе

компаратора 6 D-триггер 7 по импульсу строба устанавливается в состояние логической единицы, а по импульсу сброса - в состояние логического нуля, Запись в регистровое ЗУ 8

осуществляется в моменты ,

Т

по адресу 1, а в моменты t -, t

IT ч

Drill

зт

7 по адресу О. Моментам t, 0

Т

и tj,7 соответствует уровень логической единицы знакового разряда, а моментам и уровень логического нуля знакового разряда.

Такой алгоритм позволяет определить за цикл развертывающего преобразования значения ортогональных составляющих комплексного сигнала; в моменты t,0, каждого такта CHHфазной составляющей

U,(t,0)A;sin()A sin4 j; и,- ()(,,,

Т ЗТ а в моменты , каждого такта

квадратурной составляющей

U()(2tft2- f,)A.,;

U.(t,p)A,.sin(,+ f,)-AiCOS f

Таким образом, за цикл разверты- Бающего преобразования (T,j,) осуществляется кодирование и запись ортогональных составляющих в каждом ка

нале.

-J - Ти

где Т - период измеряемого сигнала; и „„ --максимальное значение К.

плитуды измеряемого сигнала;ли - шаг квантования;

/

jjj sa/ss число тактов преобразования

А и

Режим измерения амплитуды комплексного сигнала. На управляющем входе Uyp - уровень логического нуля Опорный сигнал - меандр, имеющи частоту измеряемого сигнала. Опорный сигнал Up(,j - меандр, имеюп1ий частоту fg, которая определяет разрешаю- щуго способность аналого-цифрового преобразователя по уровню ((.„)

и равна f

-, где Т Tarccosd - )

период измеряемого сигнала, U - максимальное значение амплитуды, ди - погрешность квантования. С поступлением опорных сигналов на первый и второй входы блока 2 начинается уравновешивающее преобразование. На каж- дом такте преобразования, равном периоду измеряемого сигнала, вырабатываются импульсы: импульс такта, по

S

5

0

0

5

.,

0

0

ступающий на счетный вход счетчика 3 и увеличивающий напряжение на 4U; импульсы строба с частотой стробирова- ния fctn поступающие на С-вход D- триггера 7 канала 1; импульсы сброса, которые формируются по заднему фронту импульсов строба; сигнал Адреса записи, который имеет уровень логичесг кого нуля. До тех пор, пока уравновешивающее напряжение не превзойдет максимальное значение измеряемого сигнала, на выходе D-триггера 7 формируется сигнал Разрешение записи (V,- ) и осуществляется запись в регистровое ЗУ8 в моменты стробирования по адресу (А) О. Такой алгоритм позволяет определить значение амплитуды комплексного сигнала за цикл развертывающего преобразования в каждом канале.

Формула изобретения

устройств поразрядно объединены и являются шиной данных,

| Гитис Э.И | |||

| Аналого-цифровые преобразователи | |||

| -М.: Энергоиздат, 1981, с | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

| Амрамин С.Д | |||

| Мультиплицированные измерительные системы | |||

| - Тезисы докл | |||

| всес | |||

| конф | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-23—Публикация

1986-01-13—Подача