(Р) адреса 1-й свободной страницы, Р адреса 1-й; выдаваемой страницы, Р адреса конца очереди выдаваемой страницы; блок 5 выдачи информации, содержа1чий узел анализа запросов, коммутатор данных, Р адреса выдаваемой страницы, 1-й буферный Р; блок 7 анализа признаков, содержащий узел сканирования запросов, узел сравнения признаков, узел записи адреса :свободной страницы, узел записи а- iголовка, узел записи информации.

Устр-во обеспечивает побайтный прием информации от большого кол-ва источников и формирование страниц информации, принадлежащей одному и тому же источнику, с сохранением порядка поступления байтов, размер всех страниц постоянен. В устр-ве аппаратно реализован динамич.принцип распределения памяти, что позволяет значительно эффективнее использовать выделенный объем памяти, повысив коэф. его загрузки, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

Изобретение относится к обработке измерительной информации. Цель изобретения - повьгаение скорости выборки каналов и снижение объема оперативной памяти, приходящейся на один выбранный канал. Устр-во содержит блок 1 приема информации, коммутаторы 3 и 6, блок 4 оперативной памяти, блок 6 выделения управляющих сигналов. Введены блок 2 динамического распределения памяти, имеющий . узел формирования таблицы адресов страниц, узел чтения/записи адресов свободных страниц, узел чтения адреса выдаваемой страницы, узел записи адреса закрываемой страницы, регистр

1

Изобретение относится к обработке измерительной информации и может быть использовано для ввода измерительной информации в системы обработки данньЬс.

Целью изобретения является повышение скорости выборки каналов и снижение объема оперативной памяти, приходящейся на один выбранный канал

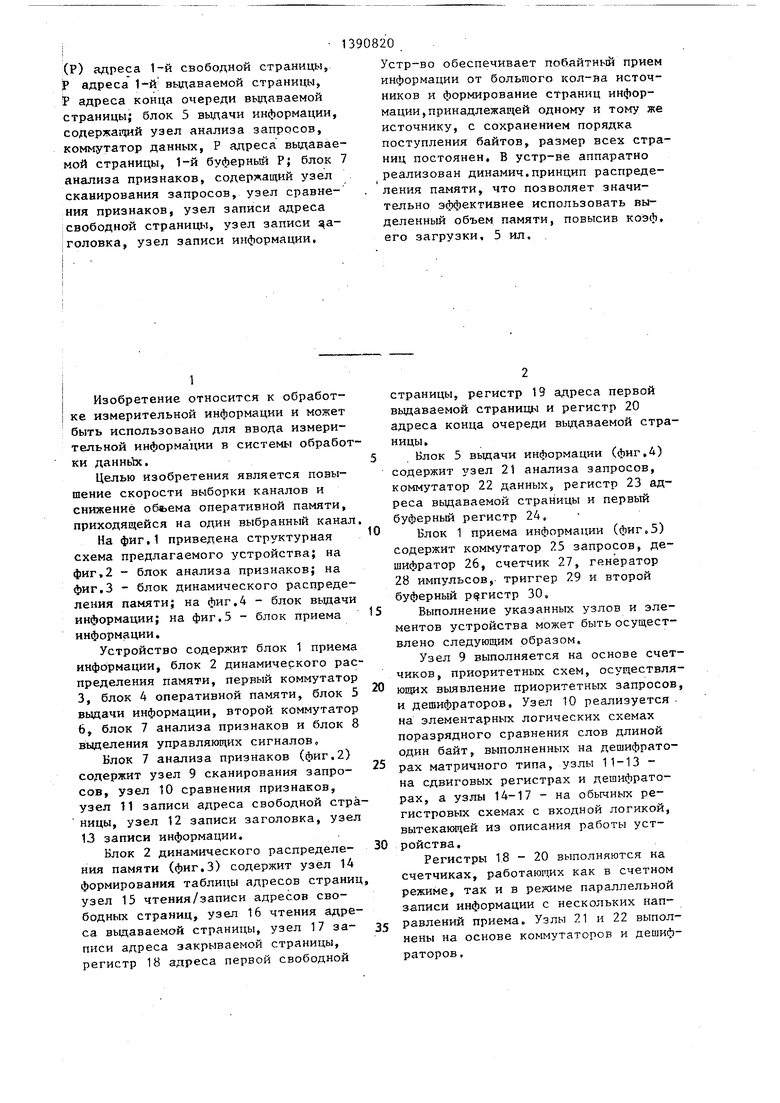

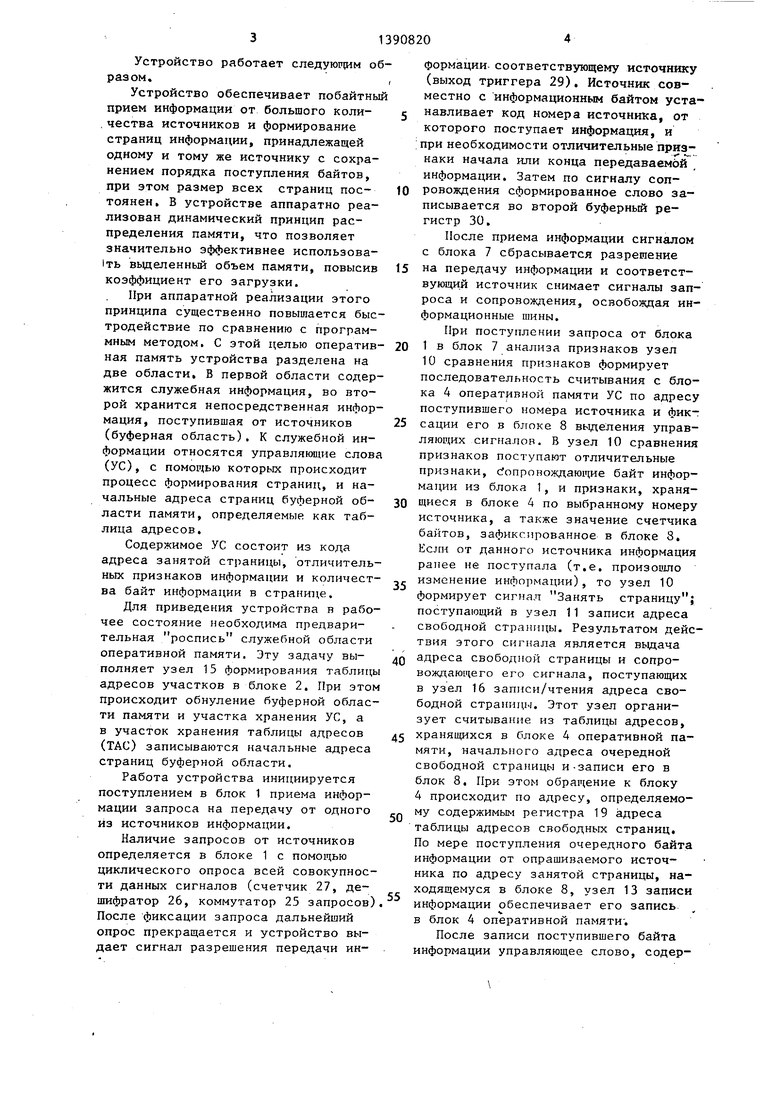

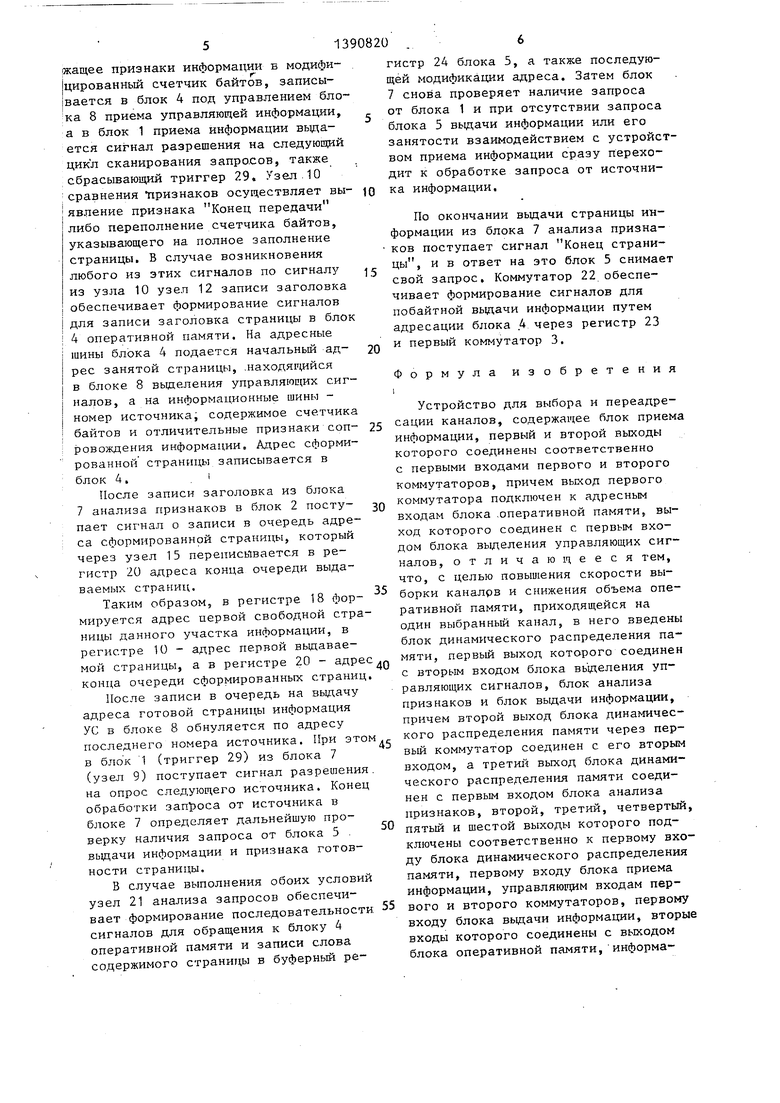

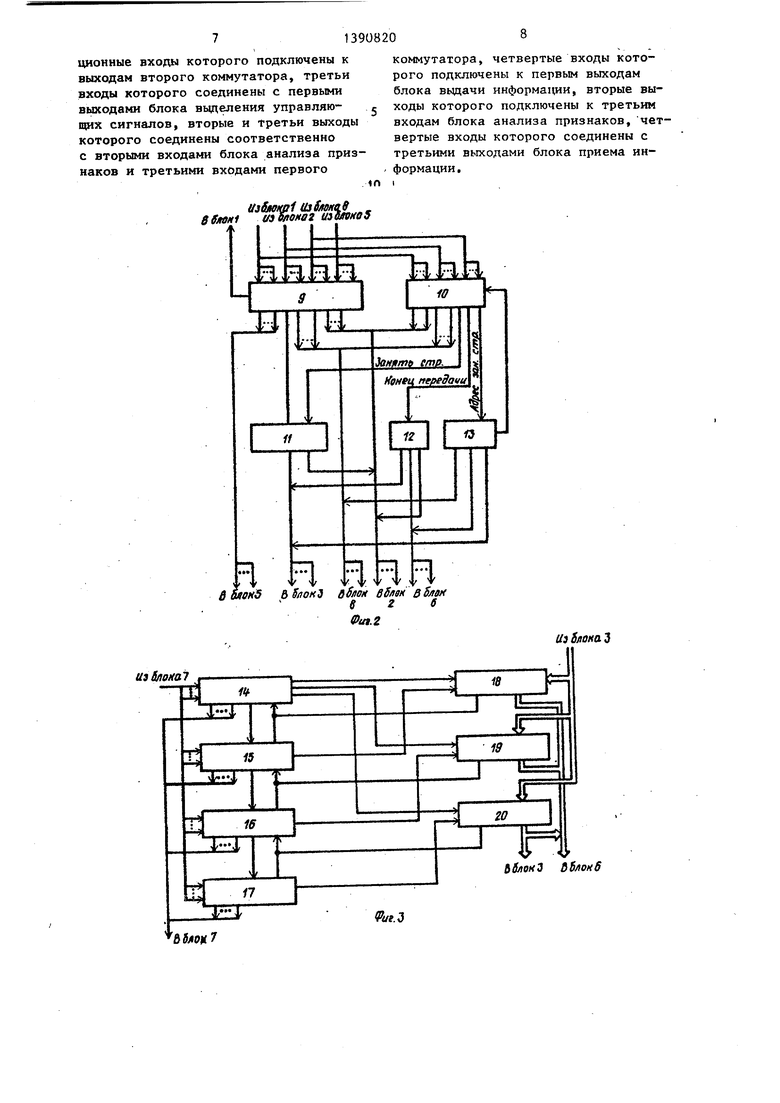

На фиг,1 приведена структурная схема предлагаемого устройства; на фиг.2 - блок анализа признаков; на фиг.З - блок динамического распределения памяти; на фиг,4 - блок вьщачи информации; на фиг,5 - блок приема информации.

Устройство содержит блок 1 приема информации, блок 2 динамического распределения памяти, первый коммутатор 3, блок 4 оперативной памяти, блок 5 выдачи информации, второй коммутатор 6, блок 7 анализа признаков и блок 8 выделения управляющих сигналов,

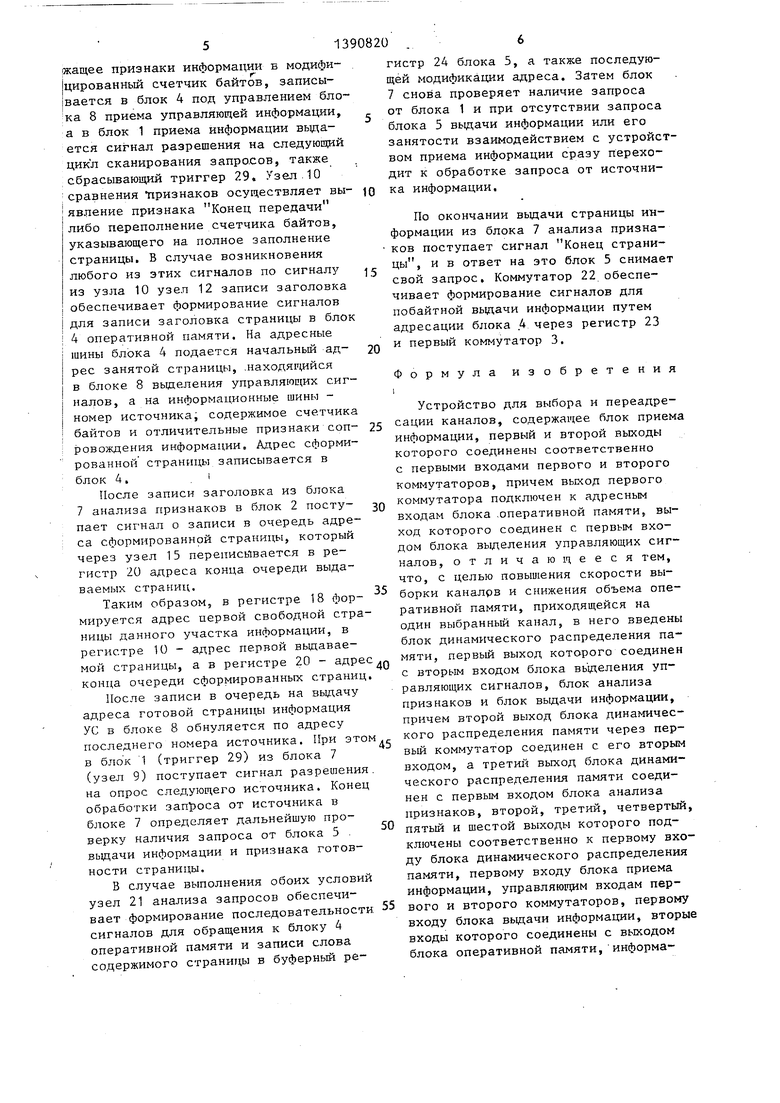

Блок 7 анализа признаков (фиг,2) содержит узел 9 сканирования запросов, узел 10 сравнения признаков, узел 11 записи адреса свободной страницы, узел 12 записи заголовка, узел 13 записи информации.

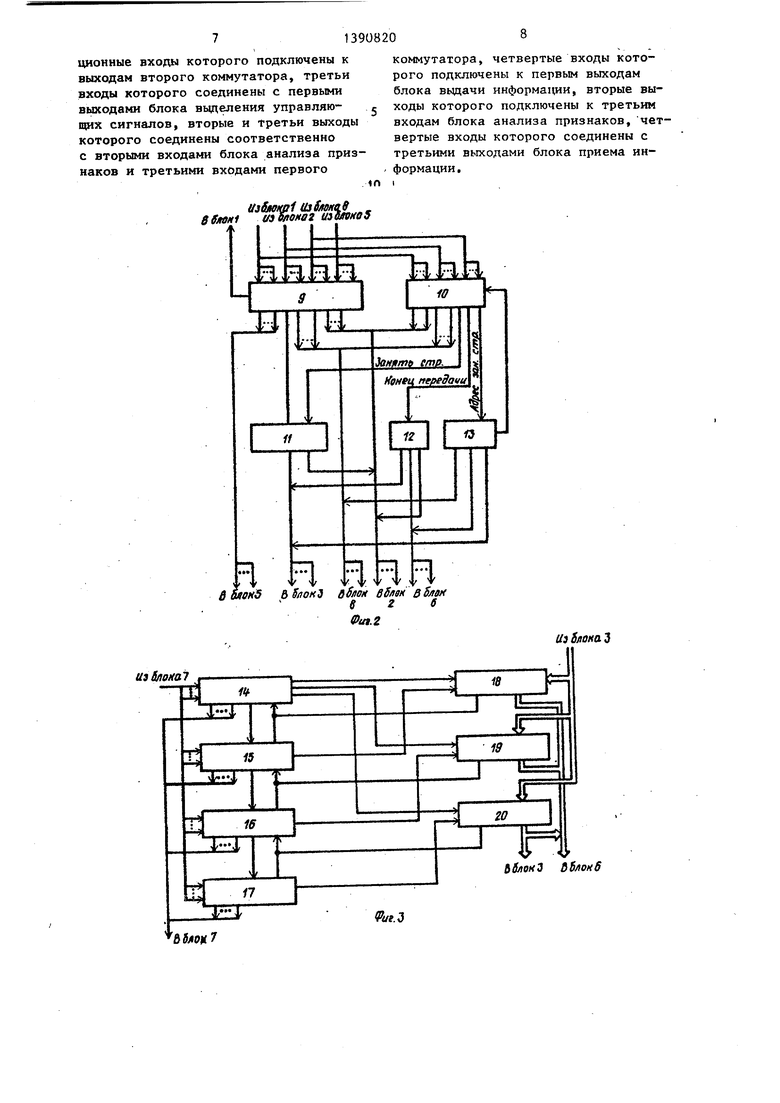

Блок 2 динамического раслределе- ния памяти (фиг,3) содержит узел 14 формирования таблицы адресов страниц узел 15 чтения/записи адресов свободных страниц, узел 16 чтения адреса выдаваемой страницы, узел 17 за- писи адреса закрываемой страницы, регистр 18 адреса первой свободной

страницы, регистр 19 адреса первой выдаваемой страницы и регистр 20 адреса конца очереди выдаваемой страницы .

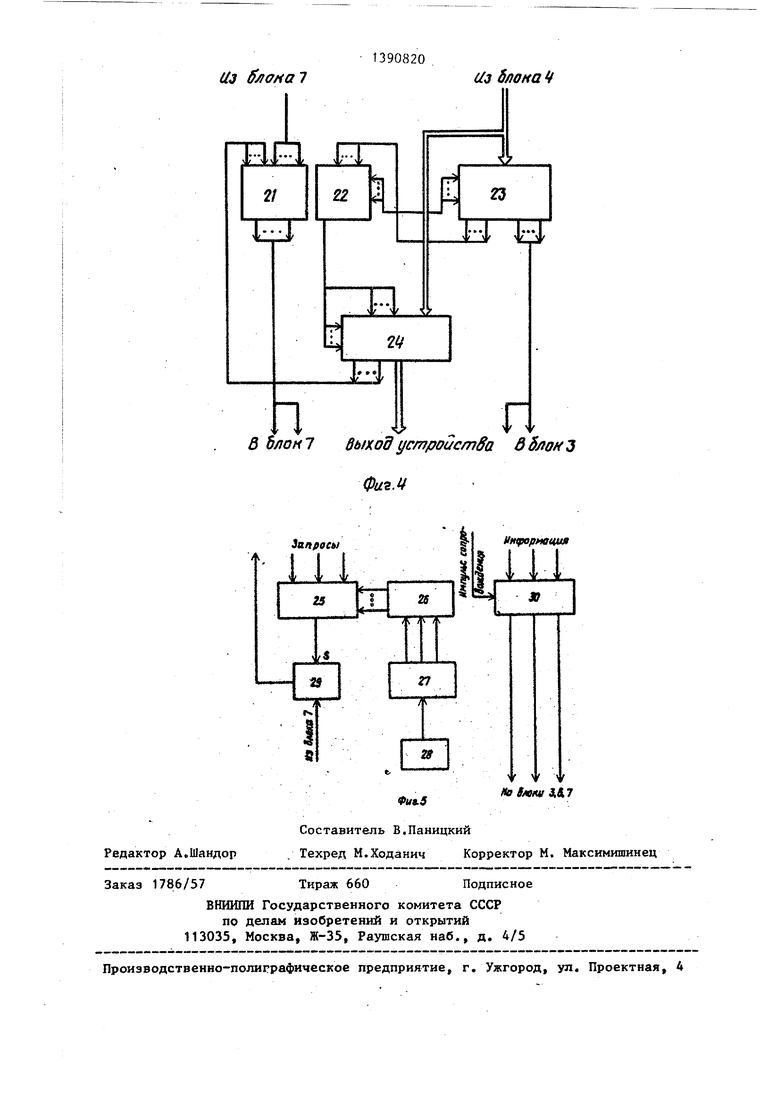

Блок 5 выдачи информации (фиг,4) содержит узел 21 анализа запросов, коммутатор 22 данных, регистр 23 адреса вьздаваемой страницы и первый буферный регистр 24,

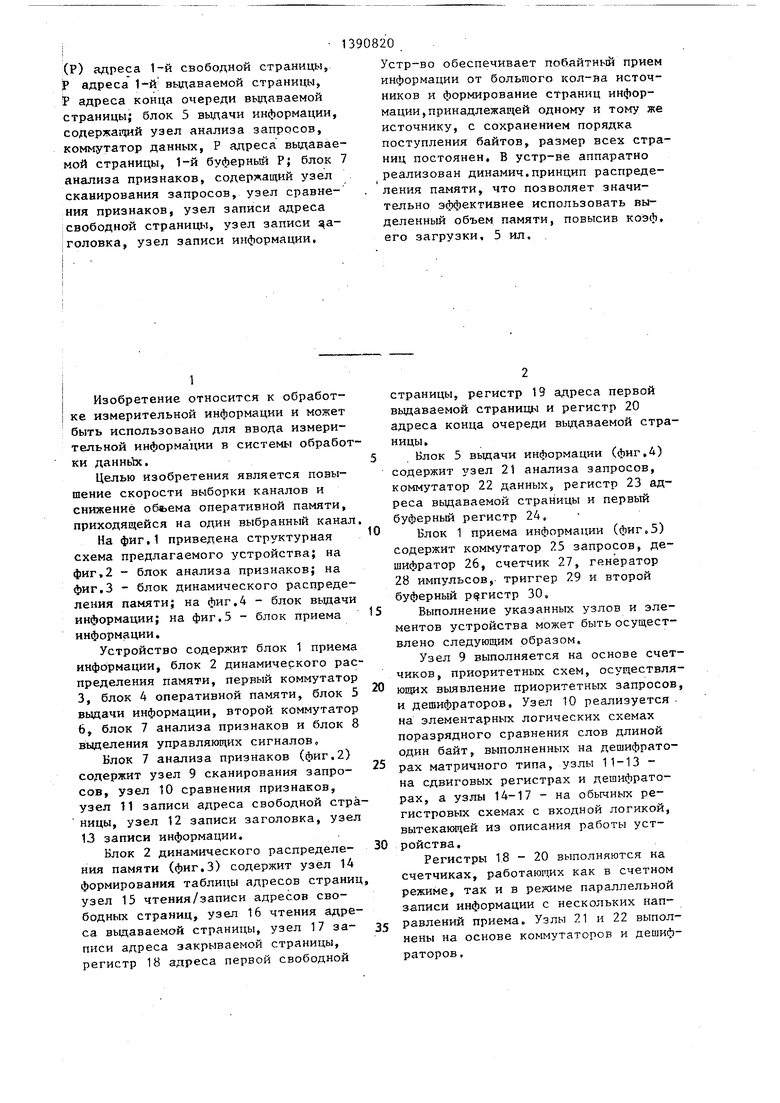

Блок 1 приема информации (фиг,5) содержит коммутатор 25 запросов, дешифратор 26, счетчик 27, генератор 28 импульсов,- триггер 29 и второй буферный регистр 30,

Выполнение указанных узлов и элементов устройства может быть осуществлено следующим образом,

Узел 9 выполняется на основе счетчиков, приоритетных схем, осуществляющих выявление приоритетных запросов и дешифраторов. Узел 10 реализуется на элементарных логических схемах поразрядного сравнения слов длиной один байт, выполненных на дешифраторах матричного типа, узлы 11-13 - на сдвиговых регистрах и дешифраторах, а узлы 14-17 - на обычных регистровых схемах с входной логикой, вытекакщей из описания работы устройства.

Регистры 18 - 20 выполняются на счетчиках, работающих как в счетном режиме, так и в режиме параллельной записи информации с нескольких направлений приема. Узлы 21 и 22 выполнены на основе коммутаторов и дешифраторов .

Устройство работает следующим обазом.I

Устройство обеспечивает побайтный рием информации от большого коли- j честна источников и формирование страниц информации, принадлежащей одному и тому же источнику с сохранением порядка поступления байтов, при этом размер всех страниц пос- 10 тоянен, В устройстве аппаратно реаизован динамический принцип распределения памяти, что позволяет значительно эффективнее использова- ть вьделенньй объем памяти, повысив 15 коэффициент его загрузки.

При аппаратной реализации этого принципа существенно повышается быстродействие по сравнению с программным методом. С этой целью оператив- 20 ная память устройства разделена на ве области, В первой области содерится служебная информация, во второй хранится непосредственная информация, поступившая от источников 25 (буферная область). К служебной информации относятся управляющие слова (УС), с помощью которых происходит процесс формирования страниц, и начальные адреса страниц буферной об- ЗО асти памяти, определяемые как табица адресов.

Содержимое УС состоит из кода адреса занятой страницы, отличительных признаков информации и колнчест- ,,. ва байт информации в странице.

Для приведения устройства в рабочее состояние необходима предварительная роспись служебной области оперативной памяти. Эту задачу вы- Q полняет узел 15 формирования таблицы адресов участков в блоке 2, При этом происходит обнуление буферной области памяти и участка хранения УС, а в участок хранения таблицы адресов дд (ТАС) записываются начальные адреса страниц буферной области.

Работа устройства инициируется поступлением в блок 1 приема информации запроса на передачу от одного из источников информации.

Наличие запросов от источников определяется в блоке 1 с помощью циклического опроса всей совокупности данных сигналов (счетчик 27, дешифратор 26, коммутатор 25 запросов). После фиксации запроса дальнейший опрос прекращается и устройство выдает сигнал разрешения передачи ин50

0 5 О

,.

Q д

0

формации соответствующему источнику (выход триггера 29). Источник совместно с информационным байтом устанавливает код номера источника, от которого поступает информация, и ;при необходимости отличительные приз наки начала или конца передаваемой информации. Затем по сигналу сопровождения сформированное слово записывается во второй буферньй регистр 30.

После приема информации сигналом с блока 7 сбрасывается разрешение на передачу информации и соответствующий источник снимает сигналы запроса и сопровождения, освобождая информационные шины.

При поступлении запроса от блока 1 в блок 7 анализа признаков узел 10 сравнения признаков формирует последовательность считывания с блока 4 оперативной памяти УС по адресу поступившего номера источника и фиксации его в блоке 8 выделения управ- ляюпщх сигналов. В узел 10 сравнения признаков поступают отличительные признаки, Сопровождающие байт информации из блока 1, и признаки, хранящиеся в блоке 4 по выбранному номеру источника, а также значение счетчика байтов, зафиксированное в блоке 8, Если от данного источника информация ранее не поступала (т.е. произоишо изменение информации), то узел 10 формирует сигнал Занять страницу ; поступающий в узел 11 записи адреса свободной страницы. Результатом действия этого сигнала является выдача адреса свободной страницы и сопровождающего его сигнала, поступающих в узел 16 записи/чтения адреса свободной страницы. Этот узел организует считывание из таблицы адресов, хранящихся в блоке 4 оперативной памяти, начального адреса очередной свободной страницы и-записи его в блок 8. При этом обращение к блоку 4 происходит по адресу, определяемому содержимым регистра 19 адреса таблицы адресов свободных страниц. По мере поступления очередного байта информации от опрашиваемого источника по адресу занятой страницы, находящемуся в блоке 8, узел 13 записи информации обеспечивает его запись , в блок 4 оперативной памяти .

После записи поступившего байта информации управляющее слово, содер10

15

20

25

51390820

ащее признаки информации Б модифи- ированный счетчик байтов, записы- ается в блок 4 под управлением бло а 8 приема управляющей информации, а в блок 1 приема информации выдается сигнал разрешения на следующий цикл сканирования запро-Сов, также сбрасывающий триггер 29. Узел . 10 сравнения признаков осуществляет вы- явление признака Конец передачи либо переполнение счетчика байтов, указывающего на полное заполнение страницы, В случае возникновения любого из этих сигналов по сигналу из узла 10 узел 12 записи заголовка обеспечивает формирование сигналов ля записи заголовка страницы в блок 4 оперативной памяти. На адресные шины блока 4 подается начальный адес занятой страницы, .находярщйся в блоке 8 вьщеления управляющих сигналов, а на информационные шины - номер источника, содержимое счетчика байтов и отличительные признаки сопровождения информации. Адрес сформированной стран1П,ы записывается в блок 4, . i

После записи заголовка из блока 7 анализа признаков в блок 2 поступает сигнал о записи в очередь адреса сформированной страницы, который через узел 15 переписывается в регистр 20 адреса конца очереди выдаваемых страниц.

Таким образом, в регистре 18 формируется адрес первой свободной страницы данного участка информации, в регистре 10 - адрес первой выдаваемой страницы, а в регистре 20 - адрес Q конца очереди сформированных страниц.

После записи в очередь на выдачу адреса готовой страницы информация УС в блоке 8 обнуляется по адресу последнего номера источника. При этом в блок 1 (триггер 29) из блока 7 (узел 9) поступает сигнал разрешения на опрос следуюо его источника. Конец обработки запТроса от источника в блоке 7 определяет дальнейшую проверку наличия запроса от блока 5 . вьщачи информации и признака готовности страницы.

В случае выполнения обоих условий узел 21 анализа запросов обеспечивает формирование последовательности сигналов для обращения к блоку 4 оперативной памяти и записи слова содержимого страницы в буферньй ре30

35

45

50

55

0

5

0

5

Q

0

5

5

0

5

гистр 24 блока 5, а также последующей модификации адреса. Затем блок 7 снова проверяет наличие запроса от блока 1 и при отсутствии запроса блока 5 выдачи информации или его занятости взаимодействием с устройством приема информации сразу переходит к обработке запроса от источника информации.

По окончании выдачи страницы информации из блока 7 анализа признаков поступает сигнал Конец страницы, и в ответ на это блок 5 снимает свой запрос. Коммутатор 22 обеспечивает формирование сигналов для побайтной выдачи информации путем адресации блока 4 через регистр 23 и первый коммутатор 3.

Формула изобретения I

Устройство для выбора и переадресации каналов, содержащее блок приема информации, первый и второй выходы которого соединены соответственно с первыми входами первого и второго коммутаторов, причем выход первого коммутатора подключен к адресным входам блока .оперативной памяти, выход которого соединен с первым входом блока выделения управляющих сигналов, отличающееся тем, что, с целью повышения скорости выборки каналрв и снижения объема оперативной памяти, приходящейся на один выбранный канал, в него введены блок динамического распределения памяти, первый выход которого соединен с вторым входом блока вьщеления управляющих сигналов, блок анализа признаков и блок вьщачи информации, причем второй выход блока динамического распределения памяти через первый коммутатор соединен с его вторьм входом, а третий выход блока динамического распределения памяти соединен с первым входом блока анализа признаков, второй, третий, четвертый, пятый и шестой выходы которого подключены соответственно к первому входу блока динамического распределения памяти, первому входу блока приема информации, управляющим входам первого и второго коммутаторов, первому входу блока выдачи информации, вторые входы которого соединены с выходом блока оперативной памяти, информационные входы которого подключены к выходам второго коммутатора, третьи входы которого соединены с первыми выходами блока выделения управляющих сигналов, вторые и третьи выходы которого соединены соответственно с вторыми входами блока анализа признаков и третьими входами первого

itiSnoiail из1лмл9 . 8бмн1 азтонаг азвмиаУ

ф г

f

3

TI

ж

It

« «

г ф f

п

6 аяонЗ д SaoKS dSnox eS/isK

коммутатора, четвертые входы которого подключены к первым выходам блока вьщачи информации, вторые выходы которого подключены к третьим входам блока анализа признаков, четвертые входы которого соединены с третьими выходами блока приема информации.

10

и

Змятоетр.

Яонец треЗачи

шеи

п

Snox eS/isK

в

BSaan

его ФпЛ

из SflOHu3

м.

21

22

п

Л

в Ьлон7 дыкод ycmpoac/nSa e$yjo/f3 фиъМ

Редактор А.Шандор

Составитель В.Паницкий

Техред М.ХоданичКорректор М. Максимишинец

J

О

гз

. г f о

Фив.5

Д|7 «/игД«7

| Способ изготовления литий-марганцево-висмутовых низкокоэрцитивных ферритов с прямоугольной петлей гистерезиса | 1983 |

|

SU1177056A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-04-23—Публикация

1986-11-06—Подача