сл

со со

tsD СЛ

1

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессоров в однородную вы- чис.и1те.1ьную структуру (ОВС).

He.ibKj изобретения является рас1нирение функциона,1ьны.х возможностей устройства путем сопряжения нроцессоров с различными ск()|)остями работы и обеспечения анализа информационной напряженности данной вегви .тите.11)Пой системы.

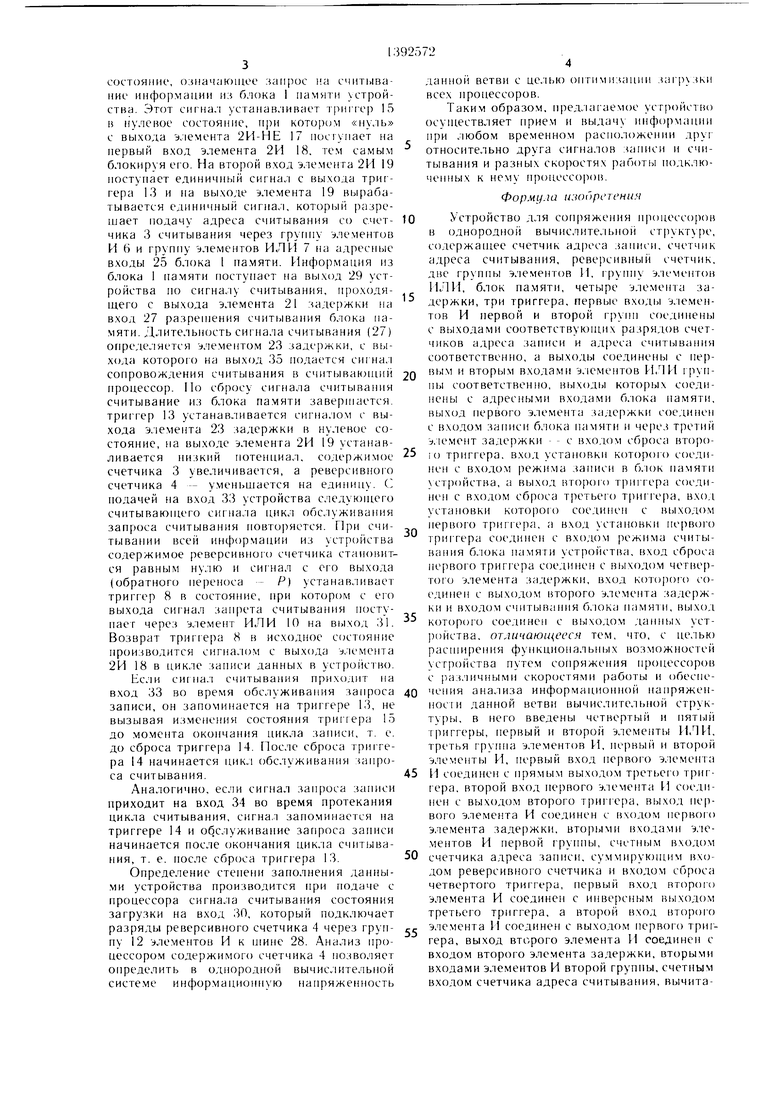

Па чертеже показана структурная схема усгройства.

Уст)ойство содержит блок I памяти, счетчик 2 адреса записи, счетчик 3 адреса считывания, реверсивный счетчик 4, э.темент И 5 nepiioii рунны, элементы И 6 второй I pyriribi, элементы ИЛИ 7 грунпы, четвертый триггер 8, пятый триггер 9, первый элемергг ИЛИ И), второй элемент ИЛИ 11, элемент И 12 третьей группы, первый триггер 13, вгорой триггер 14, третий триггер 15, первый : лемент И-НЕ 16, второй элемент И-НН 17, первый элемент И 18. второй элемент И 19, nepBbn i 20, второй 21, третий 22 и четвер- т1)1Й 23 элементы задержки соответственно, информационный 24 и адресный 25 входы блока памяти, вход 26 записи блока памяти, вход 27 считывания б;юка намяти, вход/выход 28 данных устройства, выход 29 данных устройства, вход 30 считывания состояния загрузки устройства, выход 31 .ча запрета считывания ует юйства, выход 32 сигнала занрета записи данных устройства, вход 33 CHi na. ia считывания данных устройства, вход 34 сигна.та записи данных в устройство, выход ,35 сигнала сопровождения считываемых данных, выход 36 сишала подтверждения записи.

стр()йство работает следующим образом.

В исходном состоянии счетчики 2 заниси, 3 считывания и реверсивный счетчик 4 находятся в нулевом состоянии, на разрядах адресного входа 25 блока 1 памяти присутствует потенциал, соответствующий «О, на разрядах выхода 29 данных блока памяти и выходах элементов 12 третьей И гругшы ноддерживается высокоимпедансное состояние, на выходе 32 запрета записи присутствует потенциал разреншющего сигнала, на выходе 31 сигнала запрета считывания поддерживается потенциал запреп;аюш,е1-о сигнала.

Выдача адресов записи и считывания со счетчиков 2 и 3 через схемы ИЛИ 7 группы на адресный вход 25 блокируется схемами 5 и 6 элементов И первой и второй групп, на вторые входы которых поступают нулевые управляющие сигналы с выходов элементов И 18 и 19.

Триггеры 13 и 14 установлены в нулевое состояние и с их выходов на входы схем 2И-НЕ 16 и 17 и на вторые входы схем 2И 18 и 19 поступают нулевые потециалы, б;1оки- руя их.

Процесс записи или считывания данных в устройство начинается с анализа занисы

2

вающим данные процессором (или считывающим данные процессором) состояния сигнальных выходов: 31 - запрета считывания или 32 запрета записи. В исходном состоянии разрешается только запись данных

в устройство. Записывающий данные процессор помещает данные на вход/выход 28 данных и вырабатывает команду записи на входе 34, которая устанавливает триггер 14 в единичное состояние, означающее за10 прос на запись информации в блок 1 памяти устройства. Запрос на запись высоким по- генциалом поступает на вход установки триг- 1 ера 15 и второй вход элемента 2И 18, в то же время с выхода триггера 13 не выдается сигнал заироса на считывание и на первом

5 выходе триггера 15, таким образом, присутствует высокий потенциал, что вызывает появление высокого потенциала на выходе элемента 2И 18, Этот потенциал поступает па вторые входы элементов 5 нервой групQ пы И, пропуская на выходы 25 через группу элементов ИЛИ 7 нулевой адрес с выходов счетчика 2 записи, и вырабатывает на выходе эле.мента 20 задержки сигнал (26), управляющий записью данных в нулевую ячейку блока 1 памяти. Происходит запись дан5 ных в блок 1 памяти, а сигнал с выхода элемента 20 проходит элемеит 22 задержки и поступает на вход сброса триггера 14, устанавливая его опять в нулевое состояние. При этом с выхода элемента 18 снимается высокий потенциал уг1равляюн1его сигнала,

30 вызывая переход состояний счетчиков 2 записи и 4 реверсивного 4 к следуюн1ему значению адреса и установку триггера 8 в состояние, которое соответствует снятию сигнала запрета считывания с его выхода и выхода 31, на который сигнал проходит через

35 схему ИЛИ 10. На этом цикл записи заканчивается. Во время каждого цикла заниси на выходе 31 поддерживается сигнал запрета считывания. (Следующие циклы записи происходят аналогично, вызывая увеличение

4Q содержимого счетчиков 2 и 4. Окончание каждого цикла заииси сопровождается со стороны устройства сигналом (36) «Подтверждение заниси.

При переполнении памяти устройства С выхода прямого переноса реверсивного

45 счетчика выдается сигнал, устанавливающий триггер 9 в единичное состояние, соответствующее выдаче через элемент ИЛИ 1 1 на выход 32 сигнала «Запрет записи. Снятие сигнала «Запрет записи происходит при осуществлении цикла считывания,

50 когда сигнал с выхода элемента 19 возвращает трип ер 9 в нулевое состояние.

1Дикл считывания начинается с анализа считывающим нроцессором состояния сигнала (32) «Запрет считывания. При отсутствии сигнала «Запрет считывания нроцессор

вырабатывает сигнал «Считывание (33), который, проходя через элемент ИЛИ 11 на выход 32, устанавливает сигнал «Запрет записи и переводит триггер 13 в единичное

состояние, означающее запрос на считывание информации из блока 1 памяти устройства. Этот сигна. устанав.чивает трИ|-|-ер 15 к нулевое состояние, при KOTOpcjM «нуль с выхода элемента 2И-НЕ 17 поступает па первый вход элемента 2И 18. тем самым блокируя его. На второй вход элемента 2И 19 поступает единичный сигнал с выхода триг - гера 13 и па выходе элемента 19 вырабатывается едиппчный сигнал, который разрешает нодачу адреса считывания со счетчика 3 считывания через группу элементов И 6 и группу элементов ИЛИ 7 на адресные входы 25 блока I памяти. Информация из блока 1 памяти поступает па выход 29 устройства по сигналу считывания, проходящего с выхода элемента 21 заде)жки на вход 27 разрен1ения считывания блока памяти. Длительность сигнала считывания (27) определяется элементом 23 задержки, с выхода которого на выход 35 подается сшпал сопровождения считывания в считывающий процессор. Но сбросу сигнала считывания считывание из блока памяти завершается. три1тер 13 устанавливается сигналом с выхода э.лемента 23 задержки в нулевое состояние, на выходе элемента 2И 19 устанавливается низкий потенциал, содержимое счетчика 3 увеличивается, а реверсивно1 о счетчика 4 - у.меньшается на единицу. С подачей на вход 33 устройства следующего считываюн1его сигнала цикл обслуживания запроса считывания повторяется. При считывании всей информации из устройства содержимое реверсивного счетчика становится равным нулю и сигнал с его выхода (обратного переноса - Р) устанавливает тригг ер 8 в состояние, при котором с его выхода сигнал запрета считывания поступает через элемент ИЛИ 10 на выход 31. Возврат триггера 8 в исходное состояние производится сигна,;1()м с выхода элемента 2И 18 в цикле записи данных в устройство.

Если си(нал считывания приходит на вход 33 во время обслуживания запроса записи, он запоминается па триггере 13, пе вызывая изменении состояния триггера 15 до момента окончания цикла загщси, т. е. до сброса триггера 14. После сброса триггера 14 начинается цикл обслуживания запроса считывания.

Аналогично, если сигнал запроса записи приходит на вход 34 во время протекания цикла считывания, сигнал запоминается на триггере 14 и обслуживание запроса записи начинается после окончания цикла считывания, т. е. после сброса триггера 13.

Определение степени заполнения данными устройства производится нри подаче с процессора сигнала считывания состояния загрузки на вход 30, который подключает разряды реверсивного счетчика 4 через группу 12 элемептов И к типе 28. Анализ процессором содержимого счетчика 4 позволяет определить в одпородпой вычислительрюй системе информационную напряженность

0

5

0

5

0

5

0

5

0

5

данной ветви с целью оптимизации загрузки всех процессоров.

Таким образом, предлагаемое устройство осуществляет прием и выдачу информации при любом временном расположении друг относительно друга сигналов занпси и считывания и разных скоростях работы подключенных к нему nponcccopoLi.

Формула изобретения

Устройство для соп()яжепия nponeccojioB в однородной вычислительной структу н содержап1ее счетчик адреса записи, счетчик адреса считывапия, реверсивный счетчик, дне группы элементов И, rpyiniy э, 1ементов ИЛИ, блок па.мяти, четыре эле.мента задержки, три триггера, первые входы элементов И первой и второй групп соединены с выходами соответствующих разрядов счетчиков адреса записи и адреса считывания соответственно, а выходы соединены е первым и вторым входами э,1ементов ИЛИ группы соответствепно, вьгходы которых соединены с адресными входами б. юка памяти, выход первого элемепта задержки соедипеп с входом записи блока памяти и через третий э,1емепт задержки - - с входом сброса второ- io триггера, вход установки которого соединен с входом режима записи в блок памяти устройства, а выход второго триггера соединен с входом сброса третьего т()иггера, вход установки которого соединен с выходом иервого триггера, а вход установки нерво|-о триггера соединен с входом режима считывания блока памяти устройства, вход сброса первого триггера соединен с выходом четвер- TOi o элемента задержки, вход которого соединен с выходом второго э,темента задержки и входом считываиия блока памяпи, выход которого соединен с в|11ходом данных устройства, отличающееся тем, что, с це, 1ью расширения функциона,пьных возможностей устройства путем сопряжения процессоров с юз.чичными скоростями работы и обеспечения анализа информационной папряжеп- НОС1И данной ветви вычислительной структуры, в него введены четвертый и пяты11 триггеры, первый и второй элементы ИЛИ, третья группа элемептов И, первы(1 и BTOpoii элементы И, первый вход первого элемепта И соединен с прямым выходом третьего триг- г ера, второй вход первого элемента И соеди- HeFi с выходом второго три1тера, выход первого э,пемента И соединен с входом иервогч) элемента задержки, вторыми входами э.че- .ментов И первой гругшы, счетпым входом счетчика адреса записи, суммирующим входом реверсивного счетчика и входом сброса четвертого триггера, первый вход элемента И соединен с инверсным выходом третьего триггера, а второй вход второго элемента И соединен с выходом первого триггера, выход второго элемента И соединен с входом второго элемента задержки, вторыми входами элементов И второй группы, счетпым входом счетчика адреса считывания, вычитающим входом реверсивного счетчика и входом сброса пятого триггера, вход установки которого соединен с выходом положительного переполнения реверсивного счетчика, выход пятого триггера соедииен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого триггера, выход второго элемента ИЛИ соединен с выходом сигнала запрещения записи данных устройства, вход установки четвертого триггера соединен с выходом заема реверсивного счетчика, выход четвертого триггера соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, выход первого элемента

ИЛИ является выходом сигнала запрещения считывания данных устройства, информационные выходы реверсивного счетчика соединены с вторыми входами элементов И третьей группы, первые входы которых соединены с входом сигнала считывания состояния загрузки устройства, выходы элементов И третьей группы соединены с входом/ /выходом данных устройства и информационным входом блока памяти, выход третьего элемента задержки соединен с выходом сигнала подтверждения записи данных устройства, выход четвертого элемента задержки является выходом сигнала сопровождения считываемых данных устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров в распределенную вычислительную систему | 1989 |

|

SU1661781A1 |

| Устройство для контроля программ | 1985 |

|

SU1251128A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для измерения среднеквадратического значения сигнала | 1989 |

|

SU1728808A1 |

| Запоминающее устройство | 1986 |

|

SU1437915A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для сопряжения разноскоростных вычислительных устройств | 1991 |

|

SU1789986A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессоров в однородную вычислительную структуру. Целью изобретения является расширение функциональных возможностей устройства за счет сопряжения процессоров с различными скоростями работы и анализа информационной напряженности данной ветви вычислительной системы. Для этого в устройство, содержащее счетчики 2 и 3 адреса записи и считывания соответственно, реверсивный счетчик 4, блок I памяти, группы эле.ментов ИЛИ 7 и И 5, 6, элементы задержки 20-23, элементы И 18, 19, триггеры 13, 14, 15, дополнительно введены два триггера 8, 9, два элемента ИЛИ 10 II, группа элементов И 12. I ил.

| Устройство для ввода информации | 1981 |

|

SU989555A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-30—Публикация

1986-12-24—Подача