(21)4П9092/24-24

(22)23.07.86

(46) 15.11.Й8. Бюп. № 42 (72) А.Д.Жучков, В.И.Косов, Б.Б.Кугутов, О.В.Росницкий, А.И.Савельев и З.А.Чумакова

(53)681.327.066 (088.8)

(56)Авторское свидетельство СССР № 705901, кл. G II С 7/00-, 1982.

Авторское свидетельство СССР № 780035, кл. G 11 С 7/00, 1982.

(54)ЗАПОМИНАЮ11ЩЕ УСТРОЙСТВО

(57)Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам, и может быть использовано в качестве динамического блока памяти при работе различных внешних устройств (ЭВМ, процессоры) . Цель изобретения - повышение быстродействия устройства и расширение области применения за счет возможности осуществления его работы с внетчними устройствами с передачей

информации в обоих направлениях - достигается введега1ем элементов И, ИЛИ, триггеров, блоков сопряжения, адресного селектора, селектора входных данных, мультиплексора и блока задержки. С инверсного выхода триггеров осуществляется запрет на прохождение информации с элементов И 13, 15, в результате чего блокируется обращение к запоминающему устройству любых внешних устройств и блокируется регенерация информации в блоке 1 памяти. По окончании процесса записи сигнал с одного из выходов блока 12 задержки устанавливает триггер 6 в нулевое состояние и на выходы элементов И 13 и 15 подается разрешающий потенциал, в результате чего начинается регенерация информации. Регенерация информации в блоке 1 памяти осуществляется в промежутках между обращениями к предложенному устройству. 1 ил.

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1481854A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1411760A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1474739A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

фь оо

со

сд

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использов о в качестве динамического блока памяти при работе различных внешних устройств (ЭВМ, процессоры).

Целью изобретения является повышение быстродействия устройства и расширение области его применения за счет возможности осуществления работы с внешними устройствами с передачей информации в обоих направлениях,

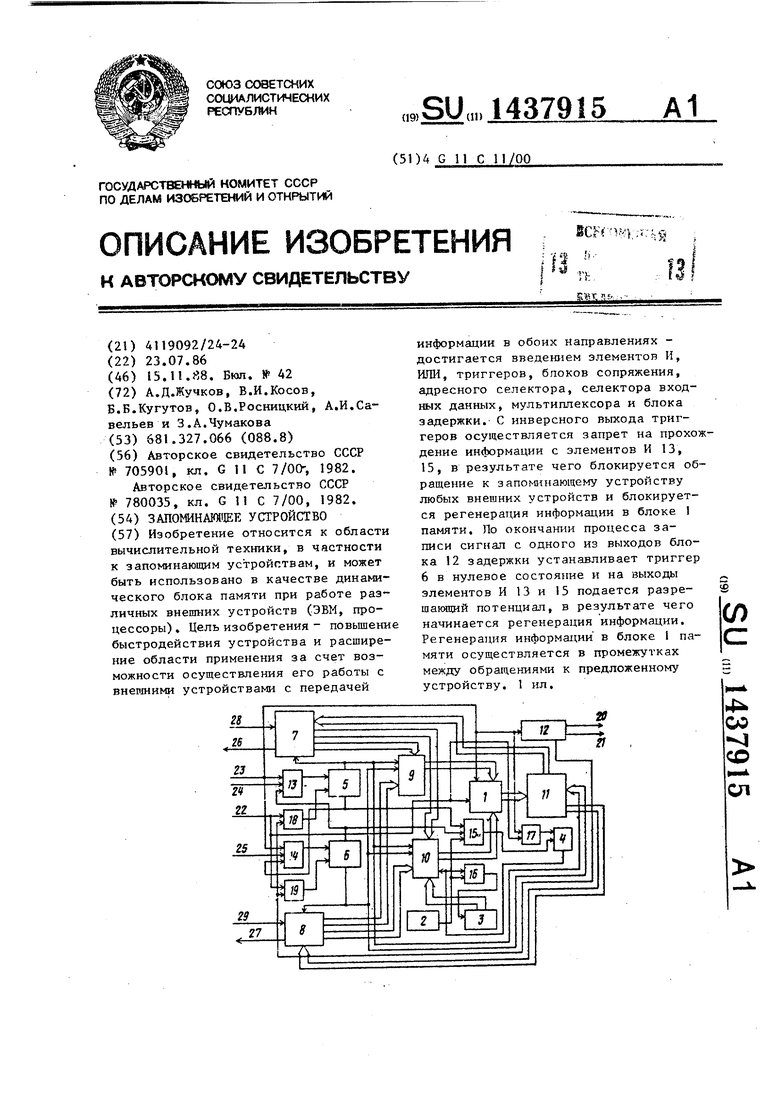

На чертеже изображена функциональ- 15 ная схема предложенного устройства.

Запоминающее устройство содержит блок 1 памяти, генератор 2 тактовых импульсов , счетчик 3 строк, триггеры

10

элемента ШШ 17, выходной сигнал которого фиксирует нулевое состояние триггера 4. По окончании процесса записи сигнал с одного из выходов блока 12 устанавливает триггер 6 в нулевое состояние, в результате чего на входы элементов И 13 и 15 подается, разрешающий потенциал,

В режиме считывания на вход 29 поступает только код адреса, а считанный код адреса по разрешению тригге ра 6 через мультиплексор 11 подается на блок 8 и далее на выход 27,

Одновременно с передачей кода считанного слова с блока 12 подается сигнал Сопровождение 1, обеспечивающий работу ;: приемных блоков внешнего процессора. Сразу после окончания

4,5,6, блоки 7 и 8 сопряжения, сепек- 20 работы формирующих и усиливающих схем тор 9 входных данных, адресньй себлока 1 памяти после установки триггера 6 в нулевое состояние начинается работа блоков регенерации. Импульс с генератора 2 устанавливает триггер 4 в единичное состояние, и через элемент И 16 начинается счет адресов регенерируемых строк на счетчике 3, Адреса строк через селектор 10 адреса по разрешаю1геь4у потенциалу с триггера 6 подаются в блок 1 памяти, обеспечивая регенерацию информации в блоке 1 памяти. При каждом новом обращении регенерация прерывается, обеспечивая сохранность последнего регенерируемого адреса.

лектор 10, мультиплексор П, блок 12 задержки, элементы И 13-16, элементы ИЛИ 17, 18 и 19, управлякадие внешними устройствами и процессором, выходы 20 и 21 устройства, вход 22 сброса устройства, вход 23 записи- считывания устройства, входы 24 и 25 разрешетя занесения информации, информационные выходы 26 и 27 устройст- ва, информационные.вхоДы 28 и 29 устройства.

Устройство работает следующим образом.

Перед началом работы происходит установка в нуль триггеров 4,5,6 блока 1 памяти. При наличии сигналов записи и разрешения занесения информаци на входах элемента И 14 на его выходе появляется импульс, который устанавливает триггер 6 н единичное состояние (триггер 5 находится в нулевом состоянии и с его инверсного вьйсода поступает разрешающий сигнал на один из входов элемента И 14). С инверсного выхода триггера 6 осуществляется запрет на прохождение информации с выхода элемента И 13 и с выхода элемента И 15, в результате чего блокируется обращение к запоминающему устройству любых внешних устройств и блокируется регенерация информации в блоке 1 памяти. При появлении сигнала на входе 23 осуществляется запись в блоке 1 поступившего слова и происходит запуск блока 12 задержки, С целью исключения несанкционированной регенерации информации сигнал с входа 23 поступает на один из входов

5

элемента ШШ 17, выходной сигнал которого фиксирует нулевое состояние триггера 4. По окончании процесса записи сигнал с одного из выходов блока 12 устанавливает триггер 6 в нулевое состояние, в результате чего на входы элементов И 13 и 15 подается, разрешающий потенциал,

В режиме считывания на вход 29 поступает только код адреса, а считанный код адреса по разрешению триггера 6 через мультиплексор 11 подается на блок 8 и далее на выход 27,

Одновременно с передачей кода считанного слова с блока 12 подается сигнал Сопровождение 1, обеспечивающий работу ;: приемных блоков внешнего процессора. Сразу после окончания

0 работы формирующих и усиливающих схем

5 О

5

0

5

0

5

блока 1 памяти после установки триггера 6 в нулевое состояние начинается работа блоков регенерации. Импульс с генератора 2 устанавливает триггер 4 в единичное состояние, и через элемент И 16 начинается счет адресов регенерируемых строк на счетчике 3, Адреса строк через селектор 10 адреса по разрешаю1геь4у потенциалу с триггера 6 подаются в блок 1 памяти, обеспечивая регенерацию информации в блоке 1 памяти. При каждом новом обращении регенерация прерывается, обеспечивая сохранность последнего регенерируемого адреса.

Обращение от периферийных устройств производится аналогичным образом, только подается разреша1едий потенциал внешнее устройство на вход 24, который позволяет сигналу Запись проходить через элемент И 13 на триггер 5. Сигнал с инверсного выхода триггера 5 блокирует при этом работу элементов И 14 и 15. С блока 12 задержки выдается сигнал Сопровождение 2 информации внешнего устройства.

При таких режимах работы обеспечивается регенерация информации как в промежутках между обращениями, так и при отсутствии обращений к запоминающему устройству, а также надежная асинхронная работа внешних устройств и процессоров с запоминающим устройст-- вом,

Введение в предложенное устройство новых элементов и блоков позволило увеличить его быстродействие за счет осуществления регенерации инфорнации в блоке памяти в промежутках записи (обращения) и расширить область примр.нения устройства за счет его работы с внешними (периферийными) устройствами с оперативным переключением потоков информации к внешним устройствам различного типа в .прямом и обратном направлениях,

Формула изобретения

Запоминающее устройство, содержащее блок памяти, вход установки нуля которого является входом сброса устройства, генератор тактовых импуль- сов и счетчик строк, отличающееся тем, что, с целью повьше- ния быстродействия устройства и расширения области его применения за счет возможности осуществления работы с внешними устройствами с передачей информации в обоих направлениях, в него введены элементы И, ИЛИ, триггеры, блоки сопряжения, адресный селектор, селектор входных данных, мульти- плексор и блок задержки, п ервый и второй выходы которого являются выходами устройства, вход блока задержки является входом разрешения записи-считывания информации устройства и соединен с первыми входами первого и второго элементов И, с входом разрешения записи-считывания информации блока памяти, и с первым входом первого элемента ИЛИ, второй вход первого элемен- та ИЛИ соединен с входом установки нуля блока памяти, выход которого соединен с информационным входом мультиплексора, информационный и адресный входы блока памяти соединены с выходами селектора входных данных и адресного селектора соответственно выход блока задержки соединен с первыми входами второго и третьего элементов ИЛИ, вторые входы которых сое- динены с вторым входом первого элемента ИЛИ, выход первого элемента ИЛИ соединен с входом установки нуля первого триггера, вход установки единицы которого соединен с выходом третьего элемента И, выход первого триггера соединен с первым входом четвертого элемента И и с первым

входом разрешеушя приема информации адресного селектора, выход генератора тактовых импульсов соединен с пер- пым входом третьего элемента И и вторым входом четвертого элемента И, выход которого соединен с информационным входом счетчика строк, первая и вторая группы информационных входов адресного селектора соединены с первыми группами информационных выходов первого и второго блоков сопряжения, вторые группы информационных выходов которых соединены с информационными входами селектора входных данных, выход счетчика строк соединен с третьим входом адресного селектора, вторые входы первого и второго элементов И являются входами разрешения записи информации устройства, выход первого элемента И соединен с входом установки едини1у 1 второго триггера, вход установки нуля которого соединен с выходом второго элемента ИЛИ, прямой выход, второго триггера соединен с входом разрешения приема информации первого блока сопряжения, с первыми входами разрешения приема информации селектора входных данных, адресного селектора и мультиплексора, инверсшлй выход второго триггера соединен с третьим входом второго элемента, И и вторым входом третьего элемента И, выход второго элемента И соединен с входом установки единицы третьего триггера, вход установки нуля которого соединен с выходом третьего элемента ИЛИ, инверсный выход третьего триггера соединен с третьими входами первого и третьего элементов И, прямой выход третьего триггера соединен с входом разрешения приема информации второго блока сопряжения, вторыми входами разрешения приема информации селектора входных данных адресного селектора и мультигшексора, выходы которого соединены с информационными входами бло,ков сопряжения, группы третьих информационных выходов которых являются выходами устройства, информационные входы блоков сопряжения являются информационными входами устройства.

Авторы

Даты

1988-11-15—Публикация

1986-07-23—Подача