Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных сетей.

Цель изобретения - повышение производительности системы путем совмещения процессов записи данных в устройство сопряжения и передачи их по каналам связи.

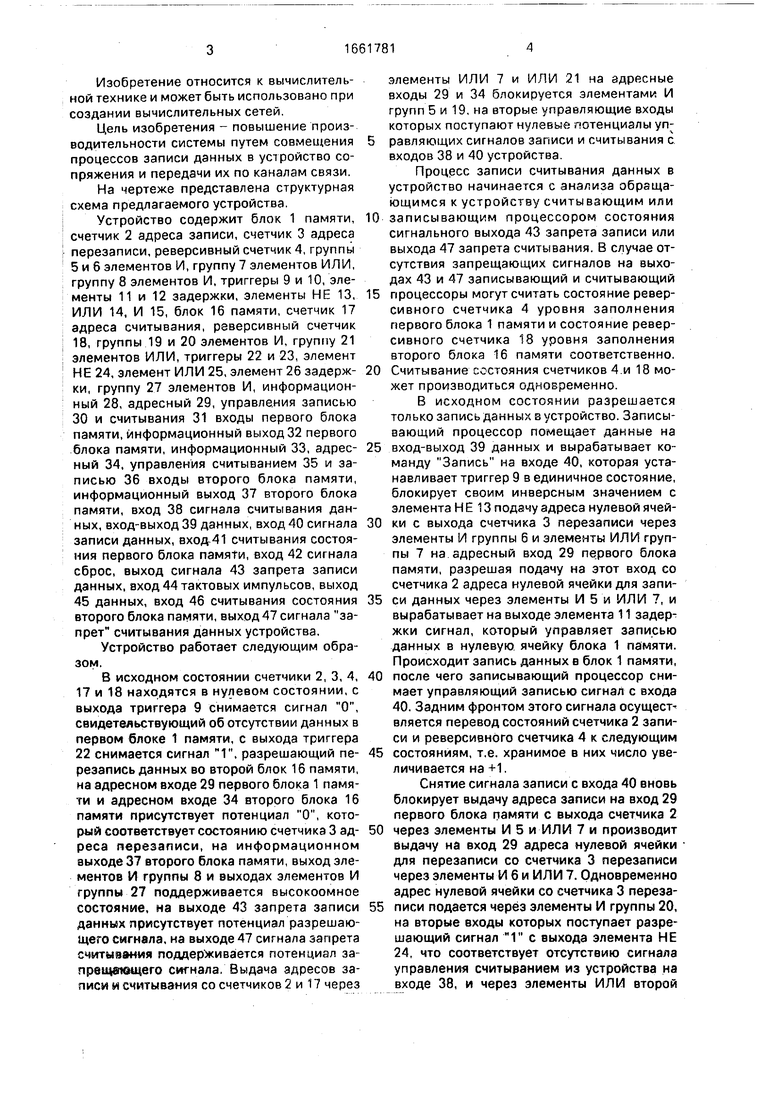

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит блок 1 памяти, счетчик 2 адреса записи, счетчик 3 адреса перезаписи, реверсивный счетчик 4, группы 5 и 6 элементов И, группу 7 элементов ИЛИ, группу 8 элементов И, триггеры 9 и 10, элементы 11 и 12 задержки, элементы НЕ 13, ИЛИ 14, И 15, блок 16 памяти, счетчик 17 адреса считывания, реверсивный счетчик 18, группы 19 и 20 элементов И, группу 21 элементов ИЛИ, триггеры 22 и 23, элемент НЕ 24, элемент ИЛИ 25, элемент 26 задержки, группу 27 элементов И, информационный 28, адресный 29, управления записью 30 и считывания 31 входы первого блока памяти, информационный выход 32 первого блока памяти, информационный 33, адресный 34, управления считыванием 35 и записью 36 входы второго блока памяти, информационный выход 37 второго блока памяти, вход 38 сигнала считывания данных, вход-выход 39 данных, вход 40 сигнала записи данных, вход-41 считывания состояния первого блока памяти, вход 42 сигнала сброс, выход сигнала 43 запрета записи данных, вход 44 тактовых импульсов, выход 45 данных, вход 46 считывания состояния второго блока памяти, выход 47 сигнала запрет считывания данных устройства.

Устройство работает следующим образом.

В исходном состоянии счетчики 2, 3, 4, 17 и 18 находятся в нулевом состоянии, с выхода триггера 9 снимается сигнал О, свидетельствующий об отсутствии данных в первом блоке 1 памяти, с выхода триггера 22 снимается сигнал 1, разрешающий перезапись данных во второй блок 16 памяти, на адресном входе 29 первого блока 1 памяти и адресном входе 34 второго блока 16 памяти присутствует потенциал О, который соответствует состоянию счетчика 3 адреса перезаписи, на информационном выходе 37 второго блока памяти, выход элементов И группы 8 и выходах элементов И группы 27 поддерживается высокоомное состояние, на выходе 43 запрета записи данных присутствует потенциал разрешающего сигнала, на выходе 47 сигнала запрета считывания поддерживается потенциал запрещающего сигнала, Выдача адресов записи и считывания со счетчиков 2 и 17 через

элементы ИЛИ 7 и ИЛИ 21 на адресные входы 29 и 34 блокируется элементами И групп 5 и 19, на вторые управляющие входы которых поступают нулевые потенциалы управляющих сигналов записи и считывания с входов 38 и 40 устройства.

Процесс записи считывания данных в устройство начинается с анализа обращающимся к устройству считывающим или

0 записывающим процессором состояния сигнального выхода 43 запрета записи или выхода 47 запрета считывания. В случае отсутствия запрещающих сигналов на выходах 43 и 47 записывающий и считывающий

5 процессоры могут считать состояние реверсивного счетчика 4 уровня заполнения первого блока 1 памяти и состояние реверсивного счетчика 18 уровня заполнения второго блока 16 памяти соответственно.

0 Считывание состояния счетчиков 4 и 18 может производиться одновременно.

В исходном состоянии разрешается только запись данных в устройство. Записывающий процессор помещает данные на

5 вход-выход 39 данных и вырабатывает команду Запись на входе 40, которая устанавливает триггер 9 в единичное состояние, блокирует своим инверсным значением с элемента Н Е 13 подачу адреса нулевой ячей0 ки с выхода счетчика 3 перезаписи через элементы И группы 6 и элементы ИЛИ группы 7 на адресный вход 29 первого блока памяти, разрешая подачу на этот вход со счетчика 2 адреса нулевой ячейки для запи5 си данных через элементы И 5 и ИЛИ 7, и вырабатывает на выходе элемента 11 задержки сигнал, который управляет записью данных в нулевую ячейку блока 1 памяти. Происходит запись данных в блок 1 памяти,

0 после чего записывающий процессор снимает управляющий записью сигнал с входа 40. Задним фронтом этого сигнала осущест вляется перевод состояний счетчика 2 записи и реверсивного счетчика 4 к следующим

5 состояниям, т.е. хранимое в них число увеличивается на +1.

Снятие сигнала записи с входа 40 вновь блокирует выдачу адреса записи на вход 29 первого блока памяти с выхода счетчика 2

0 через элементы И 5 и ИЛИ 7 и производит выдачу на вход 29 адреса нулевой ячейки для перезаписи со счетчика 3 перезаписи через элементы И б и ИЛИ 7. Одновременно адрес нулевой ячейки со счетчика 3 переза5 писи подается через элементы И группы 20, на вторые входы которых поступает разрешающий сигнал 1 с выхода элемента НЕ 24, что соответствует отсутствию сигнала управления считыванием из устройства на входе 38, и через элементы ИЛИ второй

группы 21 не адресный вход 34 второго блока 16 памяти. Выдача адреса считывания со счетчика 17 заблокирована сигналом О на входах элементов И группы 19. На всех входах элемента И 15, кроме входа тактово- го сигнала с входа 44, подают сигналы 1. Устройство подготовлено для осуществления перезаписи информационного слова из блока 1 памяти в блок 16 памяти, которая происходит с приходом значения 1 такто- вого импульса.

С появлением значения 1 тактового импульса на выходе элемента И 15 вырабатывается единичный сигнал, который поступает через элемент 12 задержки на вход 31 управления считыванием первого блока 1 памяти и вход 36 управления записью второго блока 16 памяти и осуществляет перезапись содержимого нулевой ячейки блока 1 памяти в нулевую ячейку блока 16 памяти, Задним фронтом сигнала с элемента И 15 после поступления уровня О сигнала тактового импульса 44 производится перевод состояния счетчика 3 перезаписи в следующее: соответствующее адресу первой ячей- ки памяти значение первого реверсивного счетчика 4 возвращается к предыдущему - нулевому, а сигнал с его выхода устанавливает триггер 9 в нулевое состояние, и сигнал О с выхода триггера 9 блокирует работу элемента И 15 при переходе очередных тактовых импульсов. Задний фронт сигнала с элемента И 15 также переводит второй реверсивный счетчик 18 в следующее состояние и производит установку триггера 23 в состояние, при котором с его выхода на выход 47 устройства поступает сигнал с потенциалом, разрешающим считывание данных. На этом цикл записи и перезаписи оканчивается. В дальнейшем, при отсутствии счи- тывания данных из устройства, циклы записи и перезаписи будут происходить в последовательности, аналогичной рассмотренной ранее, до состояния полного заполнения второго блока 16 памяти, что фиксируется переполнением реверсивного счетчика 18 и появлением на его выходе сигнала, который устанавливает триггер 22 в нулевое состояние. Нулевой сигнал с выхода триггера 22 блокирует дальнейшую вы- работку управляющих перезаписью сигналов с элемента И 15 и перезапись данных из блока 1 записи в блок 16 памяти прекращается.

После заполнения последней свобод- ной- ячейки первого блока 1 памяти происходит переполнение первого реверсивного счетчика 4 и на его выходе появляется единичный сигнал, который устанавливает второй триггер 10 в состояние, соответствующее выдаче не выход 43 сигнала запрета записи данных в устройство. С этого момента устройство закрыто для записи данных и находится в состоянии ожидания режима считывания, Снятие сигнала запрета записи с выхода 43 ПРОИСХОДИТ при осуществлении цикла считывания и перезаписи или прихода сигнала 42 сброса.

Цикл считывания данных из устройства начинается с анализа состояния сигнала 47 запрета считывания и анализа степени заполнения второго блока 16 памяти, которая отражается состоянием реверсивного счетчика 18. Рассмотрение работы устройства в режиме выхода данных в считывающий процессор производится при условии отсутствия циклов записи данных в устройство и состояния полного заполнения устройства данными.

После анализа состояния сигнала на выходе 47 на вход 38 считывания подается сигнал управления считыванием, который разрешает подключение адреса первой ячейки для считывания, хранящегося на счетчике адреса 17 считывания, через элементы И 19 и ИЛИ 21 к адресному входу 34 второго блока 16 памяти и блокирует на элементах И 20 адрес перезаписи со счетчика 3. Сигнал 38 считывания подается через элемент 26 задержки на вход 35 управления считыванием второго блока 16 памяти после установления адреса 34 считывания, и на выходе 37 второго блока 16 памяти появляется содержимое адресуемой ячейки памяти, которое поступает на выход 45 данных устройства и считывается запрашивающим процессором. Снятие сигнала -38 считывания вызывает переход реверсивного счетчика 18 в предыдущее состояние (хранимое в нем число уменьшается на 1} и установку триггера 22 в единичное состояние через элемент ИЛИ 25, при котором Г с его выхода подается на вход элемента И 15. На других входах элемента И 15 также присутствуют единичные сигналы, которые свидетельствуют об отсутствии в данный момент циклов обращения к устройству и наличии данных в первом блоке 1 памяти, что подтверждается единичным сигналом на выходе триггера 9.

Приход на вход 44 единичного сигнала тактового импульса вызывает появление Г на выходе элемента И 15, которая поступает через линию 12 задержки на вход 31 управления считыванием первого блока 1 памяти и вход 36 управления записью второго блока 16 памяти, на адресных входах 29 и 34 которых присутствует адрес считывания и записи со счетчика 3. Происходит перезапись информационного слова из блока 1 памяти во ворой блок 16 памяти. Приход нулевого значения тактового импульса снимает единичный сигнал с выхода элемента И 15, что вызывает переход счетчика 3 перезаписи к следующему адресу, уменьшение значения реверсивного счетчика 4 на 1, установку триггера 10 в состояние, при котором на выход 43 выдается разрешающий запись потенциал, переход реверсивного счетчика 18 к следующему состоянию и выдаче с его выхода сигнала переполнения, который устанавливает триггер 22 в нулевое состояние и О с его выхода блокирует через элемент 15 дальнейшую перезапись данных. Протекание процесса перезаписи данных после считывания данных из устройства аналогично рассмотренному процессу перезаписи после записи данных в устройство.

После окончания цикла считывания данных из устройства, сопровождающегося процессом перезаписи, в блоке 1 памяти освобождается одна ячейка памяти, второй же блок 16 памяти остается полностью заполненным. Дальнейший последовательный вывод данных из устройства без записи в него приводит сначала к выводу всей информации из блока 1 памяти, обнулению реверсивного счетчика 4 и установке триггера 9 в нулевое состояние, которое блокирует осуществление дальнейшей перезаписи. Затем происходит последовательный вывод данных из второго блока 16 памяти и с выводом содержимого его последней ячейки памяти содержимое реверсивного счетчика памяти 18 становится равным нулю, а сигнал с его выхода устанавливает триггер 23 в состояние, соответствующее выдаче на выход 47 сигнала, запрещающего дальнейшее считывание данных из устройства.

В режиме одновременного обращения записывающего и считывающего процессо- ров;устройство работает следующим образом.

После анализа состояния разрешающих сигналов на выходах 43 и 47 записывающий процессор помещает данные на шину 39 и вырабатывает сигнал 40 записи, а считывающий процессор вырабатывает сигнал 38 считывания, после чего протекают процессы записи данных в первый блок 1 памяти и считывания данных из блока 16 памяти в указанной последовательности. Временное перекрытие сигналов записи и считывания в пределах одного такта может быть произвольным. Процесс перезаписи данных будет заблокирован до момента снятия сигнала управления, пришедшего последним, при равной длительности этих сигналов. Поскольку ввод данных в ОЗУ

процессора или вывод данных из процессора в устройство всегда требует несколько машинных тактов, в течение большей части которых устройство находится в состоянии

ожидания, а процесс перезаписи осуществляется за один рабочий такт, то даже при последовательной пересылке элементов массива произойдет несколько процессов перезаписи внутри устройства. Осуществление перезаписи данных в устройство во время протекания циклов ввода или вывода данных из него. т.е. осуществление вложения процесса перезаписи во временной цикл тактов, обеспечивающих запись или

считывание данных процессорами, и параллельное выполнение этих операций реализует возможность одновременной работы с устройством записывающего и считывающего процессоров, исключая их простои при

обращении к устройству.

Формула изобретения Устройство для сопряжения процессоров в распределенную вычислительную систему, содержащее блок памяти, счетчик адреса записи, счетчик адреса перезаписи, реверсивный счетчик, три группы элементов И, группу элементов ИЛИ, два триггера, два элемента задержки, причем вход сигнала

запись данных устройства соединен с первыми входами элементов И первой группы, со счетным входом счетчика адреса записи, с прямым счетным входом реверсивного счетчика, входом первого элемента задержки и входом сброса первого триггера, выходы элементов И первой группы соединены с первыми входами элементов ИЛИ группы, выходы которых соединены с входом адреса блока памяти, информационный выход счетчика адреса записи поразрядно соединен с вторыми входами элементов И первой группы, выходы элементов И второй группы соединены с вторыми входами элементов ИЛИ группы, вход сигнала считывания состояния блока памяти устройства соединен с первыми входами элементов И третьей группы, выходы которых поразрядно соединены с информационным входом блока памяти и являются входом-выходом

данных устройства, информационный выход реверсивного счетчика поразрядно соединен с вторыми входами элементов И третьей группы, прямой выход переполнения реверсивного счетчика соединён с входом установки первого триггера, инверсный выход переполнения реверсивного счетчика соединен с входом установки второго триггера, прямой выход которого является выходом сигнала запрет записи данных устройства, выход первого элемента

задержки соединен с входом управления записью блока памяти, отличающееся тем, что, с целью повышения производительности системы путем совмещения процессов записи данных в устройство сопряжения и передачи их по каналам связи, в него введены вторые блок памяти, реверсивный счетчик, группа элементов ИЛИ, три группы элементов И, два триггера, два элемента НЕ, третий элемент задержки, счетчик адреса считывания, два элемента ИЛИ. элемент И, причем вход сброса устройства соединен с первыми входами первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с входом сброса второго триггера, выход второго элемента ИЛИ соединен с входом установки третьего триггера, вход сброса которого соединен с прямым выходом переполнения второго реверсивного счетчика, прямой счетный вход которого соединен с вторым входом второго элемента ИЛИ, со счетным входом счетчика адреса считывания, с первыми входами элементов И четвертой группы, входом первого элемента НЕ, входом третьего элемента задержки и является входом сигнала считывания данных устройства, обратный счетный вход первого реверсивного счетчика соединен со счетным входом счетчика адреса перезаписи, с вторым вхо- дом первого элемента ИЛИ, с обратным счетным входом второго реверсивного счетчика, входом сброса второго триггера, входом второго элемента задержки и выходом элемента И, первый вход которого соединен с выходом второго элемента НЕ и первыми входами элементов И второй группы, вторые входы которого поразрядно соединены с информационным выходом счетчика адреса

перезаписи и первыми входами элементов И пятой группы, выходы которых соединены с первыми входами элементов ИЛИ второй группы, выходы которых поразрядно соединены с адресным входом второго блока памяти, второй вход элемента И соединен с выходом первого триггера, третий вход элемента И является входом тактовых импульсов устройства, четвертый вход элемента И соединен с выходом первого элемента НЕ и вторыми входами элементов И пятой группы, пятый вход элемента И соединен с выходом третьего триггера, информационный выход реверсивного счетчика поразрядно соединен с первыми входами элементов И шестой группы, вторые входы которого соединены с входом считывания состояния второго блока памяти устройства, выходы элементов И шестой группы соединены поразрядно с информационным выходом второго блока памяти и являются выходом данных устройства, выход второго элемента задержки соединен с входом считывания первого блока памяти и входом записи второго блока памяти, вход считывания которого соединен с выходом третьего элемента задержки, информационный выход первого блока памяти соединен с информационным входом второго блока памяти, информационный выход счетчика считывания поразрядно соединен с вторыми входами элементов И четвертой группы, выходы которых соединены соответственно с вторыми входами элементов ИЛИ второй группы, инверсный выход переполнения второго реверсивного счетчика соединен с входом установки четвертого триггера, выход которого является выходом запрета считывания устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров в однородной вычислительной структуре | 1986 |

|

SU1392572A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство для отладки программ | 1988 |

|

SU1513457A1 |

| Устройство для сортировки @ -разрядных чисел | 1985 |

|

SU1298738A1 |

| Цифровое устройство доплеровской фильтрации | 1990 |

|

SU1830496A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для сортировки чисел | 1985 |

|

SU1277092A1 |

| Запоминающее устройство | 1986 |

|

SU1437915A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных сетей. Целью изобретения является повышение производительности системы путем совмещения процессов записи данных в устройство сопряжения и передачи их по каналам связи. Цель достигается тем, что в устройство, содержащее блок 1 памяти, счетчик 2 адреса записи, счетчик 3 адреса перезаписи, реверсивный счетчик 4, группы 5, 6, 8 элементов И, группу 7 элементов ИЛИ, триггеры 9, 10, элементы 11, 12, задержки введены элементы НЕ 13, 24, элементы ИЛИ 14, 25, элемент И 15, второй блок 16 памяти, счетчик 17 адреса считывания, второй реверсивный счетчик 18, группы 19, 20, 27, элементов И вторая группа 21 элементов ИЛИ, два триггера 22, 23. 1 ил.

| Устройство для сопряжения разноскоростных вычислительных устройств | 1984 |

|

SU1183975A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессоров в однородной вычислительной структуре | 1986 |

|

SU1392572A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1991-07-07—Публикация

1989-07-18—Подача