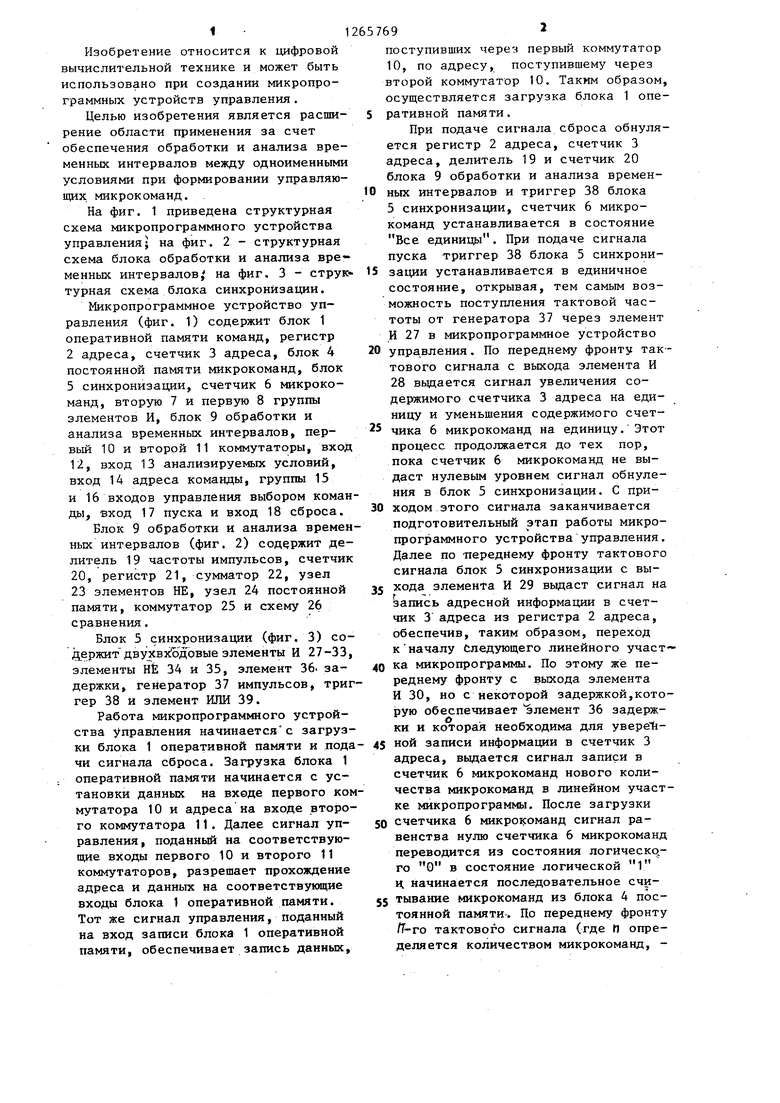

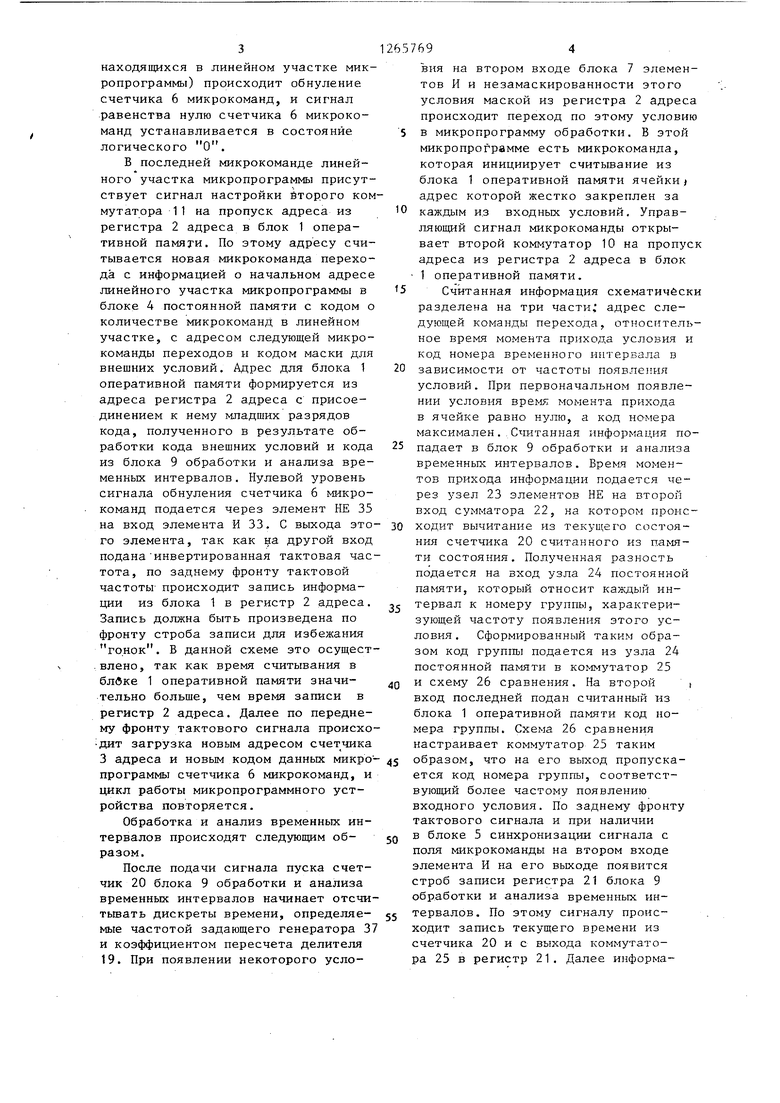

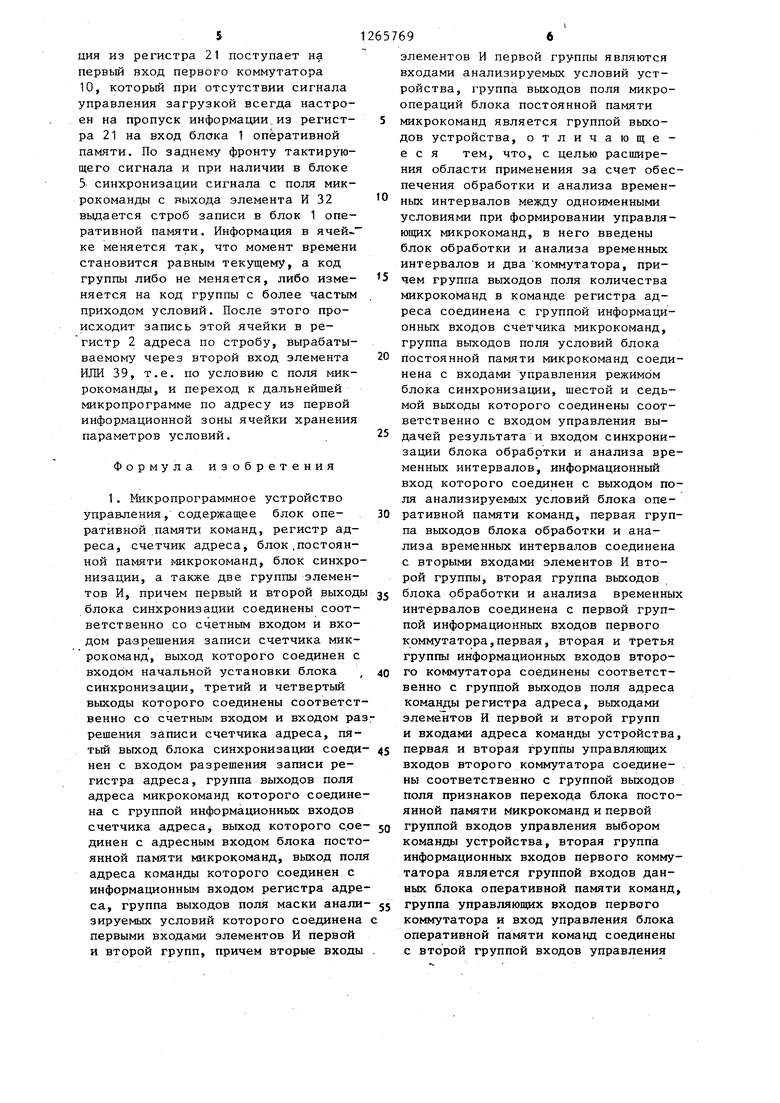

1 Изобретение относится к цифровой вычислительной технике и может быть использовано при создании микропрограммных устройств управления. Целью изобретения является расширение области применения за счет обеспечения обработки и анализа временных интервалов между одноименными условиями при формировании управляющих, микрокоманд. На фиг. 1 приведена структурная схема микропрограммного устройства управления; на фиг. 2 - структурная схема блока обработки и анализа вре менных интервалов, на фиг. 3 - струк турная схема блока синхронизации. Микропрограммное устройство управления (фиг. 1) содержит блок 1 оперативной памяти команд, регистр 2 адреса, счетчик 3 адреса, блок 4 постоянной памяти микрокоманд, блок 5 синхронизации, счетчик 6 микрокоманд, вторую 7 и первую 8 группы элементов И, блок 9 обработки и анализа временных интервалов, первый 10 и второй 11 коммутаторы, вхоД 12, вход 13 анализируемых условий, вход 14 адреса команды, группы 15 и 16 входов управления выбором кома ды, вход 17 пуска и вход 18 сброса. Блок 9 обработки и анализа време ных интервалов (фиг. 2) содержит де литель 19 частоты импульсов, счетчи 20, регистр 21, сумматор 22, узел 23 элементов НЕ, узел 24 постоянной памяти, коммутатор 25 и схему 26 сравнения. Блок 5 синхронизации (фиг. 3) со держит двуХвз одовые элементы И 27 -33 элементы НЕ 34 и 35, элемент 36. задержки, генератор 37 импульсов, три гер 38 и элемент ИЛИ 39. Работа микропрограммного устройства управления начинается с загруз ки блока 1 оперативной памяти и под чи сигнала сброса. Загрузка блока 1 оперативной памяти начинается с установки данных на входе первого ко мутатора 10 и адреса на входе второ го коммутатора 11. Далее сигнал управления , поданный на соответствующие входы первого 10 и второго 11 коммутаторов, разрешает прохождение адреса и данных на соответствуклцие входы блока 1 оперативной памяти. Тот же сигнал управления, поданный на вход записи блока 1 оперативной памяти, обеспечивает запись данных. 9 поступивших через первый коммутатор 10, по адресу, поступившему через второй коммутатор 10. Таким образом, осуществляется загрузка блока 1 оперативной памяти. При подаче сигнала сброса обнуляется регистр 2 адреса, счетчик 3 адреса, делитель 19 и счетчик 20 блока 9 обработки и анализа временных интервалов и триггер 38 блока 5 синхронизации, счетчик 6 микрокоманд устанавливается в состояние Все единицы. При подаче сигнала пуска триггер 38 блока 5 синхронизации устанавливается в единичное состояние, открывая, тем самым возможность поступления тактовой частоты от генератора 37 через элемент И 27 в микропрограммное устройство управления. По переднему фронту тактового сигнала с выхода элемента И 28 вьздается сигнал увеличения содержимого счетчика 3 адреса на единицу и уменьшения содержимого счетчика 6 микрокоманд на единицу. Этот процесс продолжается до тех пор, пока счетчик 6 микрокоманд не выдаст нулевым уровнем сигнал обнуления в блок 5 синхронизации. С приходом этого сигнала заканчивается подготовительный этап работы микропрограммного устройства управления. Далее по ттереднему фронту тактового сигнала блок 5 синхронизации с выхода элемента И 29 выдаст сигнал на г запись адресной информации в счетчик 3 адреса из регистра 2 адреса, обеспечив, таким образом, переход кначалу Следующего линейного участка микропрограммы. По этому же переднему фронту с выхода элемента И 30, но с некоторой задержкой,которую обеспечивает элемент 36 задерж6 . ки и которая необходима для yBepeti«ой записи информации в счетчик 3 адреса, выдается сигнал записи в счетчик 6 микрокоманд нового количества микрокоманд в линейном участке микропрограммы. После загрузки счетчика 6 микрок:оманд сигнал равенства нулю счетчика 6 микрокоманд переводится из состояния логического О в состояние логической 1 и; начинается последовательное считывание микрокоманд из блока 4 постоянной памяти. По переднему фронту /Т-го тактового сигнала (где П определяется количеством микрокоманд, находящихся в линейном участке мик ропрограммы) происходит обнуление счетчика 6 микрокоманд, и сигнал равенства нулю счетчика 6 микрокоманд устанавливается в состояние логического О. В последней микрокоманде линейного участка микропрограммы присут ствует сигнал настройки ёторого ко мутатора 11 на пропуск адреса из регистра 2 адреса в блок 1 оперативной памяти. По этому адресу счи тывается новая микрокоманда перехо да с информацией о начальном адрес линейного участка микропрограммы в блоке 4 постоянной памяти с кодом количестве микрокоманд в линейном участке, с адресом следующей микро команды переходов и кодом маски дл внешних условий. Адрес для блока 1 оперативной памяти формируется из адреса регистра 2 адреса с присоединением к нему младших разрядов кода, полученного в результате обработки кода внешних условий и кода из блока 9 обработки и анализа вре менных интервалов, Нулевой уровень сигнала обнуления счетчика 6 микрокоманд подается через элемент НЕ 35 на вход элемента И 33. С выхода это го элемента, так как на другой вход поданаинвертированная тактовая час тота, по заднему фронту тактовой частоты происходит запись информации из блока 1 в регистр 2 адреса Запись должна быть произведена по фронту строба записи для избежания гонок. В данной схеме это осущест ,влено, так как время считывания в блбке 1 оперативной памяти значительно больше, чем время записи в регистр 2 адреса. Далее по переднему фронту тактового сигнала происхо дит загрузка новым адресом счетчика 3 адреса и новым кодом данных микро программы счетчика 6 микрокоманд, и цикл работы микропрограммного устройства повторяется. Обработка и анализ временных интервалов происходят следующим образом. После подачи сигнала пуска счетчик 20 блока 9 обработки и анализа временных интервалов начинает отсчи тьюать дискреты времени, определяемые частотой задающего генератора 3 и коэффициентом пересчета делителя 19. При появлении некоторого усло694ВИЯ на втором входе блока 7 элементов И и незамаскированности этого условия маской из регистра 2 адреса происходит переход по этому условию в микропрограмму обработки. В этой микропрограмме есть микрокоманда, которая инициирует считывание из блока 1 оперативной памяти ячейки t адрес которой жестко закреплен за каждым из входных условий. Управляющий сигнал микрокоманды открывает второй коммутатор 10 на пропуск адреса из регистра 2 адреса в блок 1 оперативной памяти. Считанная информация схематически разделена на три части; адрес следующей команды перехода, относительное время момента прихода условия и код номера временного интервала в зависимости от частоты появления условий. При первоначальном появлении условия время момента прихода в ячейке равно нулю, а код номера максимален.,Считанная информация попадает в блок 9 обработки и анализа временных интервалов. Время моментов прихода информации подается через узел 23 элементов НЕ на второй вход сумматора 22, на котором пронсходит вычитание из текущего состояния счетчика 20 считанного из памяти состояния. Полученная разность подается на вход узла 24 постоянной памяти, который относит каждый интервал к номеру группы, характеризующей частоту появления этого условия . Сформированный таким образом код группы подается из узла 24 постоянной памяти в коммутатор 25 и схему 26 сравнения. На второй , вход последней подан считанный нз блока 1 оперативной памяти код номера группы. Схема 26 сравнения настраивает коммутатор 25 таким образом, что на его выход пропускается код номера группы, соответствуюЕ1 й более частому появлению входного условия. По заднему фронту тактового сигнала и при наличии в блоке 5 синхронизации сигнала с поля микрокоманды на втором входе элемента И на его выходе появится строб записи регистра 21 блока 9 обработки и анализа временных интервалов. По этому сигналу происходит запись текущего времени из счетчика 20 и с выхода коммутатора 25 в регистр 21. Далее информация из регистра 21 поступает на первый вход первого коммутатора 10, который при отсутствии сигнала управления загрузкой всегда настроен на пропуск информации,из регистра 21 на вход блока 1 оперативной памяти. По заднему фронту тактирующего сигнала и при наличии в блоке 5 синхронизации сигнала с поля микрокоманды с выхода элемента И 32 выдается строб записи в блок 1 оперативной памяти. Информация в ячей- ке меняется так, что момент времени становится равным текущему, а код группы либо не меняется, либо изменяется на код группы с более частым приходом условий. После этого происходит запись этой ячейки в регистр 2 адреса по стробу, вырабатываемому через второй вход элемента ИЛИ 39, т.е. по условию с поля микрокоманды, и переход к дальнейшей микропрограмме по адресу из первой информационной зоны ячейки хранения параметров условий. Формула изобретения 1. Микропрограммное устройство управления, содержащее блок oneративной памяти команд, регистр адреса, счетчик адреса, блок.постоянной памяти микрокоманд, блок синхро низации, а также две группы элементов И, причем первый и второй выход блока синхронизации соединены соответственно со счетным входом и входом разрешения записи счетчика микрокоманд, выход которого соединен с входом начальной установки блока синхронизации, третий и четвертый выходы которого соединены соответст венно со счетным входом и входом ра решения записи счетчика адреса, пятый выход блока синхронизации соеди нен с входом разрешения записи регистра адреса, группа выходов поля адреса микрокоманд которого соедине на с группой информационных входов счетчика адреса, выход которого сое динен с адресным входом блока посто янной памяти микрокоманд, выход пол адреса команды которого соединен с информационным входом регистра адре са, группа выходов поля маски анали зируемых условий которого соединена первыми входами элементов И первсуй и второй групп, причем вторые входы 696 элементов И первой группы являются входами анализируемых условий устройства, группа выходов поля микроопераций блока постоянной памяти микрокоманд является группой выходов устройства, отличающения области применения за счет обеспечения обработки и анализа временных интервалов между одноименными условиями при формировании управляющих микрокоманд, в него введены блок обработки и анализа временных интервалов и два коммутатора, причем группа выходов поля количества микрокоманд в команде регистра адреса соединена с группой информационных входов счетчика микрокоманд, группа выходов поля условий блока постоянной памяти микрокоманд соединена с входами управления режимом блока синхронизации, шестой и седьмой выходы которого соединены соответственно с входом управления выдачей результата и входом синхронизации блока обработки и анализа временных интервалов, информационный вход которого соединен с выходом поля анализируемых условий блока оперативной памяти команд, первая группа выходов блока обработки и анализа временных интервалов соединена с вторыми входами элементов И второй группы, вторая группа выходов блока обработки и анализа временных интервалов соединена с первой группой информационных входов первого коммутатора,первая, вторая и третья группы информационных входов второго коммутатора соединены соответственно с группой выходов поля адреса команды регистра адреса, выходами элементов И первой и второй групп и входами адреса команды устройства, первая и вторая группы управляющих входов второго коммутатора соедине- . вы соответственно с группой выходов поля признаков перехода блока постоянной памяти микрокоманд и первой группой входов управления выбором команды устройства, вторая группа информационных входов первого коммутатора является группой входов данных блока оперативной памяти команд, группа управляющих входов первого коммутатора и вход управления блока оперативной памяти команд соединены с второй группой входов управления выбором команды устройства, выходы первого и второго коммутаторов соединены соответственно с входом данных и входом адреса блока оперативной памяти команд, вход управления записью которого соединен с восьмым выходом блока синхронизации, входы сброса блока синхронизации, счетчика микрокоманд, блока обработки и анализа временных интервалов, регис ра адреса и счетчика адреса объединены и являются входом сброса устройства, вход запуска блока синхронизации является входом пуска устройства, причем блок обработки и анализа временных интервалов содержит делитель частоты импульсов, сче чик, узел постоянной памяти, коммутатор, сумматор, регистр, схему сравнения и узел элементов НЕ, выхо делителя частоты импульсов соединен со счетным входом счетчика, выход которого соединен с первым информационным входом регистра и первым вх дом сумматора, второй вход которого соединен с выходом узла элементов Н выход сумматора через узел постоянной памяти соединен с первым информ ционным входом коммутатора и первым входом схемы сравнения, выход котор соединен с управляющиц входом комму татора, выход которого соединен с вторым информационным входом регист ра, вход узла элементов НЕ, второй вход схемы сравнения и второй информационный вход коммутатора объединены и являются информационным входом блока обработки и анализа временных интервалов, тактовый вход де« лителя частоты импульсов является входом синхронизации блока обработки и анализа временных интервалов, вход управления записью регистра является входом управления выдачей результата блока обработки и анали- за временных интервалов, входы установки делителя частоты импульсов rf счетчика объединены и являются входом сброса блока обработки и анализа временных интервалов, первая и вторая группы выходов регистра являются соответственно первой и втог рой группами выходов блока обработки и анализа временных интервалов. 2. Устройство по п. 1, отличающееся тем, что блок синхронизации содержит триггер, генератор импульсов, элемент задержки, семь элементов И, два элемента НЕ и элемент ИЛИ, причем вход установки в О триггера соединен с входом сброса блока, а вход установки в 1 триггера соединен с входом запуска блока, выход триггера соединен с первым входом первого элемента И, второй вход которого соединенс выходом генератора импульсов, выход первого элемента И соединен с первыми входами второго и третьего элементов И, через элемент задержки с первым входом четвертого элемента И, через первый элемент НЕ с первыми входами пятого, шестого и седьмого элементов И и является седьмыми выходом блока синхронизации, выход второго элемента НЕ соединен с вторыми входами третьего и четвертого элементов И и с первым входом элемента ИЛИ, выход которого соединен с вторым входом седьмого элемента И, а вход второго элемента НЕ соединен с вторым входом второго элемента И и является входом начальной установки блока, выход второго элемента И соединен с первым и третьим выходами блока, выход четвертого элемента И является вторым выходом блока, выход третьего элемента И является , четвертым выходом блока, выход седьмого элемента И - пятым выходом блока, выход ,пятого элемента И - шестым выходом блока, выход шестого элемента И - восьмым выходом блока, вторые входы пятого, шестого элементов И и элемента ИЛИ являются входами управления режимом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано при создании микропрограммных устройств управления. Целью изобретения является расширение области применения за счет обеспечения обработки и анализа временных интервалов между одноименными условиями.при формирований управляющих микрокоманд. Устройство содержит блок оперативной памяти команд, регистр адреса, счетчик адреса, блок постоянной памяти микрокоманд, блок синхронизации, счетчик микрокоманд, две группы элементов И, блок обработки и анализа временных интервалов и два коммутатора. Указанная совокупность технических с SS средств позволяет достичь цели изоб(Л ретения. 1 з.п. ф-лы, 3 ил.

| Микропрограммное устройство управления | 1973 |

|

SU456271A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Хассон С | |||

| Микропрограммное управление .М | |||

| : Мир, 1973, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

Авторы

Даты

1986-10-23—Публикация

1984-06-12—Подача