со со ел со

Изобретение относится к многоканальным системам передачи электрических сигналов и предназначено для программного управления скоростью передачи потоков сообщений по каждому каналу в сетях передачи информации.

Цель изобретения - повышение информационной гибкости.

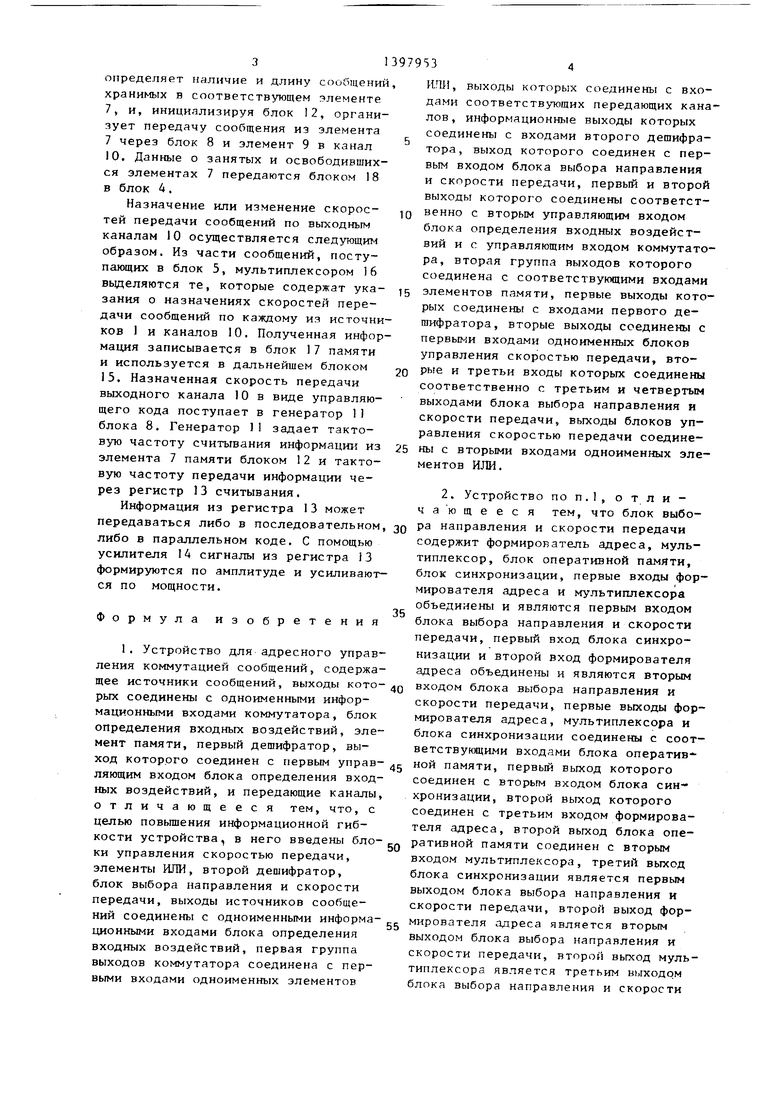

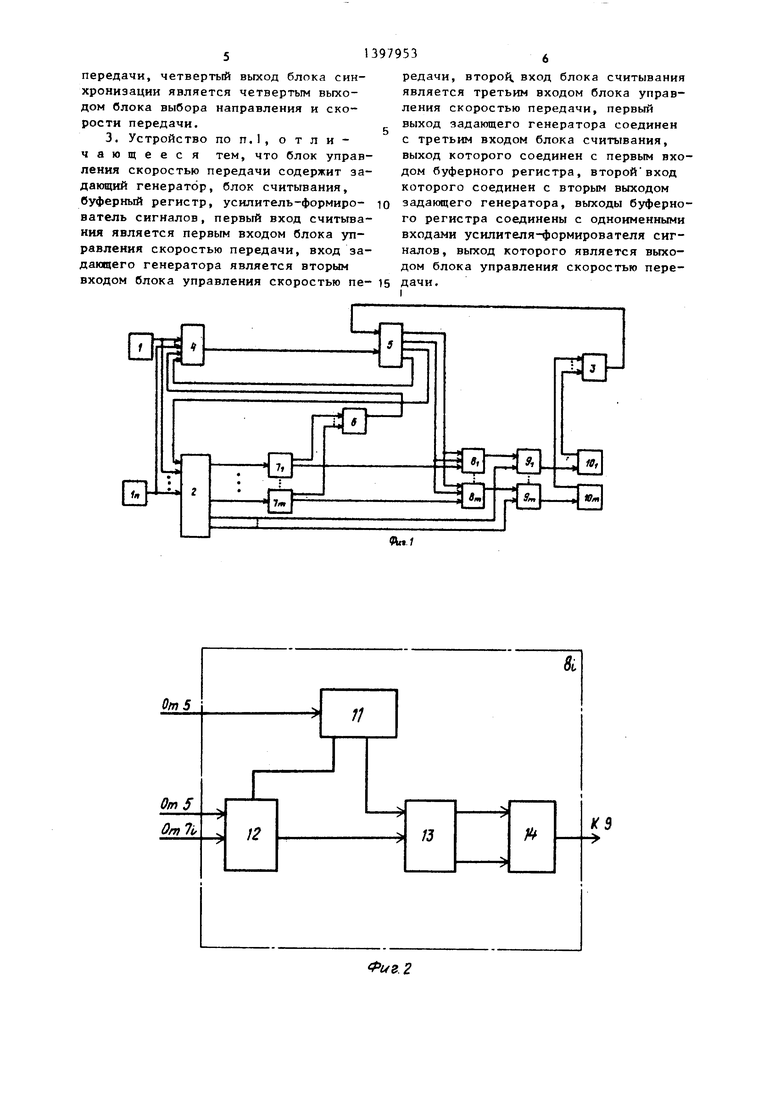

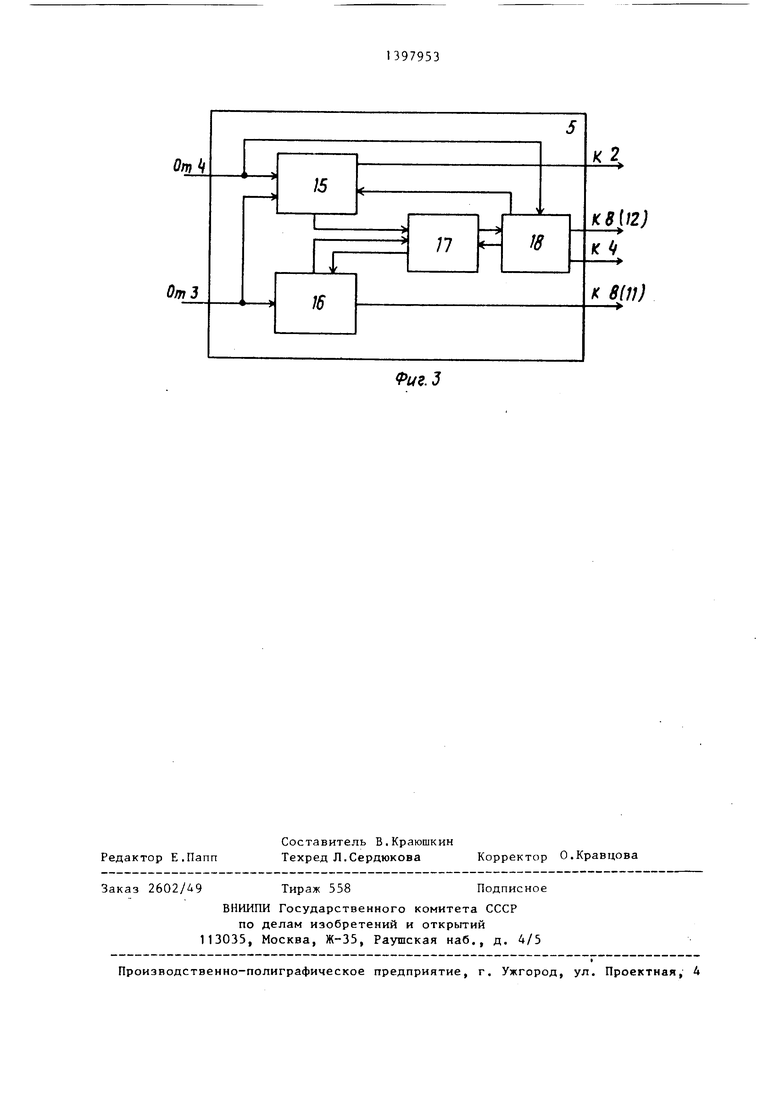

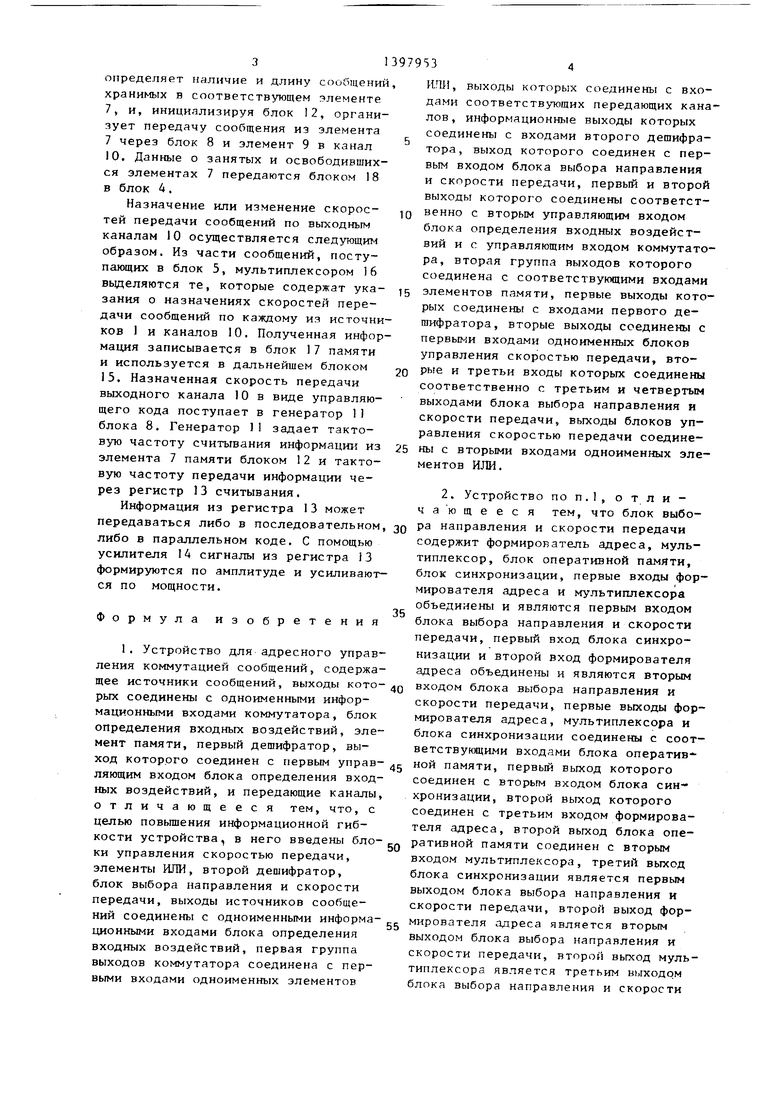

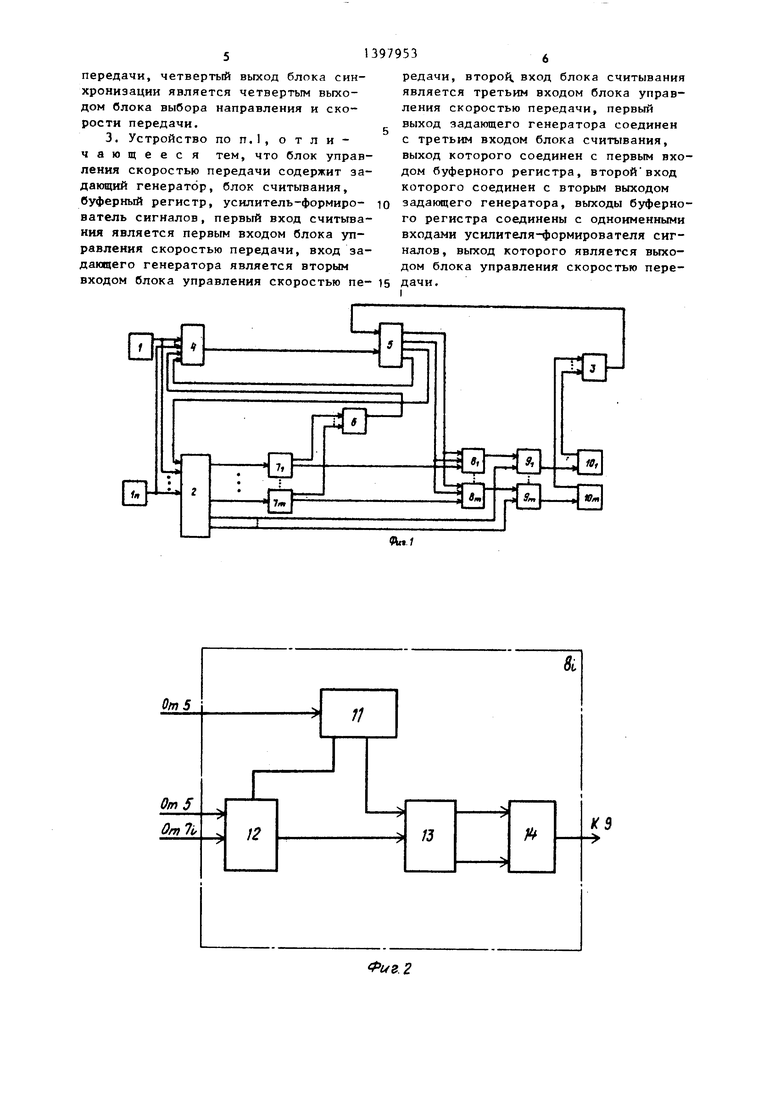

На фиг.1 приведена структурная схема устройства для адресного управления коммутацией сообщений; на фиг.2 структурная схема блока управления скоростью передачи информации; на фиг.З - структурная схема блока, предназначенного для выбора направления и скорости передачи поступившего сообщения.

Структурная схема устройства со- держит источники , „ сообщений, коммутатор 2 из п входных каналов либо в m выходных каналов, либо в элементы памяти, второй дешифратор 3 (состояний приемников сообщений), определяющий наличие свободных приемников сообщений в каждый текущий момент времени, блок 4 определения входных воздействий, блок 5, предназначенный для выбора направления передачи поступившего сообщения в элементы памяти или непосредственно на выходные каналы и выбора скорости его передачи, первый дешифратор 6, определяющий состояние (т.е. заполнение) элементов памяти, блоки управления скоростью передачи, элементы ИЛИ 9i-9fn, выходные каналы передачи сообщений.

Блок 8 управления скоростью пере- дачи информации (фиг.2) содержит задающий генератор 1I, блок 12 считывания для организации считывания информации из элементов 7 памяти, буфер- ньй регистр 13 и усилитель-формировагель 14 выходных сигналов.

Блок 5 (фиг.З) содержит формирователь 15 адреса, определяющий адрес приемника или элемента 7 памяти и управляющий блоком 2. мультиплексор 6, блок 17 оперативной памяти, хранящий оперативную информацию, и блок 18 синхронизации.

Устройство работает следующим образом,

Входная информация о г источников 1, , 1 J, .. . , 1 поступает в коммутатор 2 и блок 4 определения входных воздействий и содержит как непосредственно информлиионную часть, передаваемую абоненту сети, так и адресную , в которой указаны пункты возникновения и назначения сообщений, признаки начала и конца передачи, указания о назначении или изменении скоростей передачи сообщений по каналам связи и т.д.

Блок 4 из адресной части поступающих сообщений вьутеляет информацию с указанием адресов приемников сообщений (адресная часть, не содержащая адресов приемника, транслируется для анализа в блок 5). На основе информации о заданных адресах приемников и данных о наличии незаполненных элементов 7,, 7 , . . . , 7 памяти (информация дешифратора состояния элементов 7 памяти и блока 18 синхронизации) блок 4 либо передает в формирователь 15 адреса номера предпочтительных каналов передачи сообщения, либо выдает сигнал отказа источнику сообщения

до освобождения элементов 7 памяти.

Формирователь 15 адреса на основе анализа информации дешифратора 3 о наличии свободных выходных каналов 10, информации блока 4 о предпочтительных каналах передачи сообщения и данных блока 17 памяти о текущих значениях скоростей передачи сообщений по входным и выходньЕМ каналам выбирает в качестве приемника сообщения либо свободный канал 10 со скоростью передачи сообщений, совпадающей со скоростью передачи входного канала, либо при отсутствии свободных приемников или несовпадении скоростей передачи элемент памяти 7;.

Выбранный формирователем 15 адрес в виде управляющего воздействия поступает в коммутатор 2, который и направляет сообщение либо через соответствующий элемент ИЛИ 9. по каналу 10, либо в элемент 7 памяти. Завершение передачи сообщения и его длина определяются блоком 18 синхронизации по признаку конца передачи в адресной части сообщения.

Формирователь 15 передает в блок 17 памяти номера элементов 7, хранящих принятые сообщения, и по команде блока 18 о завершении передачи сообщения переводит блок 2 в высокоимпе- дансное состояние.

По мере готовности каналов 10 (информация дешифраторов 3) блок 18 синхронизации по данным блока I7 памяти

определяет наличие и длину сообщений хранимых в соответствующем элементе 7, и, инициализируя блок 12, организует передачу сообщения из элемента 7 через блок 8 и элемент 9 в канал 10. Данные о занятых и освободившихся элементах 7 передаются блоком 18 в блок f.

Назначение или изменение скоростей передачи сообщений по выходным каналам 10 осуществляется следующим образом. Из части сообщений, поступающих в блок 5, мультиплексором 16 вьщеляются те, которые содержат указания о назначениях скоростей передачи сообщений по каждому из источников 1 и каналов 10, Полученная информация записывается в блок 17 памяти и используется в дальнейшем блоком 15. Назначенная скорость передачи выходного канала 10 в виде управляющего кода поступает в генератор 11 блока 8. Генератор II задает тактовую частоту считывания информации из элемента 7 памяти блоком 12 и тактовую частоту передачи информации через регистр 13 считывания.

Информация из регистра I3 может

ИПИ, выходы которых соединены с входами соответствующих передающих каналов , информационные выходы которых соединены с входами второго дешифратора, выход которого соединен с первым входом блока выбора направления и скорости передачи, первый и второй выходы которого соединены соответстQ венно с вторым управляющим входом блока определения входных воздействий и с управляющим входом коммутатора, вторая группа выходов которого соединена с соответствующими входами

5 элементов памяти, первые выходы которых соединены с входами первого дешифратора, вторые выходы соединены с первыми входами одноименных блоков управления скоростью передачи, втоQ рые и третьи входы которых соединены соответственно с третьим и четвертым выходами блока выбора направления и скорости передачи, выходы блоков управления скоростью передачи соедине5 ны с вторыми входами одноименных элементов ИЛИ,

2. Устройство по п,1, о т л и - ча ющееся тем, что блок выбо

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля и диагностики цифровых узлов | 1984 |

|

SU1249488A1 |

| Многоканальное микропрограммное устройство ввода-вывода | 1983 |

|

SU1104500A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

Изобретение относится к многоканальным системам передачи злектри- ческих сигналов и предназначено для программного управления скоростью передачи потоков сообщений по каждому из каналов. Целью изобретения является повышение информационной гибкости устройства. Устройство содержит источники сообщений, коммутатор. первый и второй дешифраторы, блок определения входных воздействий, блок выбора направления передачи, элементы памяти, блоки управления скоростью передачи, элементы ИЛИ, передающие каналы. Устройство для адресного управления коммутацией сообщений позволяет расширить функциональные возможности устройства, т.к. часть сообщений может передаваться потребителю без промежуточного хранения в зле- ментах памяти. А возможность управлять по команде от внешнего устройства настройкой скорости передачи информации по каждому выходноь у каналу позволяет повысить зффективность использования каналов, а также применять данное устройство в качестве аппаратного средства для адаптации сети информационной связи как в процессе проектирования, так и в процессе функционирования. 2 з.п, ф-лы, 3 ил. (Я

передаваться либо в последовательном, зо Р направления и скорости передачи

либо в параллельном коде. С помощью усилителя 14 сигналы из регистра 13 формируются по амплитуде и усиливаются по мощности.

Формула изобретения

I, Устройство для адресного управления коммутацией сообщений, содержащее источники сообщений, выходы кото- Q входом блока выбора направления и

рых соединены с одноименными информационными входами коммутатора, блок определения входных воздействий, элемент памяти, первый дешифратор, выход которого соединен с первым управляющим входом блока определения входных воздействий, и передающие каналы отличающееся тем, что, с целью повьшгения информационной гибкости устройства, в него введены блоки управления скоростью передачи, элементы ИЛИ, второй дешифратор, блок выбора направления и скорости передачи, выходы источников сообщений соединены с одноименными информационными входами блока определения входных воздействий, первая группа выходов коммутатора соединена с пер

выми входами одноименных элементов

5

:одержит формирователь адреса, мультиплексор, блок оперативной памяти, блок синхронизации, первые входы формирователя адреса и мультиплексора объединены и являются первым входом блока выбора направления и скорости передачи, первый вход блока синхронизации и второй вход формирователя адреса объединены и являются вторым

скорости передачи, первые выходы формирователя адреса, мультиплексора и блока синхронизации соединены с соответствующими входами блока оператив- ной памяти, первый вьгход которого соединен с вторым входом блока синхронизации, второй выход которого соединен с третьим входом формирователя адреса, второй выход блока оперативной памяти соединен с вторым входом мультиплексора, третий вьгход блока синхронизации является первым выходом блока выбора направления и скорости передачи, второй выход формирователя адреса является вторым выходом блока выбора направления и скорости передачг, второй вьгход мультиплексора является третьим выходом блока выбора направления и скорости

передачи, четвертый выход блока синхронизации является четвертым выходом блока выбора направления и скорости передачи.

От

От 5 От%

J2

редачи, второй, вход блока считывания является третьим входом блока управления скоростью передачи, первый выход задающего генератора соединен с третьим входом блока считывания, выход которого соединен с первым входом буферного регистра, второй вход которого соединен с вторым выходом задающего генератора, выходы буферного регистра соединены с одноименными входами усилителя-формирователя сигналов, вьгход которого является выходом блока управления скоростью передачи.

Ла1

13

1

КЗ

Фиг.2

/. J

| Устройство для адресного управления коммутацией сообщений | 1981 |

|

SU963044A2 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-05-23—Публикация

1986-02-04—Подача