Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального и диагностического контроля цифровых узлов и блоков.

Цель изобретения - расширение области применения системы, что позволит применять ее совместно с ЭВМ, а также с аппаратурой в стандарте КОП.

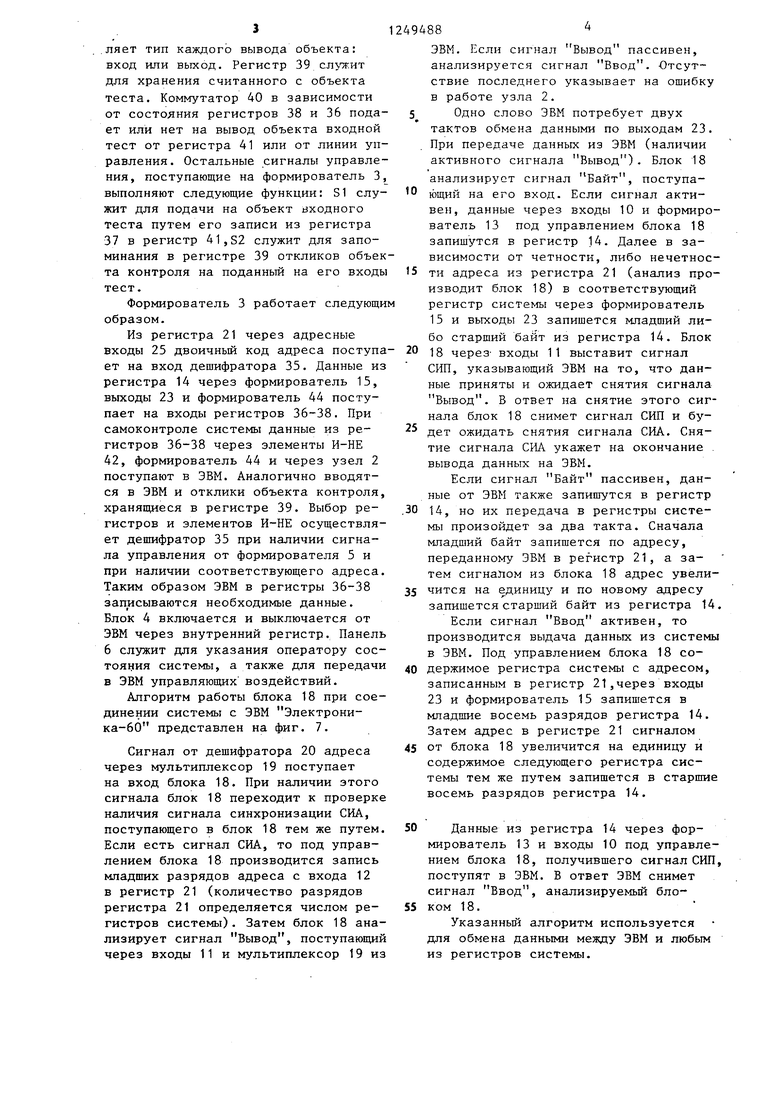

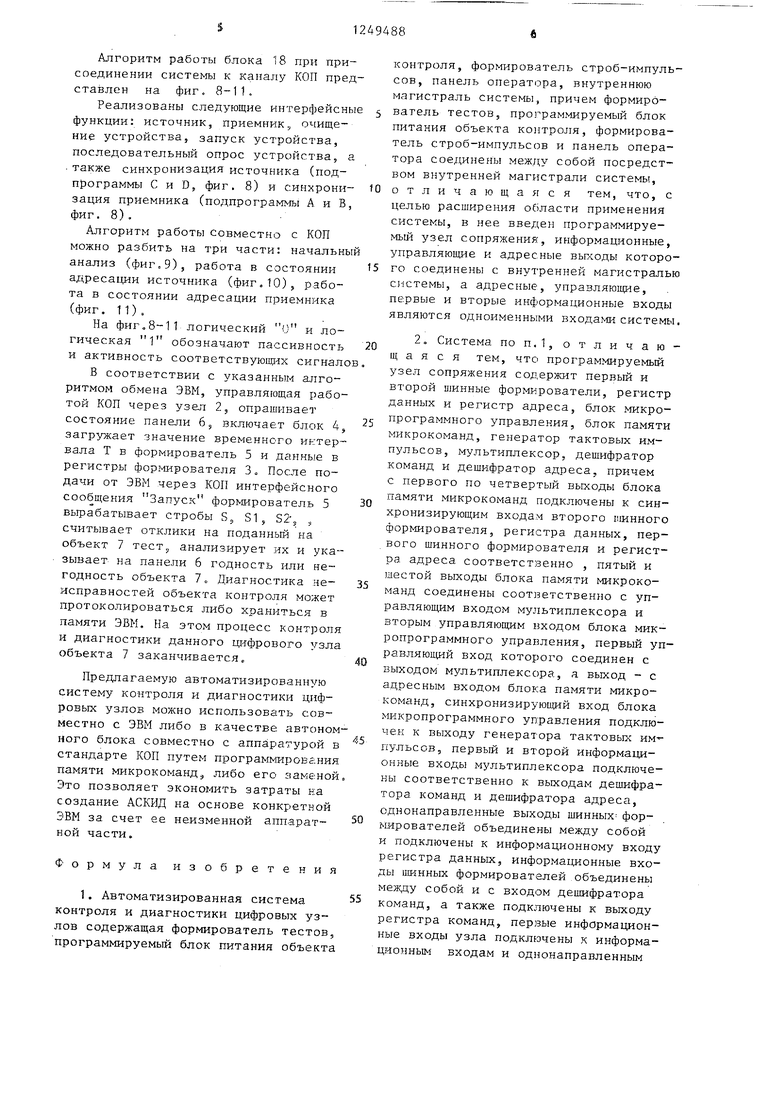

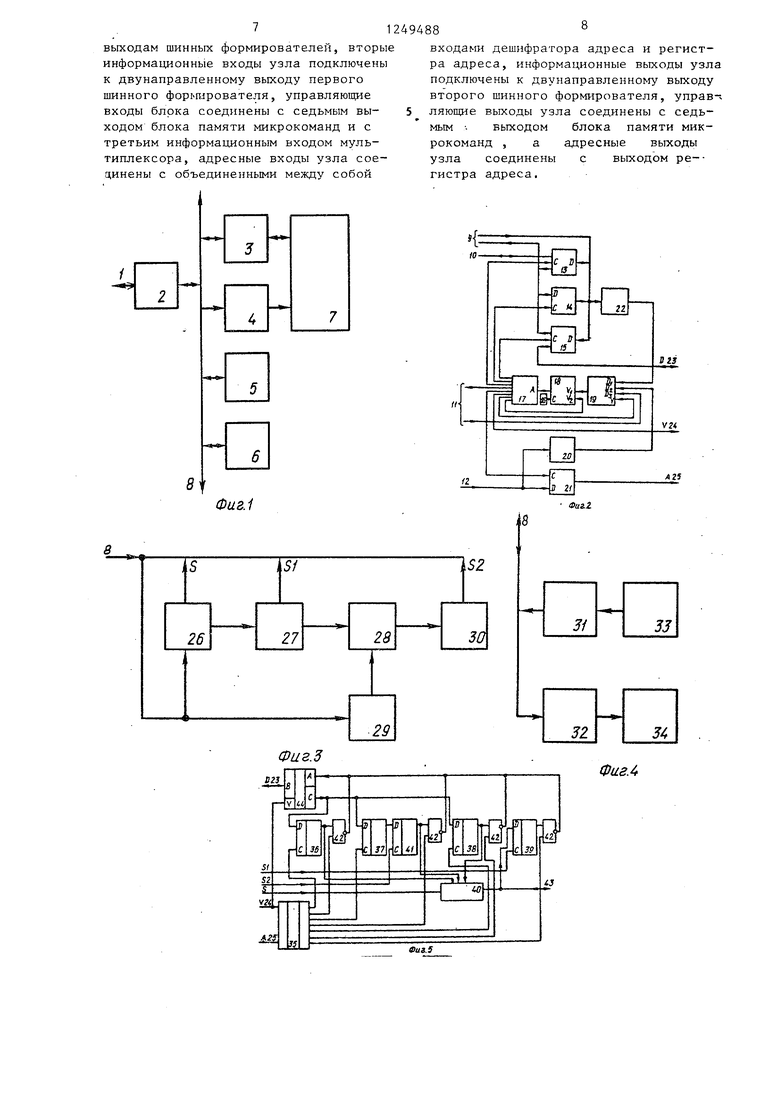

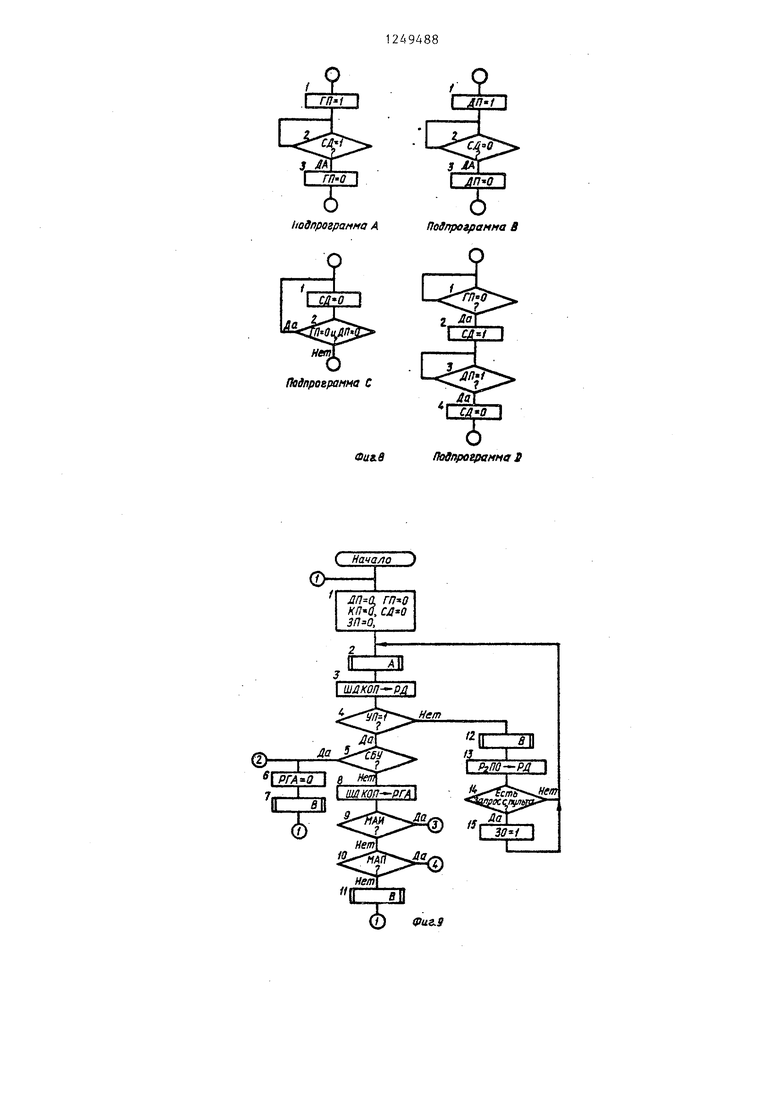

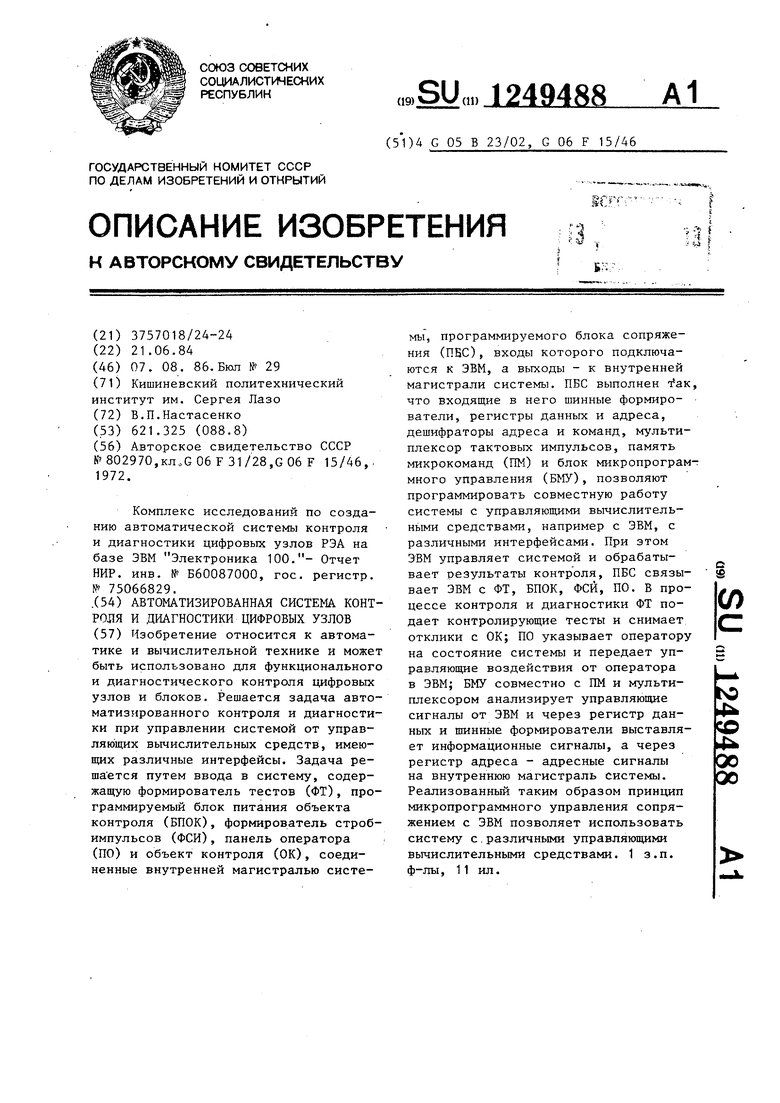

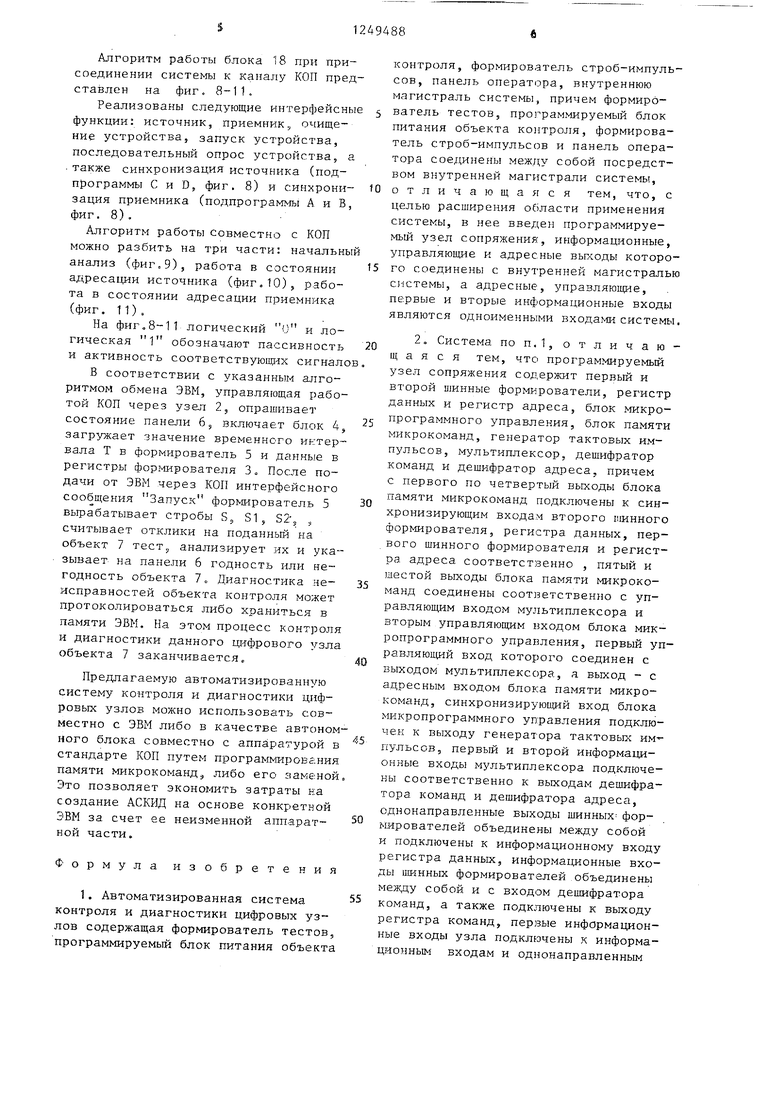

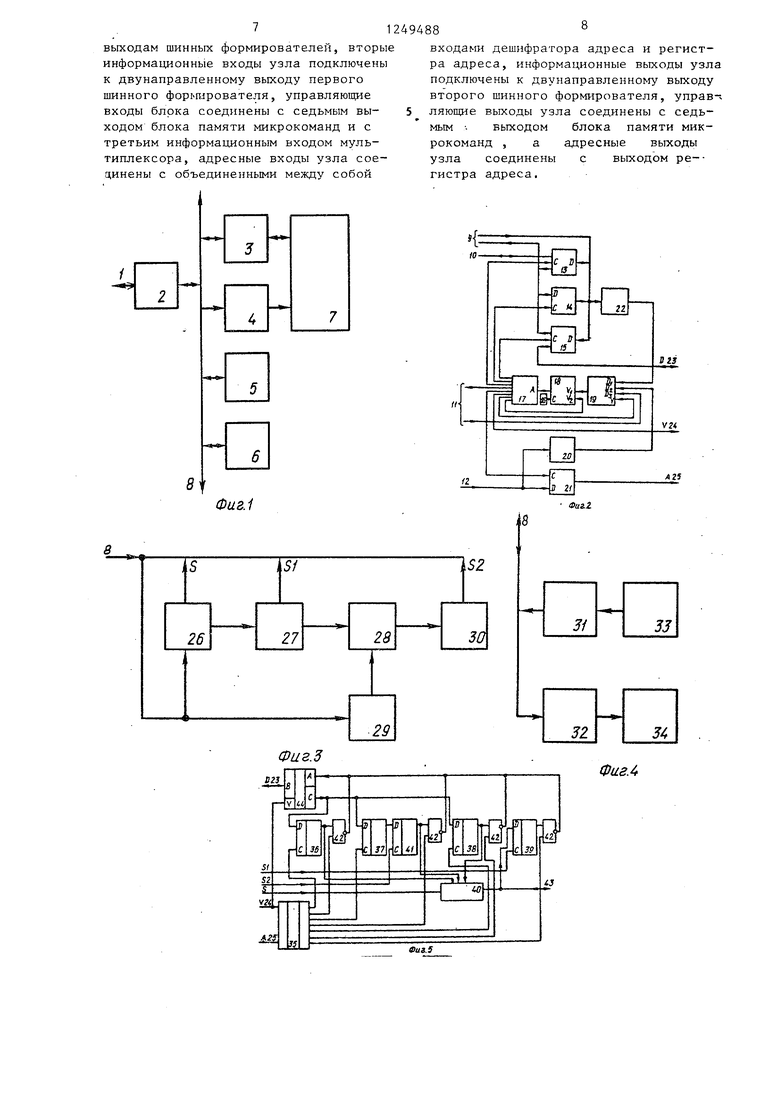

На фиг. 1 представлена блок-схема автоматизированной системы контроля и диагностики (АСКИД) с программируемым узлом сопряжения; -на фиг.2- структурная схема программируемого узла сопряжения; на фиг. 3- блок- схема формирователя строб-импульсов; на фиг. 4- блок-схема пульта оператора; на фиг. 5- функциональная схема формирователя тестов; на фиг. 6 - структурная схема блока микропрограммного управления (ЕМУ); на фиг. 7- блок-схема алгоритма работы (БМУ) при подключении системы к ЭВМ; на фиг. 8-11 - блок-схемы алгоритма работы БМУ при подключении системы к каналу КОП.

Оистема содержит входы 1, служащие для подключения ЭВМ, программируемый узел 2 сопряжения, формирователь 3 тестов, программируемый блок 4 питания объекта контроля, формирователь 5 строб-импульсов, панель 6 оператора , объект 7 контроля, внутреннюю магистраль 8 системы.

Программируемый узел 2 сопряжения содержит первые информационные входы 9, вход 10, информационные входы 11 управления, входы 12 адреса, шинный формирователь 13, регистр 14 данных, шинный формирователь 15, генератор 16 тактовых импульсов (ГТИ), блок 17. памяти микрокоманд, блок 18 микропрограммного управления, мультиплексор 19, дешифратор 20 адреса, регистр 45 с; либо к однонаправленным входам 9,

21 адреса, дешифратор 22 команд, информационные 23, управляющие 24 и адресные 25 выходы.

Выходы 23-25 совместно с внутреннёй магистралью строб-импульсов, сое- jo нала, подаваемого на вход объекта 7, тоящей из линий S, S1 и S2,образуют внутреннюю магистраль 8 системы.

.Формирователь 5 строб-импульсов содержит формирователи 26, 27, 28, и 30 импульсов и регистр 29 задания временного интервала.

Панель 6 оператора соде ржит регистр 31 управления, регистр 32 индикации.

55

импульсньш либо потенциальньш, задавать вид контролируемой точки - вход либо выход объекта,.

Регистр 36 определяет тип подаваемого на каждьм вывод объекта входного теста: импульсный или потенциальный. Регистр 37 временно хранит входной тест объекта. Регистр 38 опредеорганы 33 управления, элементы 34 индикации .

Формирователь 3 состоит из дешифратора 35 адреса, регистров типа сигнала - импульсный или потенциальный 36, входного теста 37, входа- выхода 38, считанного теста 39, а также из коммутатора 40 буферного регистра 41 входного теста, элементов И-НЕ 42,

выводов (входов или вь ходов) 43

обьекта контроля, шинного формирователя 44.

Блок 18 (фиг. 8) состоит из регистра 45 кода команды, регистра 46

флажков, логической схемы 47 опреде- легия следующего адреса микрокоманды, регистра 48 адреса микрокоманды, выходных буферов 49, линий 50 адреса микрокоманды, линии 51 синхронизации,

линий 52 команды,линий 53 управления, линии 54 входа признаков, линии 55 выбора флажков.

Линии 52, 53 и 55 подсоединяются к соответствующим выходам ПМ 17.

Вход линии 54 соединяется с выходом мультиплексора 19 и служит для подачи в регистр 46 сигналов- условий ветвления алгоритма обмена. Схема 47 в зависимости от регистров 45 и 46 и

линий 53 вырабатывает следующий адрес микрокоманды, поступающий в регистр 48 и далее через буфер 49 на адресные входы блока 17 памяти. Блок 18 тактируется от генератора 16 через

линию 51 синхронизации.

Система работает следующим образом.

Подключаемая к входам ЭВМ управ- ляет системой и обрабатывает результаты контроля. Узел 2 связывает ЭВМ с формирователем 3,, блоком 4, формирователем 5 и панелью 6. В зависимости от типа ЭВМ она может подключатьлибо к двунаправленным входам 10.

Формирователь 3 позволяет подавать контролируюЕдие тесты и снимать отклики с объекта 7, управлять типом сиг

импульсньш либо потенциальньш, задавать вид контролируемой точки - вход либо выход объекта,.

Регистр 36 определяет тип подаваемого на каждьм вывод объекта входного теста: импульсный или потенциальный. Регистр 37 временно хранит входной тест объекта. Регистр 38 опреде3

,ляет тип каждого вывода объекта: вход или выход. Регистр 39 сл 7кит для хранения считанного с объекта теста. Коммутатор 40 в зависимости от состояния регистров 38 и 36 подает или нет на вывод объекта входной тест от регистра 41 или от линии управления. Осталъные сигналы управления, поступающие на формирователъ 3, выполняют следующие функции: S1 служит для подачи на объект входного теста путем его записи из регистра 37 в регистр 41,52 служит для запоминания в регистре 39 откликов объекта контроля на поданный на его входы тест.

Формирователь 3 работает следующи образом.

Из регистра 21 через адресные входы 25 двоичный код адреса поступает на вход дешифратора 35. Данные из регистра 14 через формирователь 15, выходы 23 и формирователь 44 поступает на входы регистров 36-38. При самоконтроле системы данные из регистров 36-38 через элементы И-НЕ 42, формирователь 44 и через узел 2 поступают в ЭВМ. Аналогично вводятся в ЭВМ и отклики объекта контроля, хранящиеся в регистре 39. Выбор регистров и элементов И-НЕ осуществляет дешифратор 35 при наличии сигнала управления от формирователя 5 и при наличии соответствующего адреса. Таким образом ЭВМ в регистры 36-38 записываются необходимые данные. Блок 4 включается и выключается от ЭВМ через внутренний регистр. Панель 6 служит для указания оператору состояния системы, а также для передачи в ЭВМ управляющих воздействий.

Алгоритм работы блока 18 при соединении системы с ЭВМ Электрони- ка-60 представлен на фиг. 7.

Сигнал от дешифратора 20 адреса через мультиплексор 19 поступает на вход блока 18. При наличии этого сигнала блок 18 переходит к проверке наличия сигнала синхронизации СНА, поступающего в блок 18 тем же путем. Если есть сигнал СИА, то под управлением блока 18 производится запись младших разрядов адреса с входа 12 в регистр 21 (количество разрядов регистра 21 определяется числом регистров системы). Затем блок 18 анализирует сигнал Вывод, поступающий через входы 11 и мультиплексор 19 из

49488

ЭВМ. Если сигнал Вывод пассивен, анализируется сигнал Ввод. -Отсутствие последнего указывает на ошибку в работе узла 2. 5 Одно слово ЭВМ потребует двух

тактов обмена данными по выходам 23. При передаче данных из ЭВМ (наличии активного сигнала Вывод). Блок 18 анализирует сигнал Байт, поступа- ющий на его вход. Если сигнал активен, данные через входы 10 и формирователь 13 под управлением блока 18 запишутся в регистр 14. Далее в зависимости от четности, либо нечетнос- 5 ти адреса из регистра 21 (анализ производит блок 18) в соответствующий регистр системы через формирователь 15 и выходы 23 запишется младший либо старший байт из регистра 14. Блок 18 через- входы 11 выставит сигнал СИП, указывающий ЭВМ на то, что данные приняты и ожидает снятия сигнала Вывод. В ответ на снятие этого сигнала блок 18 снимет сигнал СИП и бу- дет ожидать снятия сигнала СИА. Снятие сигнала СИА укажет на окончание . вывода данных на ЭВМ.

Если сигнал Байт пассивен, данные от ЭВМ также запишутся в регистр 30 14, но их передача в регистры системы произойдет за два такта. Сначала младший байт запишется по адресу, переданному ЭВМ в регистр 21, а затем сигналом из блока 18 адрес увели- 35 чится на единицу и по новому адресу запишется старший байт из регистра 14.

Если сигнал Ввод активен, то производится выдача данных из системы в ЭВМ. Под управлением блока 18 со- 40 держимое регистра системы с адресом, записанным в регистр 21,через входы 23 и формирователь 15 запишется в младшие восемь разрядов регистра 14. Затем адрес в регистре 21 сигналом 45 от блока 18 увеличится на единицу и содержимое следующего регистра системы тем же путем запишется в старшие восемь разрядов регистра 14.

50 Данные из регистра 14 через формирователь 13 и входы 10 под управлением блока 18, получившего сигнал СИП, поступят в ЭВМ. В ответ ЭВМ снимет сигнал Ввод, анализируемьй бло55 ком 18.

Указанный алгоритм используется для обмена данными между ЭВМ и любым из регистров системы.

Алгоритм работы блока 18 при присоединении системы к каналу КОП представлен на фиг. 8-11.

Реализованы следующие интерфейсны функции: источник, приемник, очищение устройства, запуск устройства, последовательный опрос ycTpoiicTBa, а .также синхронизация источника (подпрограммы С и D, фиг. 8) и синхрони- зация приемника (подпрограммы А и В, фиг. 8).

Алгоритм работы совместно с КОП можно разбить на три части: начальны анализ (фиг.9), работа в состоянии адресации источника (фиг.10), работа в состоянии адресации приемника (фиг. 11).

На фиг,8-11 логический О и логическая 1 обозначают пассивность и активность cooTBeTCTByraitq;ix сигнало

В соответствии с указанным алгоритмом обмена ЭВМ, управляющая работой КОП через узел 2, опрашивает состояние панели 6, включает блок 4, загружает значение временного интервала Т в формирователь 5 и данные в регистры формирователя Зо После подачи от ЭВМ через КОП интерфейсного сообщения Запуск формирователь 5 вьфабатывает стробы S, SI, 52% ., считывает отклики на поданный на объект 7 тест,, анализирует их и указывает на панели 6 годность или негодность объекта 7 Диагностика не- исправностей объекта контроля может протоколироваться либо храниться в памяти ЭВМ, На этом процесс контроля и диагностики данного Ц1-1фрового узла объекта 7 заканчивается

Предлагаемую автоматизированную систему контроля и диагностики цифровых узлов можно использовать совместно с ЭВМ либо в качестве автономного блока совместно с аппаратурой в

стандарте КОП путем программирования памяти микрокоманд3 либо его ;1аме;ной Это позволяет экономить затраты на создание АСКИД на основе конкретной ЭВМ за счет ее неизменной аппарат- ной части,

Ф ормула изобретения

1, Автоматизированная система контроля и диагностики цифровых узлов содержащая формирователь тестов, программируемый блок питания объекта

контроля, формирователь строб-импульсов, панель оператора, внутреннюю магистраль системы, причем формирователь тестов, программируемый блок питания объекта контроля, формирователь строб-импульсов и панель оператора соединены между собой посредством внутренней магистрали системы, отличающаяся тем, что, с целью расширения области применения системы, в нее введен программируемый узел сопряжения, информационные, управляющие и адресные вьгходы которого соединены с внутренней магистраль системы, а адресные, заправляющие, первые и вторые инф ормационные входы являются одноименными входами системы

2, Система поп.1, отличающаяся тем, что программируемый узел сопряжения содержит первый и второй шинные формирователи, регистр данных и регистр адреса, блок микропрограммного управления, блок памяти микрокоманд, генератор тактовых импульсов, мультиплексор, дешифратор команд и дешифратор адреса, причем с первого по четвертый выходы блока памяти микрокоманд подключены к синхронизирующим входам второго шинного формирователя, регистра данных, первого шинного формирователя и регистра адреса соответственно , пятый и шестой выходы блока памяти микрокоманд соединены соответственно с управляющим входом мультиплексора и вторым управляющим входом блока микропрограммного управления, первый управляющий вход которого соединен с выходом мультиплексора, а выход - с адресным входом блока памяти микрокоманд, синхронизирующий вход блока микропрограммного управления подключен к выходу генератора тактовых им пульсов, первый и второй информационные входы мультиплексора подключены соответственно к выходам дешифратора команд и дешифратора адреса, однонаправленные выходы шинных формирователей объединены между собой и подключены к информационному входу регистра данных, информационные входы шинных формирователей объединены меж,цу собой и с входом дешифратора команд, а также подключены к выходу регистра команд, первые информационные входы узла подключены к информа- ционньпу входам и однонаправленным

выходам шинных формирователей, вторые информационные входы узла подключены к двунаправленному выходу первого шинного формирователя, управляющие входы блока соединены с седьмым выходом блока памяти шкрокоманд и с третьим информационным входом мультиплексора, адресные входы узла сое- а1инены с объединенными между собой

входами дешифратора адреса и регистра адреса, информационные выходы узла подключены к двунаправленному выходу второго шинного формирователя, управ- ляюш11е выходы узла соединены с седьмым . выходом блока памяти микрокоманд , а адресные выходы узла соединены с выходом ре-- гистра адреса.

лг

Фив.1

iDaiZ

а .

S2

Фиг.З

сгз

ASL

Фаз. 4

ЛСАМК

/JAMKSO

Вых Б

49

РАМК

48

7

5f

4 / 4

ЛВФ55 ВП5

ЛУ53 ЛК52 Фаг. 6

6

Подпрограмма А

,

I ЛП-Г

6

ЛоЯпрояранма В

Падпроерамма С

Фиг-в

ПоОпрограммв S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для ввода информации | 1988 |

|

SU1716501A1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для функционального и диагностического контроля цифровых узлов и блоков. Решается задача автоматизированного контроля и диагностики при управлении системой от управляющих вычислительных средств, имеющих различные интерфейсы. Задача ре- ша ется путем ввода в систему, содержащую формирователь тестов (ФТ), программируемый блок питания объекта контроля (БЛОК), формирователь строб- импульсов (ФСИ), панель оператора (ПО) и объект контроля (ОК), соединенные внутренней магистралью системы, программируемого блока сопряжения (ПБС), входы которого подключаются к ЭВМ, а выходы - к внутренней магистрали системы. ПБС выполнен , что входящие в него шинные формирователи, регистры данных и адреса, дешифраторы адреса и команд, мультиплексор тактовых импульсов, память микрокоманд (ИМ) и блок микропрограммного управления (БМУ), позволяют программировать совместную работу системы с управляющими вычислительными средствами, например с ЭВМ, с различными интерфейсами. При этом ЭВМ управляет системой и обрабатывает результаты контроля, ПБС связывает ЭВМ с ФТ, БПОК, ФСЙ, ПО. В процессе контроля и диагностики ФТ подает контролирующие тесты и снимает отклики с ОК; ПО указывает оператору на состояние системы и передает управляющие воздействия от оператора в ЭВМ; БМУ совместно с ПМ и мультиплексором анализирует управляющие сигналы от ЭВМ и через регистр данных и шинные формирователи выставляет информационные сигналы, а через регистр адреса - адресные сигналы на внутреннюю магистраль системы. Реализованный таким образом принцип микропрограммного управления сопряжением с ЭВМ позволяет использовать систему с.различными управляющими вычислительными средства1 ш. 1 з.п. ф-лы, 11 ил. i (Л

Д

у I 1МКОП- РГА

и ..li

(Ь

| Устройство для функционального конт-РОля бОльшиХ иНТЕгРАльНыХ CXEM | 1977 |

|

SU802970A1 |

| Облицовка комнатных печей | 1918 |

|

SU100A1 |

| инв | |||

| № Б60087000, гос | |||

| регистр | |||

| № 75066829 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-08-07—Публикация

1984-06-21—Подача