г

Изобретение относится к радиотехнике и вычислительной технике и. мо- жрт быть использовано в устройствах многоканальной связи с цифровой обработкой сигнала

Цель изобретения - расширение области применения фильтра за счет формирования выходного группового сигнала.

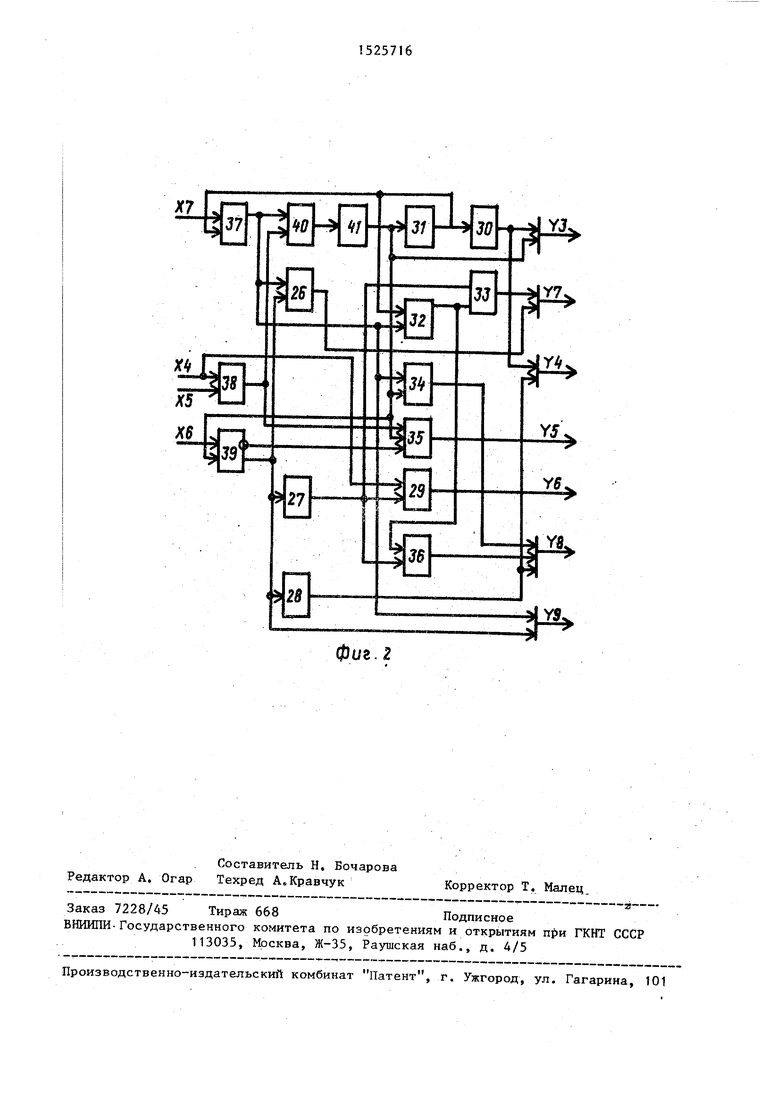

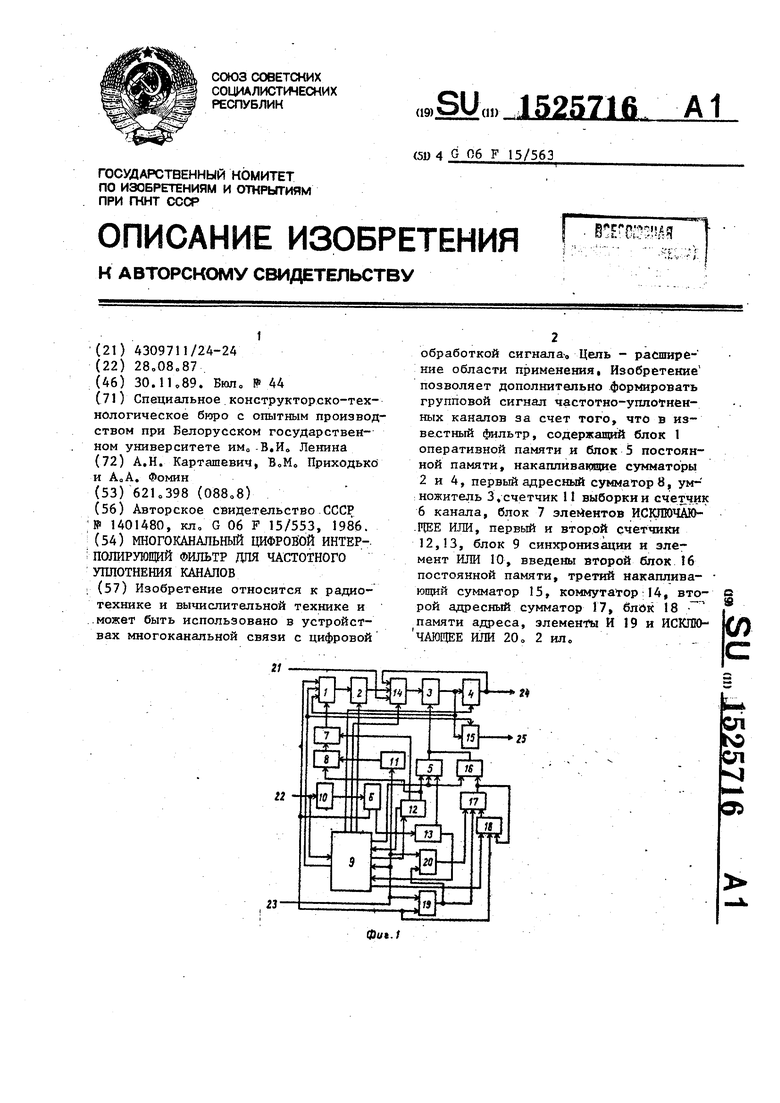

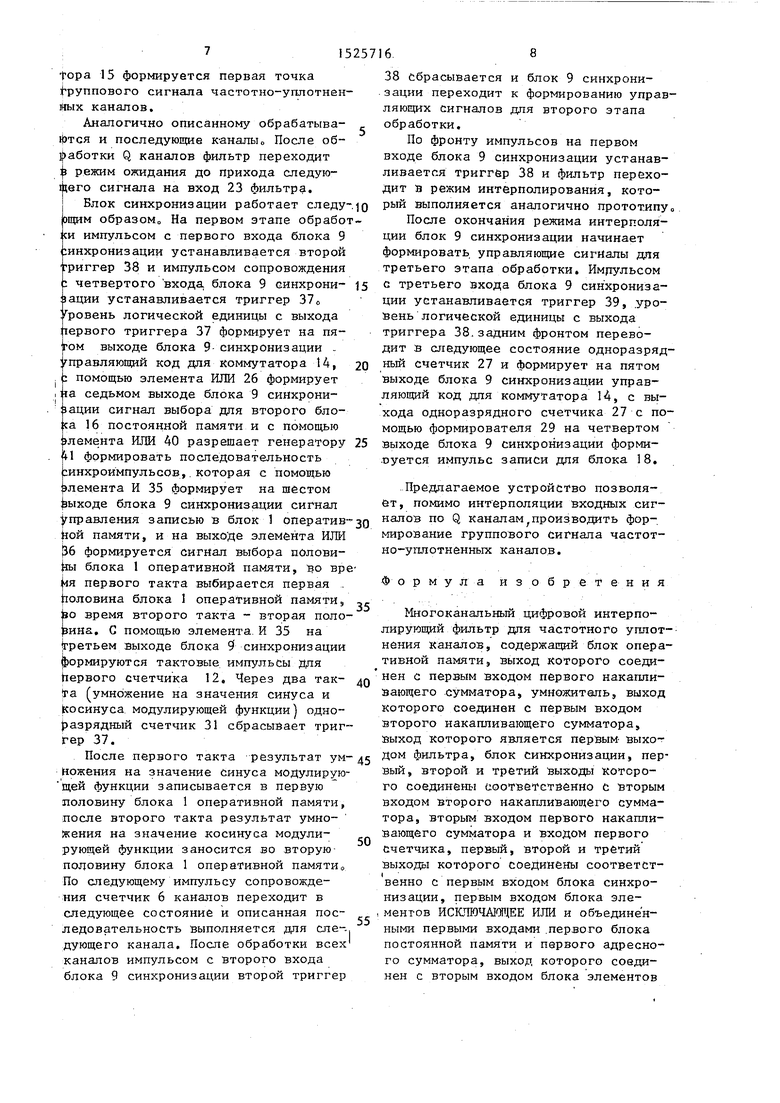

На фиг.1 приведена структурная схема фильтра; на фиг.2 - структур-, ная схема блока синхронизации

Многоканальный цифровой интерполирующий фильтр для частотного уплот- нения каналов содержит блок 1 оперативной памяти, первый накапливающий сумматор 2, умножитель 3, второй накапливающий сумматор 4, первый блок постоянной памяти, счетчик 6 кана- jJoB, блок 7 элементов ИСКЛЮЧАЮ1ЦЕЕ ИЛИ, первый адресный сумматор 8, .блок 5 синхронизации, элемент ИЛИ 10, счетчик II выборки, первый и второй счетчики 12 и 13, коммутатор 14, тре ий накаппивающий сумматор 15, второ ()лок 16 постоянной памяти, второй ад еьный сумматор 17, блок 18 памяти щреса, элемент И 19, элемент ИСКШО- ЧАЮЩЕЕ ИЛИ 20, входа 21-23 и выходы 4 и 25о

i Блок 9 синхронизации образуют лемент ИЛИ 26, счетчик 27, формиро- атели 28-30, счетчик 31, элемент h 32, элемент ИЛИ 33, элементы И 34 |я 35, элемент ИЖ 36, триггеры 37-39 Элемент ИЛИ 40 и генератор 41 синх- |роимпульсов.

Частотное уплотнение каналов осуществляется следующим образом

Из входных сигналов с граничной частотой F., которая связана с частотой дискретизации выражением Fgjj/M, по каждому каналу формиру- ются квадратурные составляющие сигнала путем домножения на множители вида sin(2 r OTn Fc/2) 31п{2ЧГум)5 cos(2 iv-bTn Fc/2) cos().

Фильтр работает следующим образом

При появлении высокого уровня на входе 23 фильтра счетчик 11 выборки переключается в следующее состояние, блок 9 синхронизации формирует сигналы, необходимые для работы устройства, и производится формирование квадратурных составляющих путем умножения входных выборок на значения синуса и косинуса модулирующей функцин, которое выполняется следующим образом. С входа 22 через элемент : ИЛИ 10 импульс сопровождения проходит на вход счетчика 6 каналов и переводит его в следующее состояние, .код с первого выхода счетчика 6 каналов поступает на первый адресный вход блока 1 оперативной памяти, на адресный вход блока 1В и через элемент И 19, на первый вход которого поступает высокий уровень с входа 23, на второй вход второго адресного сумматора 17, на первый вход которого поступает сигнал с. выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, на первый вход которого поступает высокий уровень с входа 23, а на его второй вход поступает значение младшего из разрядов с выхода элемента И 19(, Второй адресный сумматор 17 последовательно формирует коды адреса, поступающие на вход блока 16 постоянной памяти, из которого последовательно считываются значения косинуса и синуса модулирующей функции и поступают на второй вход умножителя 3, на первый вход которого через коммутатор 14 с входа 21 фильтра поступает значение выборки входного сигнала На управляющий вход комму- - татора 14 поступает управляющий код с седьмого выхода блока 9 синхронизации, в результате чего к выходу коммутатора 14 подключается его первый вход.

В первом такте умножений на значние косинуса модулирующей функции результат записывается в первую полвину блока 1 оперативной памяти по адресу, который формируется на втором адрресном входе первым адресным сумматором 8 через блок 7 под управлением сигналов, поступающих с шестго выхода блока 9 синхронизациио Во втором такте умноженный на значение синуса модулирующей функции результат записывается во вторую половину блока 1 оперативной памяти (первую/ вторую половину блока оперативной памяти 1 переключает импульс, поступающий на управляющий вход .блока 1 оперативной памяти с шестого выхода блока 9 синхронизации по адресу, сформированному на втором адресном входе адресным сумматором 8.

С приходом следующего импульса сопровождения на вход 22 фильтра

счетчик 6 каналов переключается в . следующее состояние и происходит обработка информации следующего канала аналогично описанномуо

После занесения в блок 1 оперативной памяти значений квадратурных сос- тавлянлцих по всем каналам высокий уровень с входа 23 фильтра снимается

с-

15257166

обработка считанной из блока 1 оперативной памяти информации в соответствии с описанным.

После считывания из блоАа 1 оперативной памяти N/L выборок и o6pia6oT- ки их аналогично описанному на выходе накапливающего сумматора 2 формируется код проинтерполированной

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Многоканальный перестраиваемый цифровой фильтр | 1988 |

|

SU1569955A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано в устройствах многоканальной связи с цифровой обработкой сигнала. Цель - расширение области применения. Изобретение позволяет дополнительно формировать групповой сигнал частотно-уплотненных каналов за счет того, что в известный фильтр, содержащий блок 1 оперативной памяти и блок 5 постоянной памяти, накапливающие сумматоры 2 и 4, первый адресный сумматор 8, умножитель 3, счетчик 11 выборки и счетчик 6 канала, блок 7 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй счетчики 12, 13, блок 9 синхронизации и элемент ИЛИ 10, введены второй блок 16 постоянной памяти, третий накапливающий сумматор 15, коммутатор 14, второй адресный сумматор 17, блок 18 памяти адреса, элементы И 19 и ИСКЛЮЧАЮЩЕЕ ИЛИ 20. 2 ил.

и фильтр переходит в режим интерполи- ю выборки по первому каналу на третьем выходе счетчика 12 формируется импуль.с, который поступает на первый вход блока 9 синхронизации, который формирует управляющие сигналы третьрования.

Режим интерполирования дпя каждой квадратурной составляющей сигнала выполняется в фильтре следующим образом. С третьего выхода блока 9 синх-15 его этапа обработки.

ронизации на вход первого счетчика 12 поступают тактовые импульсы, на первом выходе данного счетчика последовательно формируются коды, которые поступают на второй вход первого адресного сумматора 8, на первый вход которого поступает код с выхода счетчика 11 выборки

В первом такте информация из блок 1 оперативной памяти считывается по адресу, формируемому на выходе адресного сумматора 8, и поступает на вход второго накапливающего сумматора 2. Во время второго такта на вход управления блока 7 поступает уровень логической единицы с третьего выхода первого счетчика 12 и информация считывается из 1 .оперативной памяти по преобразованному блоком 7 адресу и суммируется во втором накап ливающем сумматоре 2о

После двух тактов считывания код выхода второго накапливающего сумматора 2 через второй вход коммутатора 14 поступает на первый вход умножителя 3, на второй вход которого поступает значение коэффициента импульсной характеристики фильтра. Адрес дпя считывания коэффициента им- .пульсной характеристики фильтра из первого блока 5 постоянной памяти поступает с первого выхода первого счетчика 12. Результат умножения с выхода у1 тожителя 3 заносится в накапливающий сумматор 4 по импульсам, поступающим на его управляющий вход с второго выхода блока 9 синхронизации о Импульсы с первого выхода бло- ка 9 синхронизации поступают на управляющий вход накапливающего сумматора 4 и обнуляют его.

Первый счетчик 12 переключается в следующее состояние, и во время следуюЕсих двух тактов выполняется

ем выходе счетчика 12 формируется импуль.с, который поступает на первый вход блока 9 синхронизации, который формирует управляющие сигналы треть0

5

5

На третьем этапе- на пятом выходе Y9 блока 9 синхронизации формируется управлянндий код дпя -коммутатора 14, в результате чего к его выходу подключается его третий вход, на седьмом выходе формируется сигнал выбора второго блока 16 постоянной памяти, на четвертом выходе формируется импульс, который через элемент ИЛИ 10 переводит в следующее состояние счетчик 6 каналов и формирует канал записи в блок 18 памяти адреса.

Проинтерполированные выборки с вы- 0 хода накапливающего сумматора. 4 через третий вход коммутатора 14 поступают на первьй вход умножителя 3, на второй вход которого поступают значения синуса и косинуса моделирующей функции из блока 16 постоянной памяти Адрес считываемого из блока 16 посто- янйой памяти значения формируется на выходе второго адресного сумматора .17, на второй вход которого поступает через элемент И 19 код с первого выхода счетчика 6 каналов, на третий вход второго адресного сумматора 17 поступает информация с выхода блока 18 памяти адреса, где хранится код адреса, который был использован при обработке предьщущей выборки Код адреса с выхода второго адресного сумматора 17 поступает на вход второго блока 16 постоянной памяти, после чего этот код заносится в ту же ячейку блока 18 памяти адреса, из которой был считано

0

5

0

С выхода умножителя 3 результат умножения заносится в третий накапливающий сумматор 15, затем аналогично описанному обрабатывается вторая квадратурная составляющая, В результате на выходе накапливающего сумма-

topa 15 формируется первая точка Группового сигнала частотно-угшотнен- Иых каналов.

Аналогично описанному обрабатыва- Йтся и последующие каналы После об- |)аботки Q каналов фильтр переходит режим ожидания до прихода следуго- iero сигнала на вход 23 фильтра. I Блок синхронизации работает следуощим образоМо На первом этапе обработ 1СИ импульсом с первого входа блока 9 синхронизации устанавливается второй триггер 38 и импульсом сопровождения : четвертого входа, блока 9 синхрони- устанавливается триггер 37о Уровень логической единицы с выхода первого триггера 37 формирует на пятом выходе блока 9- синхронизации . управляющий код для коммутатора 14, с помощью элемента ИЛИ 26 формирует I на седьмом выходе блока 9 синхронизации сигнал выбора дпя второго бло- :са 16 постоянной памяти и с помощью ;)лемента ИЛИ 40 разрешает генератору 41 формировать последовательность |:инхроимпульсов,. которая с помощью лемента И 35 формирует на шестом Ьыходе блока 9 синхронизации сигнал управления записью в блок 1 оперативЬой памяти, и на выходе элемента ИЛИ 36 формируется сигнал выбора полови- блока 1 оперативной памяти, зо вр 1Я первого такта выбирается первая

Головина блока 1 оперативной памяти.

bo время второго такта - вторая поло- ина, С помощью элемента. И 35 на (третьем выходе блока Sf синхронизации формируются тактовые импульсы дпя Ьервого счетчика 12. Через два так- га (умножение на значения синуса и Косинуса модулирующей функции) одно- |зазрядный счетчик 31 сбрасывает триггер 37.

После первого такта результат ум- йожения на значение синуса модулирую- щей функции записывается в первую половину блока 1 оперативной памяти, после второго такта результат умножения на значение косинуса модули- рующей функции заносится во вторую- половину блока 1 оперативной памятио По следующему импульсу сопровождения счетчик 6 каналов переходит в следующее состояние и описанная последовательность выполняется для еле-дующего канала. После обработки всех каналов импульсом с второго входа блока 9 синхронизации второй триггер

о

5

0

5

38 сбрасывается и блок 9 синхронизации переходит к формированию управляющих сигналов для второго этапа обработки.

По фронту импульсов на первом входе блока 9 синхронизации устанавливается триггер 38 и фильтр переходит в режим интерполирования, который выполняется аналогично прототипу,,

После окончания режима интерполяции блок 9 синхронизации начинает формировать, управляющие сигналы дпя третьего этапа обработки. Имдульсом с третьего входа блока 9 синхронизации устанавливается триггер 39, уровень логической единицы с выхода триггера 38,задним фронтом переводит в следующее состояние одноразрядный счетчик 27 и формирует на пятом выходе блока 9 синхронизации управляющий код для коммутатора 14, с выхода одноразрядного счетчика 27 с помощью формирователя 29 на четвертом выходе блока 9 синхронизации форми- .оуется импульс записи для блока 18.

Предлагаемое устройство позволяет, помимо интерполяции входных сигналов по Q каналам,производить формирование группового Сигнала частотно-уплотненных каналов.

Формула изобретения

Многоканальный цифровой интерполирующий фильтр для частотного уплот-- нения каналов, содержащий блок оперативной памяти, выход которого соединен с первым входом первого накапливающего .сумматора, умножитель, выход которого соединен с первым входом второго накапливающего сумматора, выход которого является первым- выходом фильтра, блок синхронизации, первый, второй и третий выходы которого соединены соответственно с вторым входом второго накапливающего сумматора, вторым входом первого накапливающего сумматора и входом первого счетчика, первый, второй и третий выходы которого соединены соответст- венно с первым входом блока синхронизации, первым входом блока эле- , ментов ИСКШОЧА101ЧЕЕ ИЛИ и объединенными первыми входами .первого блока постоянной памяти и первого адресного сумматора, выход которого соединен с вторым входом блока элементов

ИСКПЮЧАЩЕЕ ИЛИ, выход которого соединен с первым входом блока оперативной памяти, счетчик выборки, вход которого объединен с третьим входом блока синхронизации и является входом задания режима работы фильтра, выход счетчика выборки соединен с вторым входом первого адресного сумматора, элемент ИЛИ, выход которого соединен с входом счетчика каналов, первый и второй выходы которого соединены соответственно с вторым входом блока оперативной памяти и входом второго счетчика, первый и второй выходы которого соединены .соответственно с четвертым входом блока синхронизации и вторым входом первого блока постоянной памяти, выход которого соединён с первым входом умножителя, четвертый выход блока синхронизации соединен с первым входом элемента ИЛИ, второй вход которого является синхронизирующим входом фильтра, отличающийся тем, что, с целью расширения области применения фильтра за счет формирования выходного группового.сигнала, в него, введены коммутатор, третий накаплийа- ющий сумматор, второй блок постоянной памяти, блок памяти адреса, второй адресный сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, первый вход которого объединен с первым входом эле-- мента ИСКЛЮЧАЮЩЕЕ ИЛИ и подключен к входу задания режима работы цифрового филътра, второй вход элемента И объединен с первым входом блока памяти адреса и подключен к первому выходу счетчика каналов, выход элемента И соединен с первым входом второго адресного сумматора и вторым входом элемента ИСЮТЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым .входом второго адресного сумматора, выход которого соединен с первым входом второго блока постоянной памяти ..и вторым входом блока памяти адреса, выход и Третий вход которого подключены соответственно к третьему входу второго v адресного сумматора и четвёртому выходу блока синхронизации, питый вход и пятый выход блока синхрбнизации подключены соответственно к синхронизирующему входу фильтра и первому входу коммутаторе., выход которого со динен с вторым входом умножителя, вт рой и третий входы коммутатора подключены к выходам.соответственно первого и второго накапливающих сумматоров, четзер.тый вход коммутатора является информационным входом фильтра, шестой выход блока синхронизации соединен с третьим входом блока оперативной памяти и первым : входом.третьего накапливающего сумматора, второй вход которого объединен с четвертым входом блока оперативной памяти и подключен к выходу умножителя, выход третьего накапливающего сумматора является вторым выходом фильтра,,седьмой выход блока синхронизации соединен с третьим входом первого блока постоянной памяти и вторым входом второго блока постоянной памяти, выход которого подключен к первому входу умножителя«

фиг. 2

| Многоканальный цифровой интерполирующий фильтр | 1986 |

|

SU1401480A1 |

Авторы

Даты

1989-11-30—Публикация

1987-08-28—Подача