г /

Изобретение относится к импульсной технике и может быть использовано для контроля импульсных последовательностей цифровых блоков.

Целью изобретения является расширение функциональных возможностей путем фиксации характера и местоположения искажений, а также осуществления контроля импульсных последовательностей с непостоянным периодом повторения.

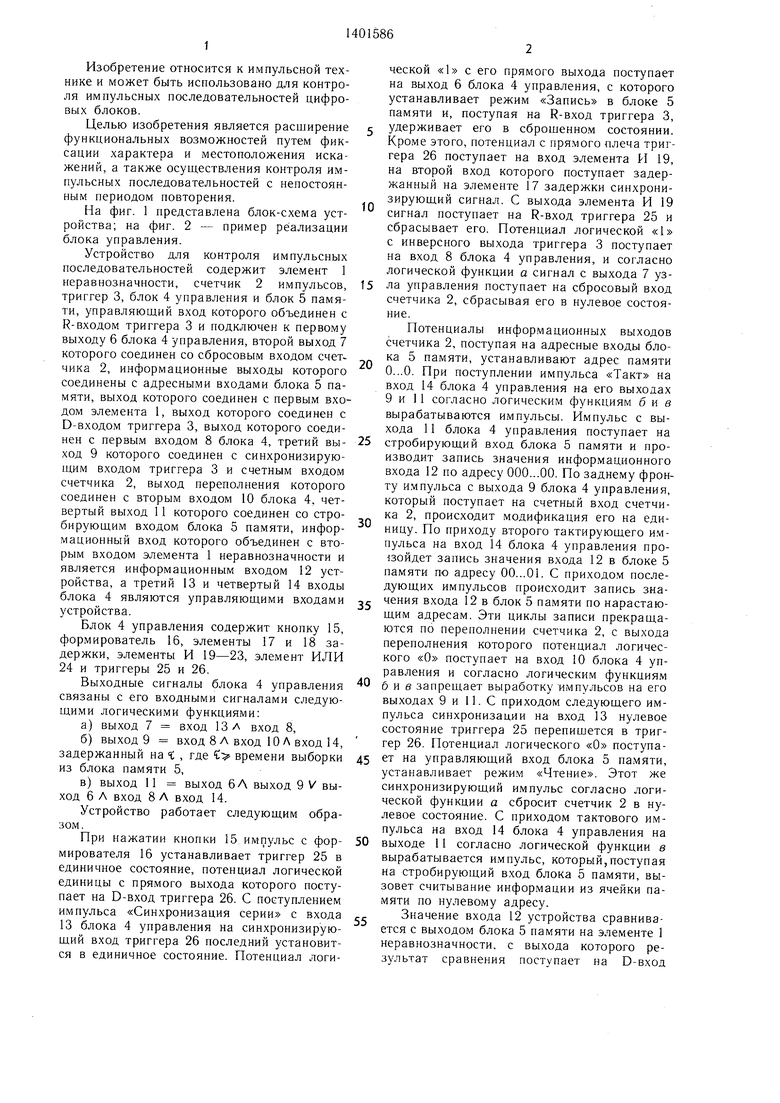

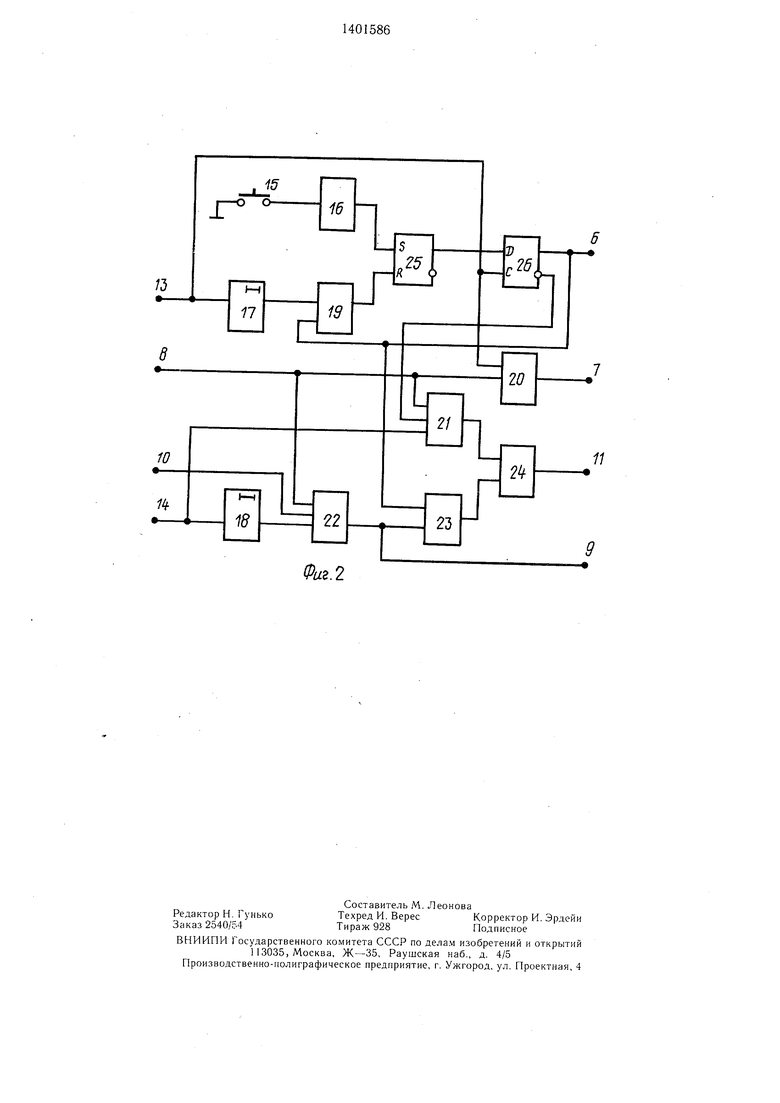

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - пример реализации блока управления.

Устройство для контроля импульсных последовательностей содержит элемент 1 неравнозначпости, счетчик 2 импульсов, триггер 3, блок 4 управления и блок 5 памяти, управляющий вход которого объединен с R-входом триггера 3 и подключен к первому выходу 6 блока 4 управления, второй выход 7 которого соединен со сбросовым входом счетчика 2, информационные выходы которого соединены с адресными входами блока 5 памяти, выход которого соединен с первым входом элемента 1, выход которого соединен с D-входом триггера 3, выход которого соединен с первым входом 8 блока 4, третий выход 9 которого соединен с синхронизирующим входом триггера 3 и счетным входом счетчика 2, выход переполнения которого соединен с вторым входом 10 блока 4, четвертый выход 11 которого соединен со стро- бирующим входом блока 5 памяти, информационный вход которого объединен с вторым входом элемента 1 неравнозначности и является информационным входом 12 устройства, а третий 13 и четвертый 14 входы блока 4 являются управляющими входами устройства.

Блок 4 управления содержит кнопку 15, формирователь 16, элементы 17 и 18 задержки, элементы И 19-23, элемент ИЛИ 24 и триггеры 25 и 26.

Выходные сигналы блока 4 управления связаны с его входными сигналами следующими логическими функциями:

а)выход 7 вход 13 А вход 8,

б)выход 9 вход 8 Л вход 10 Л вход 14, задержанный на t , где С времени выборки из блока памяти 5,

в)выход 11 выход 6 Л выход 9 V выход 6 Л вход 8 Л вход 14.

Устройство работает следующим образом.

При нажатии кнопки 15 импульс с формирователя 16 устанавливает триггер 25 в единичное состояние, потенциал логической единицы с прямого выхода которого поступает на D-вход триггера 26. С поступлением импульса «Синхронизация серии с входа 13 блока 4 управления на синхронизирующий вход триггера 26 последний установится в единичное состояние. Потенциал логи0

5

0

5

0

5

0

5

0

5

ческой «1 с его прямого выхода поступает на выход 6 блока 4 управления, с которого устанавливает режим «Запись в блоке 5 памяти и, поступая на R-вход триггера 3, удерживает его в сброшенном состоянии. Кроме этого, потенциал с пря.мого плеча триггера 26 поступает на вход элемента И 19, на второй вход которого поступает задержанный на элементе 17 задержки синхронизирующий сигнал. С выхода элемента И 19 сигнал поступает на R-вход триггера 25 и сбрасывает его. Потенциал логической «1 с инверсного выхода триггера 3 поступает на вход 8 блока 4 управления, и согласно логической функции а сигнал с выхода 7 узла управления поступает на сбросовый вход счетчика 2, сбрасывая его в нулевое состояние.

Потенциалы информационных выходов счетчика 2, поступая на адресные входы блока 5 памяти, устанавливают адрес памяти 0...0. При поступлении импульса «Такт на вход 14 блока 4 управления на его выходах 9 и 11 согласно логическим функциям б к в вырабатываются импульсы. Импульс с выхода 11 блока 4 управления поступает на стробирующий вход блока 5 памяти и производит запись значения информационного входа 12 по адресу 000...00. По заднему фронту и.мпульса с выхода 9 блока 4 управления, который поступает на счетный вход счетчика 2, происходит модификация его на единицу. По приходу второго тактирующего импульса на вход 14 блока 4 управления про- 13ойдет запись значения входа 12 в блоке 5 памяти по адресу 00...01. С приходом последующих импульсов происходит запись значения входа 12 в блок 5 памяти по нарастающим адресам. Эти циклы записи прекращаются по переполнении счетчика 2, с выхода переполнения которого потенциал логического «О поступает на вход 10 блока 4 управления и согласно логическим функциям 6 и и запрещает выработку импульсов на его выходах 9 и 11. С приходом следующего импульса синхронизации на вход 13 нулевое состояние триггера 25 перепищется в триггер 26. Потенциал логического «О поступает на управляющий вход блока 5 памяти, устанавливает режим «Чтение. Этот же синхронизирующий импульс согласно логической функции а сбросит счетчик 2 в нулевое состояние. С приходом тактового импульса на вход 14 блока 4 управления на выходе 11 согласно логической функции в вырабатывается импульс, который,поступая на стробирующий вход блока 5 памяти, вызовет считывание информации из ячейки памяти по нулевому адресу.

Значение входа 12 устройства сравнивается с выходом блока 5 памяти на элементе 1 неравнозначности, с выхода которого результат сравнения поступает на D-вход

триггера 3. Наряду с этим, тактовый импульс на входе 14 блока 4 управления, согласно логической функции б вырабатывает импульс задержки на выходе 9, который поступает на счетный вход счетчика 2, модифицируя его на единицу, и синхронизирующий вход триггера 3, фиксируя результат сравнения значения выхода блока 5 памяти с значением входа 12 устройства.

Если данные совпадают, то триггер 3 остается в нулевом состоянии и цикл чтения производится по следующим адресам, а если нет, то триггер 3 устанавливается в единичное состояние. Потенциал логического «О с его выхода поступает на вход 8 блока 4 управления и запрещает согласно логическим функциям а, б и 8 выработку импульсов на выходах 7, 9 и 11 блока 4 управления.

Таким образом прекращаются считывание информации из блока 5 памяти, сброс и модификация счетчика 2. Содержимое счетчика, уменьщенное на единицу, указывает на местоположение ошибки в серии импульсов, а значение выхода блока памяти указывает на характер искажения, т. е. если значение выхода блока 5 памяти равно единице, то произошла потеря импульса, а если нулю, то прошел ложный импульс.-Из этого состояния устройство можно вывести нажатием кнопки 15 блока 4 управления. Произойдет запись серии в блок 5 памяти, а затем производится аналогичный контроль.

Формула изобретения

1. Устройство для контроля импульсных последовательностей, содержащее элемент неравнозначности, счетчик импульсов, отличающееся тем, что, с целью расширения функциональных возможностей путем фиксации характера и местоположения искажении, в него введены триггер, блок управления и блок памяти, управляющий вход которого объединен с К-входом триггера и подключен к первому выходу блока управления, второй выход которого соединен со сбросовым входом счетчика импульсов, информационные выходы которого соединены с адресными входами блока памяти, выход которого соединен с первым входом :-)ле.мен- та неравнозначности, выход которого соединен с D-входом триггера, выход которого

5

соединен с первым входом блока управления, третий выход которого соединен с синхрони зирующим входом триггера и счетным входом счетчика и.мпульсов, выход перенолнения которого соединен с вторым входом б.чо- ка управления, четвертый выход которой соединен со стробирующим входом б.;1ока памяти, информационный вход которого объединен с вторым входом элемента неравноQ значности и является информационным входом устрой-ства, а третий и четвертый входы блока управления - управляющими входами устройства.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит первый и второй триггеры, первый, второй, третий, четвертый и пятый элементы И, элемент ИЛИ, первый и второй элементы задержки, формирователь импульсов и кнопку, соединенную с входом формирователя, выход ко0 торого соединен с S-в.ходом первого триггера, R-вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом первого элемента задержки, вход которого соединен с третьим входом блока управления, с первым входом второго элемента И, синхронизирующим входом второго триггера, прямой выход которого соединен с вторым входом первого элемента И, с первым входом третьего элемента И и первым выходом блока управления,

0 второй выход которого соединен с выходом второго элемента И, второй вход которого соединен с нервы.ми входами четвертого и пятого элементов И и с первым входом блока управления, второй вход которого соединен с вторым входо.м четвертого элемен5 та И, третий вход которого соединен с выходом второго элемента задержки, вход которого соединен с вторым входом пятого элемента И и с четвертым в.ходом блока управления, третий выход которого соединен с

Q выходом четвертого элемента И и с вторым входом третьего элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, третий вход которого соединен с инверсным выходом второготриг5 гера, D-вход которого соединен с выходом первого триггера, при этом выход элемента ИЛИ соединен с четвертым выходом блока управления.

5

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для управления доступом к памяти | 1985 |

|

SU1282147A1 |

| УСТРОЙСТВО ДЛЯ РАЗГРАНИЧЕНИЯ ДОСТУПА ПОЛЬЗОВАТЕЛЕЙ К РАЗДЕЛАМ ТЕКСТОВЫХ ДОКУМЕНТОВ | 2001 |

|

RU2239866C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУЧЕНИЕМ ОЦЕНКИ КАЧЕСТВА ЗНАНИЙ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248610C2 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1383326A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

| Устройство для ввода информации | 1990 |

|

SU1709294A1 |

| Устройство для информационного поиска | 1986 |

|

SU1399769A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Устройство для приема и передачи информации | 1991 |

|

SU1833871A1 |

Изобретение относится к импульсной технике и может быть использовано для контроля импульсных последовательностей цифровых блоков. Цель изобретения - расширение функциональных возможностей устройства - достигается путем фиксации характера и .местоположения искажений, а также осуществления контроля импульсных последовательностей с непостоянным периодом повторения. Для этого в устройство дополнительно введены триггер 3, блок 4 управления и блок 5 памяти. Устройство также содержит элемент 1 неравнозначности, счетчик 2 импульсов. На чертеже также показаны входы и выходы блока управления. В состав этого блока в.ходят один формирователь, два элемента задержки, пять элементов И, один элемент ИЛИ и два триггера. Функциональная схема блока управления приводится в описании изобретения. 1 з. п. ф-лы, 2 ил.

| Устройство контроля импульсных последовательностей | 1978 |

|

SU790231A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обнаружения искажений в последовательности импульсов | 1980 |

|

SU911715A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-07—Публикация

1986-04-22—Подача