со.

о

05 О5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок при передаче кодов | 1987 |

|

SU1509902A2 |

| Устройство для обнаружения ошибок при передаче кодов | 1989 |

|

SU1615723A2 |

| Устройство для обнаружения ошибок при передаче кодов | 1983 |

|

SU1091211A1 |

| Устройство для обнаружения и исправления ошибок в блоках вычислительной машины | 1982 |

|

SU1111169A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

14)

1

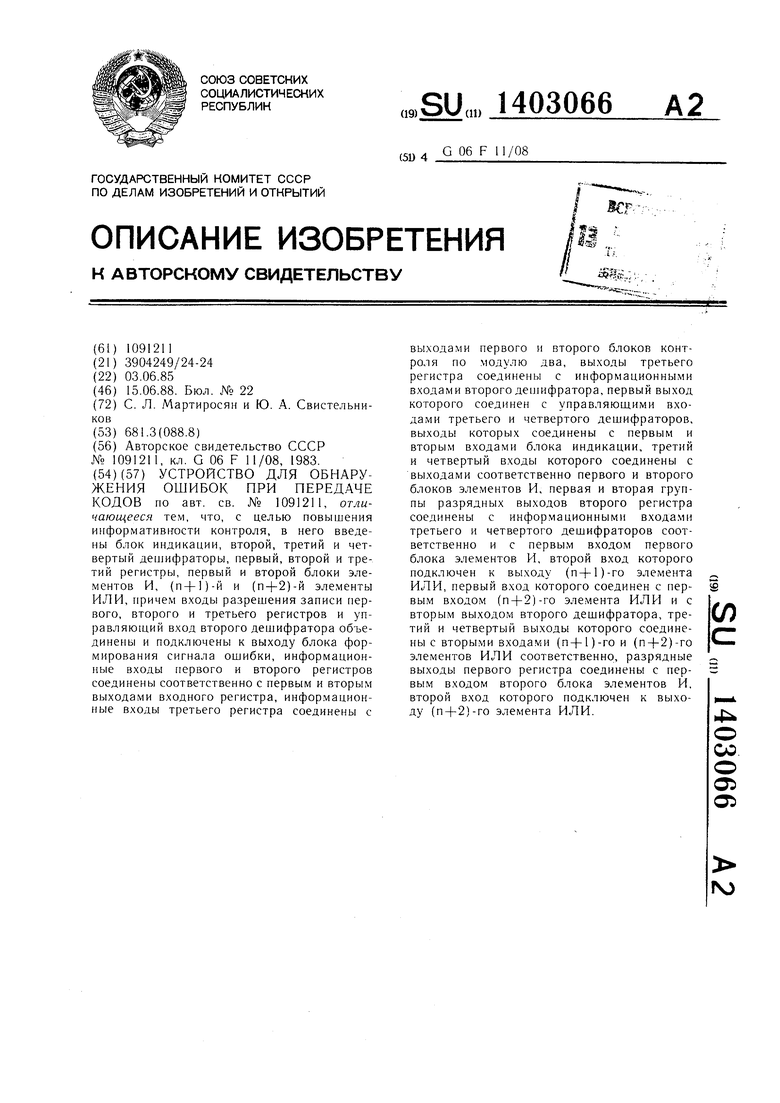

Изобретение относится к вычислительной технике, может быть использовано в устройствах автоматизированного контроля узлов передачи информации и является усовершенствованием изобретения по авт. св. № 1091211.

Цель изобретения - повышение информативности контроля.

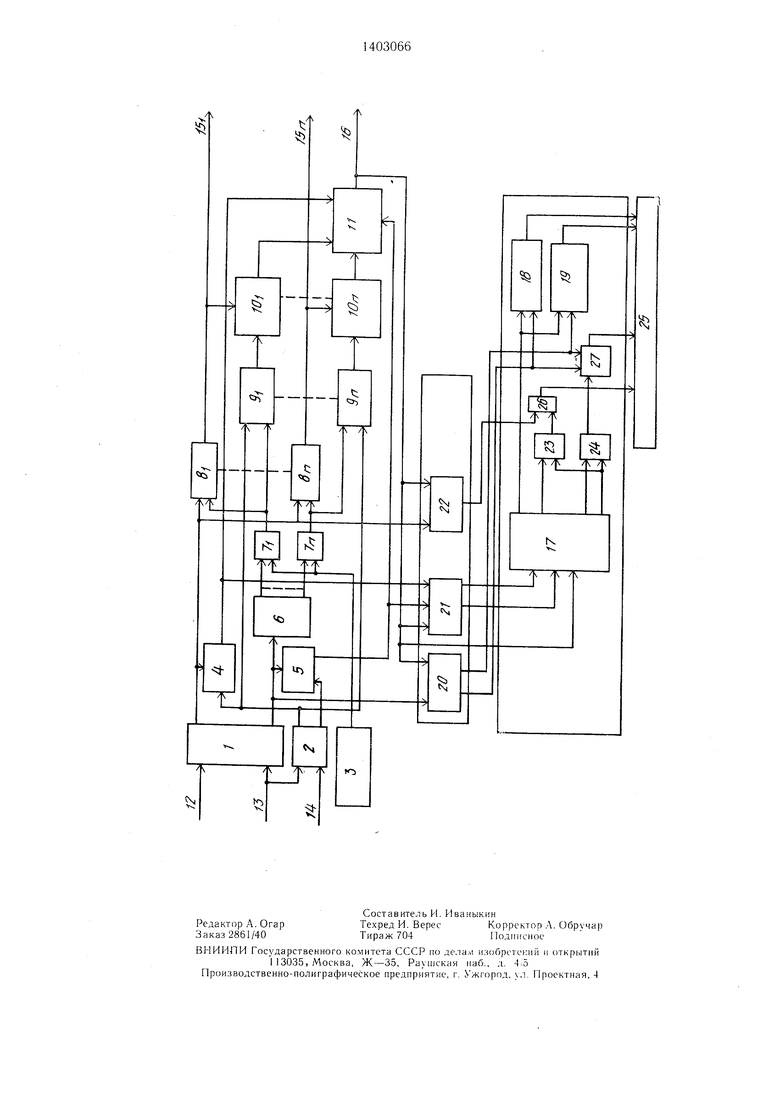

На чертеже представлена структурная схема устройства для обнаружения ошибок при передаче кодов.

Устройство содержит входной регистр 1, регистр 2 контрольных разрядов, блок 3 управления параллельной записью, блоки 4 и 5 контроля по модулю два, дешифратор 6, элементы ИЛИ 7.1-7.п, входные регистры 8.1-8.П, триггеры 9.1-9.п, блоки 10.1 -10.п контроля на четность, блок 11 формирования сигнала ошибки, информационный вход 12, стробируюший вход 13, вход 14 контрольных разрядов, информационные выходы 15.1 - 15.П, выход 16 сигнала ошибки, дешифраторы 17-;19, регистры 20-22, элементы ИЛИ 23 и 24, блок 25 индикации и блоки 26 и 27 элементов И.

Устройство работает следующим образом.

Информация, поступающая на входной регистр 1 с входа 12 информации, и контрольные разряды, поступающие на регистр 2 контрольных разрядов с входа 13 контрольных разрядов, записываются в регистры 1 и 2 по стробу, поступающему со стробируюпдего входа 13. Информация побайтно контролируется в блоках 4 и 5 контроля по модулю два. Результат контроля с выходов блоков 4 и 5 поступает на входы регистра 21 и блока 11 формирования сигнала ошибки, выход которого является выходом 16 сигнала ошибки уст

10

15

03066

2

ройства. Первый байт информации переписывается в выходной регистр 8, а соответствующий е.му контрольный разряд -- в триггер 9 по сигналу, поступающему через элемент ИЛИ 7 с выхода дешифратора 6, на вход которого поступает второй байт информации. В устройстве предусмотрена параллельная запись первого байта информации и его контрольного разряда во все регистры 8 и триггеры 9 по сигналу с блока 3 управления параллельной записью. Информация на выходах регистров 8 контролируется в блоках 10 контроля на четность. Результат контроля с выходов блоков 10 поступает на входы блока 11 формирования сигнала ошибки.

Если устройством обнаружена ошибка, то блок 11 формирования сигнала ошибки формирует сигнал, который запись вает первый и второй байты информации и результат их контроля блоками 4 ц 5 в первый, второй и третий регистры соответственно и стробирует дешифратор 17.

Если ошибка обнаружена блоком 4 контроля по модулю два, или блоком 5 контроля по модулю два, или блоками 4 и 5 одновременно, то дешифратор 17 формирует на своем выходе сигналы, разрешающие прохождение на блок 25 индикации первого байта, или второго байта, или одновременно первого и второго байтов информации соответственно.

Если ощибка обнаружена блоком 10 контроля на четность, то дешифратор 17 формирует на своем выходе сигнал, который стробирует дешифраторы 18 и 19. С выходов дешифраторов 18 и 19 информация о номере платы и номере регистра в плате, в которых произошел отказ, поступает на блок 25 индикации.

20

25

30

| Устройство для обнаружения ошибок при передаче кодов | 1983 |

|

SU1091211A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-15—Публикация

1985-06-03—Подача