j;;

о со о

Oi

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для преобразования кода системы остаточных классов в десятичный код | 1984 |

|

SU1167600A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

Изобретение относится к вычислительной технике и может быть использовано в составе средств защиты от ошибок при обмене информацией, а также в аппаратуре передачи данных. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности коррекции принятой последовательности символов. Устройство содержит регистр I сдвига, три сумматора 2-4 но модулю, три блока 5-7 преобразования в дополнительный код, два мультиплексора 8, 9, блок 10 умножения, два счетчика И, 12, два регистра 13, 14, шифратор 15, блок 16 элементов И, блок 17 сравнения, информационный вход 18, информационный выход 19, вход 20 начальной установки, пять входов 2I-25 синхронизации, два стробирующих входа 26, 27. Положительный эффект обусловлен введением блоков преобразования в дополнительный код, счетчиков, мультиплексоров, регистров, блока элементов И и заключается в вычислении истинного значения искаженной разрядной цифры. 2 ил. S

/7

Изобретение относится к вычислительной технике и может быть иснользовано в составе средств защиты от ошибок нри обмене информацией, а также в аппаратуре передачи данных,

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности коррекции принятой последовательности символов.

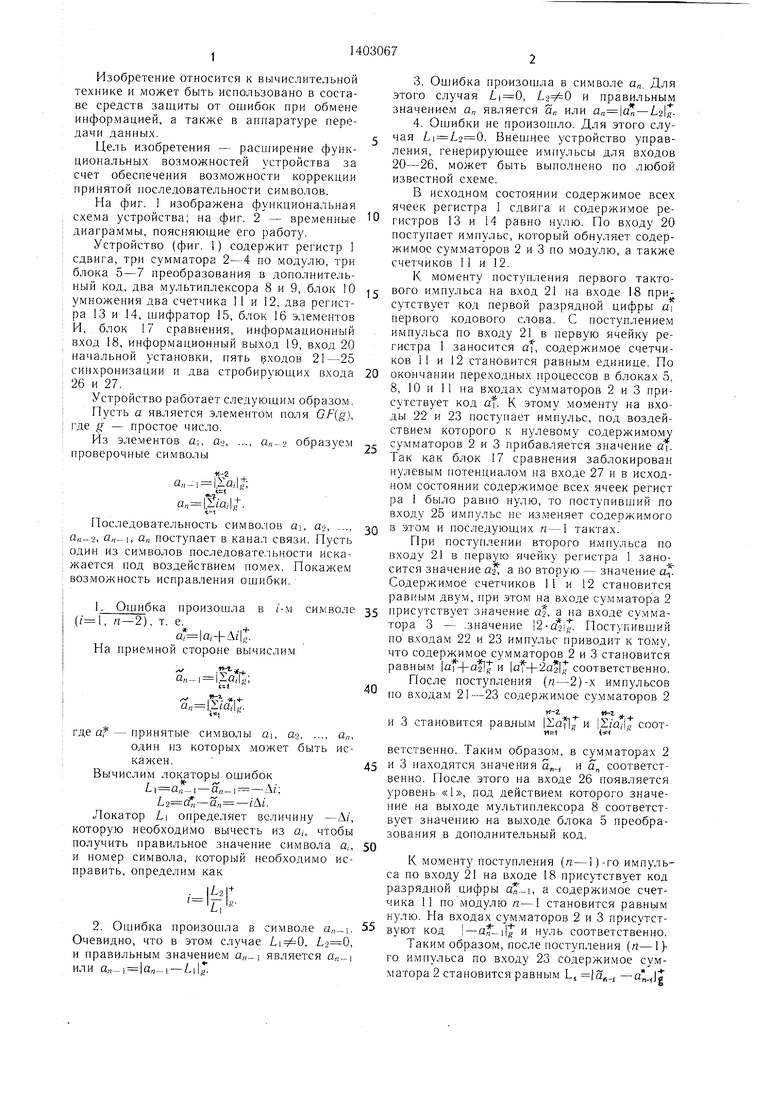

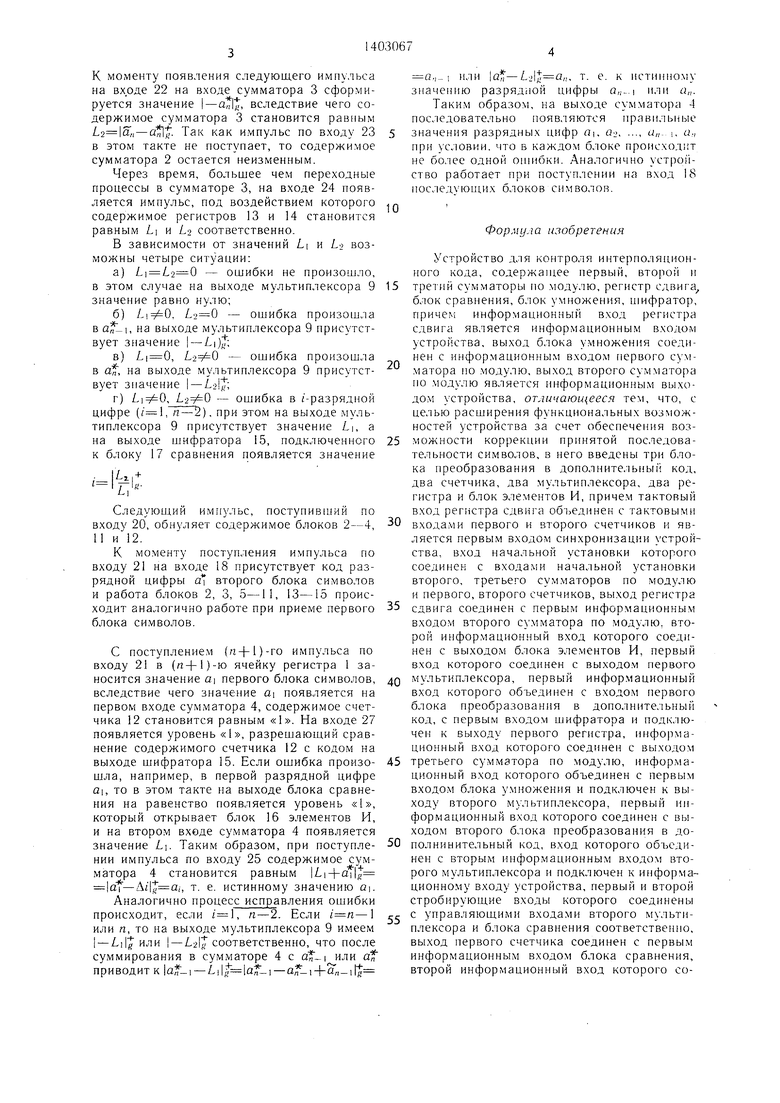

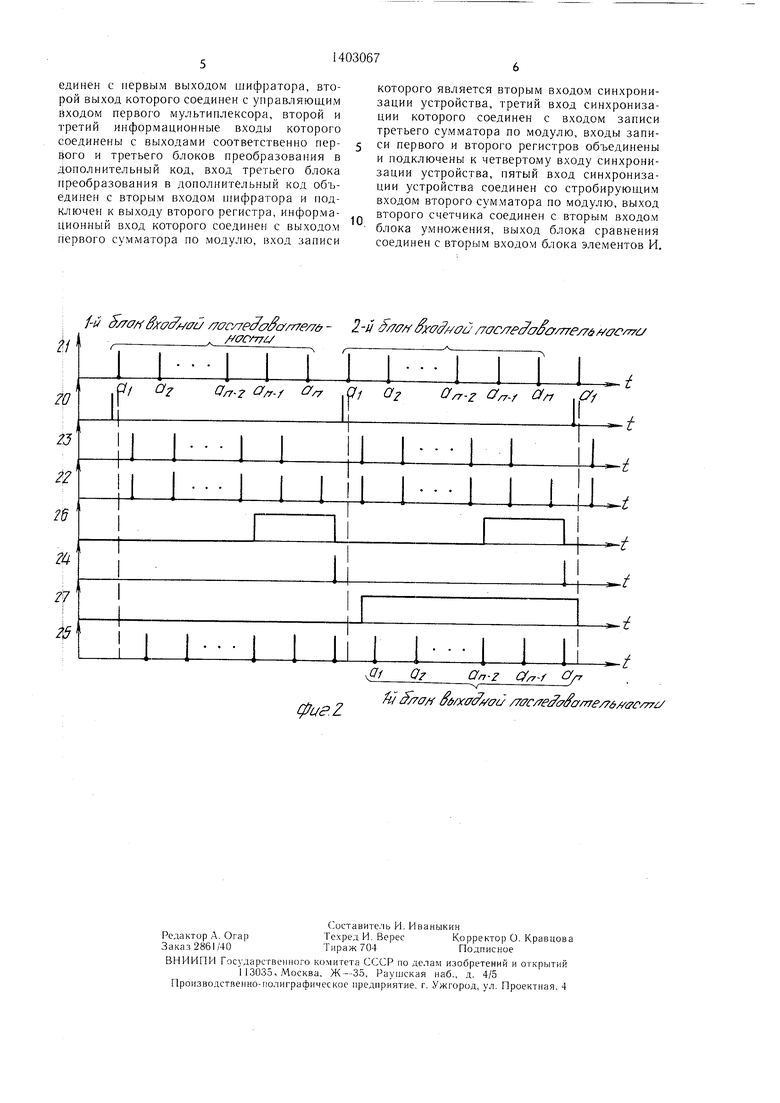

На фиг. изображена функциональная схема устройства; на фиг. 2 - временные диаграм.мы, поясняющие его работу.

Устройство (фиг. 1) содержит регистр I сдвига, три сумматора 2-4 по модулю, три блока 5-7 преобразования в дополнительный код, два мультиплексора 8 и 9, блок 10 умножения два счетчика 11 и 12, два регистра 13 и 14, шифратор 15, блок 16 элементов И, блок 17 сравнения, информационный вход 18, информационный выход 19, вход 20 начальной установки, пять входов 21-25 синхронизации и два стробирующих входа 26 и 27.

Устройство работает следующим образом.

Пусть а является элементом поля GF(g), где - простое число.

Из элементов а-,, а, ..., а„ образуе.м проверочные символы

и-г a,,-i.Za,

a,,|S,|+.

Последовательность CHMBOJFOB ai, 02, .... , «H-i, an поступает в канал связи. Пусть один из символов последовательности искажается под воздействием помех. Покажем возможность исправления ошибки.

,+ На приемной стороне вычислим

На„- 1 |,2о;,-(;;;

itf;. |Ч- a,,,.

где аг - принятые символы QI, 02,

а„,

один из которых .может быть искажен. Вычислим локаторы ошибок

,, -Д/;

(Д/.

Локатор LI определяет величину -Аг, которую необходимо вычесть из а,, чтобы получить правильное значение символа а,., и номер символа, который необходимо исправить, определи.м как

. Аг 2. Ошибка произошла в символе a,,i. 55 Очевидно, что в этом случае , /,, и правильным значением а,,-; является a,,i или |а„ |--А|

г

0

с 0

0

5

0

5

0

5

В исходном состоянии содержимое всех ячеек регистра 1 сдвига и содержимое регистров 13 и 14 равно нулю. По входу 20 поступает импульс, который обнуляет содержимое сумматоров 2 и 3 по модулю, а также счетчиков 11 и 12.

К моменту поступления первого тактового импульса на вход 21 на входе 18 присутствует код первой разрядной цифры ai первого кодового слова. С поступлением импульса по входу 21 в первую ячейку регистра 1 заносится и, содержи1мое счетчиков 11 и 12 становится равным единице. По окончании переходных процессов в блоках 5, 8, 10 и 11 на входах сумматоров 2 и 3 присутствует код а К этому мо.менту на входы 22 и 23 поступает импульс, под воздей- ствие.м которого к нулевому содержимому сумматоров 2 и 3 прибавляется значение О. Так как блок 17 сравнения заблокирован нулевым потенциалом на входе 27 и в исходном состоянии содержимое всех ячеек регист ра 1 было равно нулю, то поступивший по входу 25 импульс не изменяет содержимого в этом и последующих п- тактах.

При поступлении второго импульса по входу 21 в первую ячейку регистра 1 заносится значение а а во вторую - значение о,. Содержимое счетчиков 1 1 и 12 становится равны.м дву.м, при .это.м на входе сумматора 2 присутствует значение aF, а на входе cy.viMa- тора 3 - .значение . Поступивший по входам 22 и 23 импульс приводит к тому, что содержимое сумматоров 2 и 3 становится равным |a -|-aflj и соответственно.

После поступления (п-2)-х импульсов по входам 21-23 содержимое су.мматоров 2

я-г . .

и 3 становится равлым IHaf,, и ,, соот11 1 1(

ветственно. Таки.м образом, в сумматорах 2 и 3 находятся значения а„,, и а„ соответственно. После этого на входе 26 появляется, уровень «1, под действием которого значение на выходе мультиплексора 8 соответствует значению на выходе блока 5 преобразования в дополнительный код.

К моменту поступления (п-1)-го импульса по входу 2 на входе 18 присутствует код разрядной цифры о..-:, а содержимое счетчика 11 по модулю п-1 становится равным нулю. На входах сумматоров 2 и 3 присутствуют код I - и нуль соответственно.

Таким образом, после поступления (п-1 )- го импульса по входу 23 содержимое сумматора 2 становится равным LI |а„. -Qn-Jg

К моменту появления следующего импульса на входе 22 на входе сумматора 3 сформируется значение , вследствие чего содержимое сумматора 3 становится равным . Так как импульс по входу 23 в этом такте не поступает, то содержимое сумматора 2 остается неизменным.

Через время, большее чем переходные процессы в сумматоре 3, на входе 24 появляется импульс, под воздействием которого содержимое регистров 13 и 14 становится равным LI и L соответственно.

В зависимости от значений L и L-2 возможны четыре ситуации:

а), - ошибки не произошло,

в этом случае на выходе мультиплексора 9 значение равно нулю;

б)/,, /, - ошибка произошла в , на выходе мультиплексора 9 присутствует значение )

в)А , /, - ошибка произошла в at, на выходе мультиплексора 9 присутствует значение i -

г), - ошибка в г-разрядной

цифре (, ), при этом на выходе мультиплексора 9 присутствует значение Ь, а

на выходе шифратора 15, подключенного к блоку 17 сравнения появляется значение

, I/- + - /Л«Следуюцдий импульс, поступивший по входу 20, обнуляет содержимое блоков 2-4, 11 и 12.

К мо.менту поступления импульса по входу 21 на входе 18 присутствует код разрядной цифры а второго блока символов и работа блоков 2, 3, 5-11, 13-15 происходит аналогично работе при приеме первого блока символов.

С поступлением (п-|-1)-го импульса по входу 21 в (п-|-1)-ю ячейку регистра 1 заносится значение ai первого блока символов, вследствие чего значение ai появляется на первом входе сумматора 4, содержимое счетчика 12 становится равным «1. На входе 27 появляется уровень «1, разрешающий сравнение содержимого счетчика 12 с кодом на выходе шифратора 15. Если ошибка произо- шла, например, в первой разрядной цифре fli, то в этом такте на выходе блока сравнения на равенство появляется уровень «Ь, который открывает блок 16 элементов И, и на втором входе сумматора 4 появляется значение L. Таким образом, при поступле- НИИ импульса по входу 25 содержимое сумматора 4 становится равным ILi + aTlg |af-Дг| а,, т. е. истинному значению QI.

Аналогично процесс исправления ошибки происходит, если , п-2. Если

или п, то на выходе мультиплексора 9 имеем | -LilJ или J - L2IJ соответственно, что после суммирования в сумматоре 4 с aT-i или а;Г приводит к af-.,,-i

0.,-1 или ,,, т. е. к истинном} значению разрядной цифры или а„. Таким образом, на выходе сумматора 4 последовательно появ. шются правильные значения разрядных цифр Я|, а-, ..., а„- i. о,., при условии, что в каждом блоке проис од т не более одной ошибки. Аналогично устройство работает при поступлении на вход 18 последующих блоков символов.

„

0

5

0

5

о 5 0

5

Формула изобретения

Устройство для контроля интерполяционного кода, содержащее первый, второй и третий сумматоры по .модулю, регистр сдвига блок сравнения, блок умножения, шифратор, причем информационный вход регистра сдвига является информационным входом устройства, выход блока умножения соединен с информационным входом первого сум- .матора по .модулю, выход второго сумматора по .модулю является информационным выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности коррекции принятой последовательности символов, в него введены три блока преобразования в дополнительный код, два счетчика, два .мультиплексора, два регистра и блок элементов И, причем тактовый вход регистра сдвига )единен с тактовыми входа.ми первого и второго счетчиков и является первым ВХОД.ОМ синхронизации устройства, вход начальной установки которого соединен с входами начальной установки второго, третьего сум.маторов по модулю и первого, второго счетчиков, выход регистра сдвига соединен с первым информационны.м входом второго сумматора по модулю, второй информационный вход которого соединен с выходом блока элементов И, первый вход которого соединен с выходо.м первого мультиплексора, первый информационный вход которого объединен с входом первого блока преобразования в дополнительный код, с первьЕм входом шифратора и подключен к выходу первого регистра, информационный вход которого соединен с выходом третьего сумматора по модулю, информационный вход которого объединен с первым входом блока умножения и подключен к выходу второго мультиплексора, первый информационный вход которого соединен с выходом второго блока преобразования в до- полнинительный код, вход которого об ьеди- нен с вторым информационным входом второго мультиплексора и подключен к информационному входу устройства, первый и второй стробирующие входы которого соединены с управляющими входами второго мультиплексора и блока сравнения соответственно, выход первого счетчика соединен с первым информационным входом блока сравнения, второй информационный вход которого соединен с первым выходом шифратора, второй выход которого соединен с управляющим Е ходом первого мультиплексора, второй и третий информационные входы которого соединены с выходами соответственно пер- дого и третьего блоков преобразования в Дополнительный код, вход третьего блока преобразования в дополнительный код объединен с вторым входом пжфратора и подключен к выходу второго регистра, информационный вход которого соединен с выходом первого сумматора по модулю, вход записи

1 й §/7(7/ ffxao fyffi /7((y O /T7f/7ff - 2-Н d/7ffff Cffo ffL f7(7C/7e/ O a 77e/76 iVffC/T/a

W

f

/ c/z

A-/ /r

n

которого является вторым входом синхронизации устройства, третий вход синхронизации которого соединен с входом записи третьего сумматора по модулю, входы записи первого и второго регистров объединены и подключены к четвертому входу синхронизации устройства, пятый вход синхронизации устройства соединен со стробирующим входом второго сумматора по модулю, выход второго счетчика соединен с вторым входом блока умножения, выход блока сравнения соединен с вторым входом блока элементов И.

C/2

/ ,./

t

i

-t

Cff 0/On-z /7-/ Cf

V

fii /7a 6/)((7u /7f7c/7e(7 ame/76//(7C/77

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU398950A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электрическая печь сопротивления | 1937 |

|

SU54219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-15—Публикация

1986-03-03—Подача