4

О

сл

о

зобретение относится к вычислительной технике, в частности предназначено для использования в системах обработки данных.

Целью изобретения является расширение функпиональньгк возможностер за счет обеспечения приостанова и повторного запуска синхросигналов с определенного места цикла.

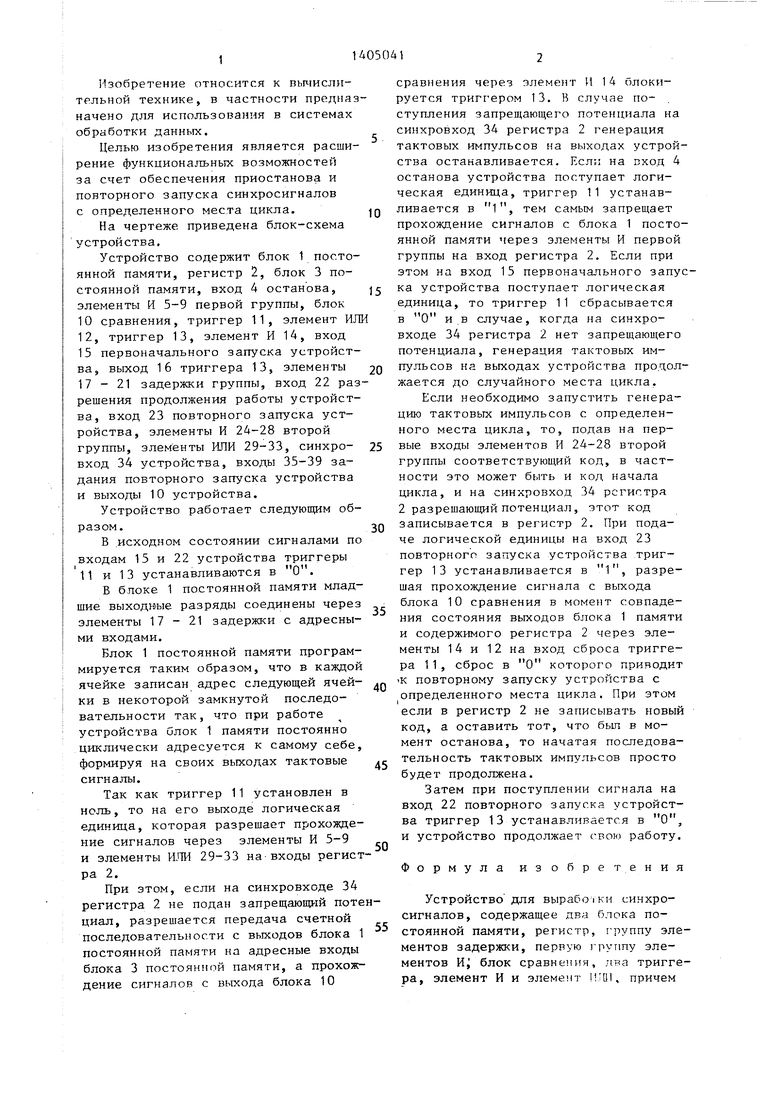

На чертеже приведена блок-схема устройства.

Устройство содержит блок 1 постоянной памяти, регистр 2, блок 3 постоянной памяти, вход 4 останова, элементы И 5-9 первой группы, блок 10 сравнения, триггер 11, элемент ИЛ 12, триггер 13, элемент И 14, вход 15 первоначального запуска устройства, выход 16 триггера 13, элементы 17-21 задержки группы, вход 22 разрешения продолжения работы устройства, вход 23 повторного запуска устройства, элементы И 24-28 второй группы, элементы ИЛИ 29-33, синхро- вход 34 устройства, входы 35-39 задания повторного запуска устройства и выходы 10 устройства.

Устройство работает следующим образом.

В исходном состоянии сигналами по входам 15 и 22 устройства триггеры l1 и 13 устанавливаются в О.

В блоке 1 постоянной памяти младшие выходные разряды соединены через элементы 17-21 задержки с адресными входами.

Блок 1 постоянной памяти программируется таким образом, что в каждой ячейке записан адрес следующей ячей- ки в некоторой замкнутой последовательности так, что при работе устройства блок 1 памяти постоянно циклически адресуется к самому себе, формируя на своих выходах тактовые сигналы.

Так как триггер 11 установлен в ноль, то на его выходе логическая единица, которая разрешает прохождение сигналов через элементы И 5-9 и элементы VLTH 29-33 на-входы регистра 2.

При этом, если на синхровходе 34 регистра 2 не подан запрещающий потециал, разрешается передача счетной последовательности с выходов блока 1 постоянной памяти на адресные входы блока 3 постоянной памяти, а прохождение сигналов с выхода блока 10

Q

5 0 5

0

.

Q

сравнения через элемент И 14 блокируется триггером 13. В случае поступления запрещающего потенциала на синхровход 34 регистра 2 генерация тактовых импульсов на выходах устройства останавливается. Есл;: на пход 4 останова устройства поступает логическая единица, триггер 11 устанавливается в 1, тем самым запрещает прохождение сигналов с блока 1 постоянной памяти через элементы И первой группы на вход регистра 2. Если при этом на вход 15 первоначального запуска устройства поступает логическая единица, то триггер 11 сбрасывается в О ив случае, когда на синхровходе 34 регистра 2 нет запрещающего потенциала, генерация тактовых импульсов на выходах устройства продолжается до случайного места цикла.

Если необходимо запустить генерацию тактовых импульсов с определенного места цикла, то, подав на первые входы элементов И 24-28 второй группы соответствующий код, в частности это может быть и код начала цикла, и на синхровход 34 регистра 2 разрешающий потенциал, этот код записывается в регистр 2. При подаче логической единицы на вход 23 повторного запуска устройства триггер 13 устанавливается в 1, разрешая прохождение сигнала с выхода блока 10 сравнения в момент совпадения состояния выходов блока 1 памяти и содержимого регистра 2 через элементы 14 и 12 на вход сброса триггера 11, сброс в О которого приводит к повторному запуску устройства с определенного места цикла. При этом если в регистр 2 не записывать новый код, а оставить тот, что был в момент останова, то начатая последовательность тактовых импульсов просто будет продолжена.

Затем при поступлении сигнала на вход 22 повторного запуска устройства триггер 13 устанавливается в О, и устройство продолжает свою работу.

Формула изобретения

Устройство для вырабогки синхросигналов, содержащее два блока постоянной памяти, регистр, г-руппу элементов задержки, первую группу элементов Hi блок сравнения, два триггера, элемент И и элемент ИТШ, причем

выходы первого блока постоянной памяти соединены соответственно с первыми входами элементов И первой группы, выходы элементов задержки - с адресными входами первого блока постоянной памяти, выходы регистра - с адресными входами второго блока постоянной памяти и с первой группой информационных входов блока сравнения, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом первого триггера, единичный вход которого является входом повторного запуска уст-- ройства, нулевой вход первого триггера является входом разрешения продолжения работы устройства, выход элемента И соединен с первым входом элемента ИДИ, второй вход которого является входом первоначального запуска устройства, выход элемента ИЛИ соединен с нулевым входом второго триггера, единичный вход которого

является входом останова устароиства, выходы второго блока постоянной па0

5

5

мяти являются выходами устройства, о тличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения при- останова и повторного запуска синхросигналов с определенного места цикла, в устройство введена группа элементов ИЛИ и вторая группа элементов И, причем первые входы элементов И второй группы являются соответственно входами задания повторного запуска устройства, прямой выход второго триггера соединен с вторыми входами элементов И второй группы, инверсный вход второго триггера соединен с вторыми входами элементов И первой группы, выходы элементов И первой группы соединены соответственно с первыми входами элементов ИЛИ группы, вторые входы которых соединены соответственно с выходами элементов И второй группы, выходы элементов ИЛИ группы соединены соответственно с информационными входами регистра,синхровход которого является синхровходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выработки синхросигналов | 1987 |

|

SU1506441A1 |

| Устройство для выработки синхросигналов | 1986 |

|

SU1310793A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для синхронизации каналов | 1985 |

|

SU1262471A1 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для сопряжения памяти с процессором | 1983 |

|

SU1142838A1 |

| Устройство для отладки программ | 1984 |

|

SU1275452A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Логический анализатор | 1986 |

|

SU1363211A1 |

Изобретение относится к вычислительной технике, в частности предназначено для использования в системах обработки данных. Устройство позволяет осуществить повторный запуск не только с начала цикла или с места останова, но и с произвольного места цикля. Целью изобретения является расширение функциональных возможно стей за счет обеспечения приостанова и повторного запуска синхросигналов с определенного мест а цикла. Цель достигается за счет введения элементов МПИ 29, 30, 31, 32, 33 и элементов И 35, 36, 37, 38, 39. 1 ил. (О

| Ортодонтический аппарат для лечения протруссии верхней челюсти | 1985 |

|

SU1509059A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Устройство для выработки синхросигналов | 1986 |

|

SU1310793A1 |

Авторы

Даты

1988-06-23—Публикация

1986-12-29—Подача