3150

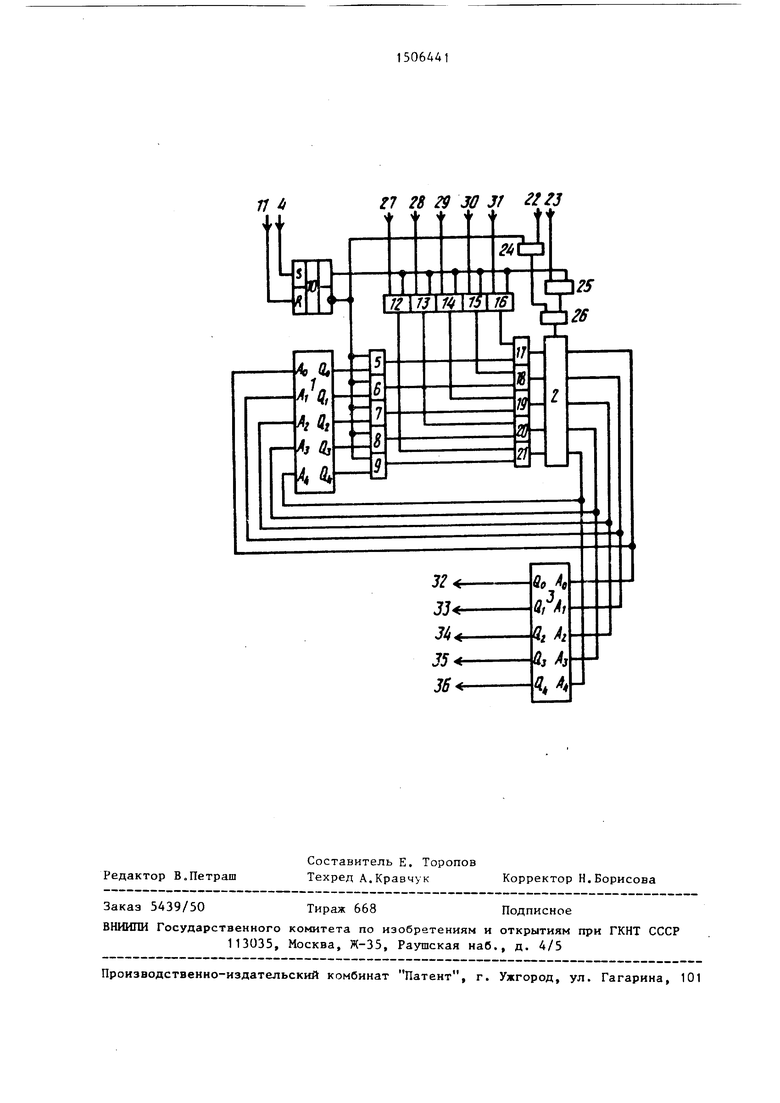

этом счетная последовательность с выходов блока 1 памяти поступает на адресные входы блока 3 памяти, образуя на выходах 32-36 устройства необ- ходимую последовательность синхросигналов. Если на вход А останова устройства поступает сигнал, триггер 10 устанавливается в 1, запрещая прохождение сигналов с выходов блока 1 постоянной памяти через элементы И 5- 9 первой группы, и генерация тактовых импульсов на выходах 32-36 устройства останавливается. Если при этом на вхо 11 запуска устройства поступает сиг- нал, то триггер 10 сбрасьшается в О и генерация С1шхроимпульсов на выходах 32-36 устройства продолжается с того места, где произошел останов

Если необходимо запустить генера- циго тактовых импульсов с определенного места цикла, то подав на входы 27- 31 устройства соответствт, код, в частности это может быть и код начала цикла, а на синхровход 23 разре- тения записи устройства подав импульс этот код будет записан в регистр 2. При подаче импульса на вход 11 запуска устройства триггер 10 сбрасьшается в О, что приводит к повторному устрсйства с определенного lecTa цикла.

Формула изобретения

Устройство Д.ПЯ выработки синхро- сигналов, содержащее два блока пос- тоянной памяти, регистр, первую и вторую группы элементов И, группу элементов ИЛИ, триггер, причем выходы первого блока постоянной памяти сое- динены соответственно с первьми входами элементов И первой группы, вто- «рые входы которых объединены и ссеци1

нены с ;шверсным выходом триггера, выходы элементов И первой группы сое - динены соответственно с первыми входами элементов ИЛИ группы, вторые входы которых соединены соответственно с выходами элементов И второй группы, первые входы которьк являются входами задания повторного запуска устройства, вторые входы элементов И второй группы объединены и соединены с прямым выходом триггера, вход сброса в О которого является входом запуска устройства, вход установки в 1 триггера является входом останова устройства, выходы элементов ИЛИ группы соединены соответственно с информационными входами регистра, разрядные выходы которого соедины с адресными входами второго блока постоянной памяти, выходы которого являются информационными выходами устройства, отличающееся тем, что, с цель расширения функциональных возможносте устройства за счет произвольного изменения длительности цикла генерации синхроимпульсов, в него введены два элемента Ии элемент ИЛИ, причем разрядные выходы регистра соединены соответственно с адресными входами первого блока памяти, инверсный вьпход триггера соединен с первым входом первого элемента И, второй вход которого является синхровходом устройства, прямой выход триггера соединен с первым входом второго элемента И, второй вход которого является входом разрешения записи устройства, выход первого элемента И соединен с первым входом элемента ИЛИ, второй выход которого сое- диен с выходом второго элемента И, выход элемента ИЖ соединен с входом разрегения записи регистра.

и

Z1 2В гд 30 j/ пз

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1432533A1 |

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1287138A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналами связи | 1983 |

|

SU1160421A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для сбора статистических данных о работе программ ЭВМ | 1982 |

|

SU1128266A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Микропроцессор | 1986 |

|

SU1361572A1 |

Изобретение относится к вычислительной технике , в частности, предназначено для использования в системах обработки данных. Особенностью устройства является то, что оно позволяет изменять длительность цикла генерации синхроимпульсов. Целью изобретения является расширение функциональных возможностей за счет произвольного изменения длительности цикла генерации синхроимпульсов. Поставленная цель достигается за счет введения двух элементов И, элемента ИЛИ. 1 ил.

юS

iHt

Лз (

л

« /f«

,

Иг и, Аз

| Устройство для выработки синхросигналов | 1986 |

|

SU1310793A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выработки синхросигналов | 1986 |

|

SU1405041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Изобретение относится к вычислительной технике и, в частности, предназначено для использования в системах обработки данных | |||

| Целью изобретения является расширение функциональных возможностей за счет произвольного изменения длительности цикла генерации синхроимпульсов | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-09-07—Публикация

1987-11-03—Подача