Изобретение относится к вычислительной технике.

Цель изобретения - повышение быстродействия при вычислении обратных , значений дискретных значений непрерывной функции-с ограниченным диапазоном изменения.

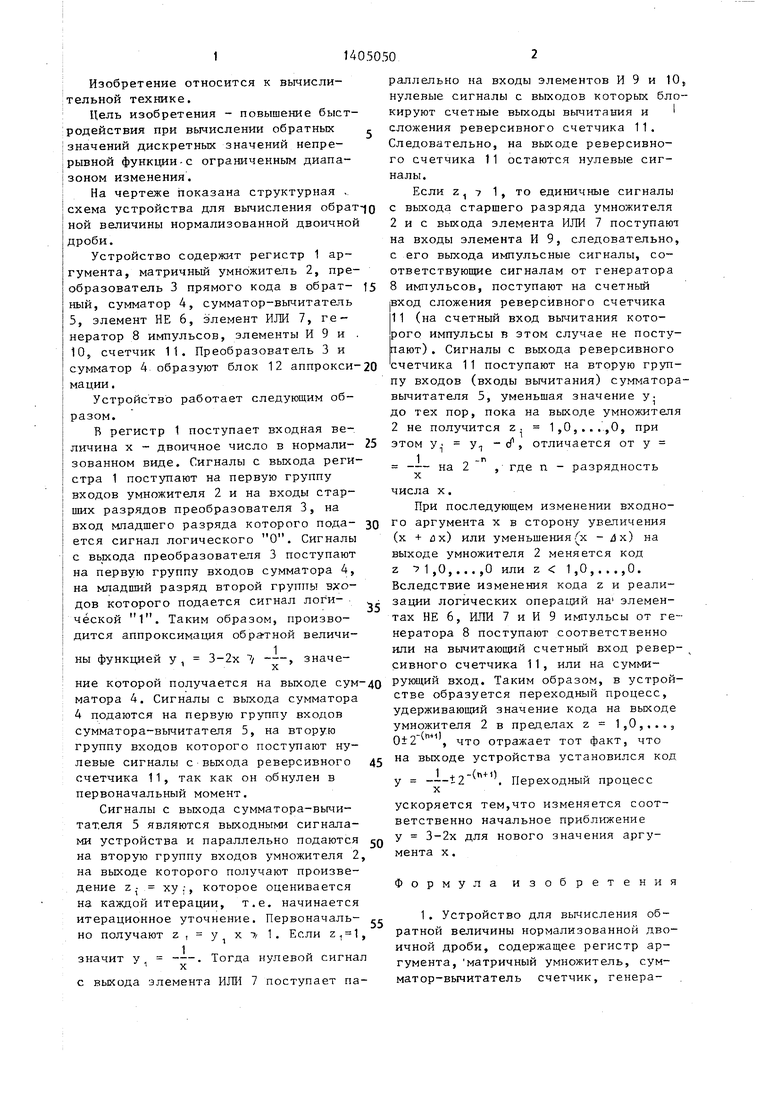

На чертеже показана структурная - схема устройства для вычисления обрат-ю

ной величины нормализованной двоичной дроби.

Устройство содержит регистр 1 аргумента, матричный умножитель 2, преобразователь 3 прямого кода в обрат- 15 ный, сумматор 4, сумматор-вычитатель 5, элемент НЕ 6, элемент ИЛИ 7, генератор 8 импульсов, элементы И 9 и . 10, счетчик 11. Преобразователь 3 и сумматор 4 образуют блок 12 аппрокси-20

мации.

Устройство работает следующим образом.

В регистр 1 поступает входная величина X - двоичное число в нормали- 25 зованном виде. Сигналы с выхода регистра 1 поступают на первую группу входов умножителя 2 я на входы старших разрядов преобразователя 3, на вход младшего разряда которого пода- ЗО ется сигнал логического О. Сигналы с вькода преобразователя 3 поступают на первую группу входов сумматора 4, на младший разряд второй группы входов которого подается сигнал логи- чёской 1. Таким образом, производится аппроксимация обра-тной величины функцией у, 3-2х /, значе X

ние которой получается на выходе сум-до матора 4. Сигналы с выхода сумматора 4 подаются на первую группу входов сумматора-вычитателя 5, на вторую группу входов которого поступают нулевые сигналы с выхода реверсивного 45 счетчика 11, так как он обнулен в первоначальный момент.

Сигналы с выхода сумматора-вычитателя 5 являются выходными сигналами устройства и параллельно подаются JQ на вторую группу входов умножителя 2, на выходе которого получают произведение Z- ху ., которое оценивается на каждой итерации, т.е. начинается

итерационное уточнение. Первоначально получают Z , у х 7/ 1 . Если z, 1,

значит у . Тогда нулевой сигнал

Л

с выхода элемента ИШi 7 поступает па

о 5

Q

5

раллельно на входы элементов И 9 и lOj нулевые сигналы с выходов которых блокируют счетные выходы вычитания и I сложения реверсивного счетчика 11. Следовательно, на выходе реверсивного счетчика 11 остаются нулевые сигналы.

Если 2,7 1, то единичные сигналы с выхода старшего разряда умножителя 2 и с выхода элемента ИЛИ 7 поступают на входы элемента И 9, следовательно, с его выхода импульсные сигналы, соответствующие сигналам от генератора 8 импульсов, поступают на счетный вход сложения реверсивного счетчика 11 (на счетный вход вычитания которого импульсы в этом случае не поступают) . Сигналы с выхода реверсивного счетчика 11 поступают на вторую группу входов (входы вычитания) сумматора- вычитателя 5, уменьшая значение у. до тех пор, пока на выходе умножителя 2 не получится z. 1,0,...,О, при этом у -с/ , отличается от у

1 „ -п

на 2 , где п - разрядность

Л

числа X.

При последующем изменении входного аргумента х в сторону увеличения (х + их) или уменьшения (х - dx) на выходе умножителя 2 меняется код z 71,0,...,0 или z 1,0,..0,0. Вследствие изменения кода z и реализации логических операций на элементах НЕ 6, ИЛИ 7 и И 9 импульсы от генератора 8 поступают соответственно или на вычитающий счетный вход реверсивного счетчика 11, или на суммирующий вход. Таким образом, в устройстве образуется переходный процесс, удерживающий значение кода на выходе умножителя 2 в пределах z 1,0,..,, 0±2 , что отражает тот факт, что на выходе устройства установился код

1 , „ -(h+ii У t2 , Переходный процесс

X

ускоряется тем,что изменяется соответственно начальное приближение у 3-2х для нового значения аргумента X .

Формула изобретения

1. Устройство для вычисления обратной величины нормализованной двоичной дроби, содержащее регистр аргумента, матричный умножитель, сумматор-вычитатель счетчик, генератор импульсов, первый элемент И, элемент ИЛИ и блок аппроксимации, причем выходы разрядов регистра аргумента соединены с входами первой группы матричного умножителя, входы второй группы которого соединены с выходами разрядов сумматора-вычита- теля, выход старшего разряда матричного умножителя соединен с первым входом первого элемента И, выходы остальных разрядов матричного умножителя соединены с входами элемента ИЛИ, второй вход первого элемента И соединен с выходом генератора импульсов, третий вход первого элемента И соединен с выходом элемента ИЛИ, вькод первого элемента И подключен к суммирующему входу счетчика, выходы

10

ных значений непрерьганой функции с ограниченным диапазоном изменения, в устройство введены второй элемент И и элемент НЕ, вход которого подключен к выходу старшего разряда матричного умножителя, а выход - к входу элемента ИЛИ и первому входу второго элемента И, второй и третий входы которого соединены с выходами соответственно генератора импульсов и элемента ИЛИ, а выход подключен к вычитающему входу счетчика.

152. Устройство по п. 1, отлич а е е с я тем, что блок ап- . проксимации содержит преобразователь прямого кода в обратный и сумматор, выходы разрядов которого являются разрядов регистра аргумента подключе- 20 выходами блока, входы старших разря- ны к входам блока аппроксимации, вы- дов преобразователя прямого кода в ходы которого соединены с входамиобратный соединены с младшими входа-

первой группы сумматора-вычитателя,ми блока, а вход младшего разряда соевходы второй группы которого соедине- динен с шиной логического нуля, вхо- ны с выходами разрядов счетчика, а 25 ды первой группы сумматора соедине- выходы разрядов сумматора-вычитате-ны со старшим входом блока и выходами

ля являются выходами устройства, о т- разрядов преобразователя прямого ко- личающееся тем, что, с це-. да в обратный, вход второй группы лью повьш1ения быстродействия присумматора соединен с шиной логичесвычислении обратных значений дискрет- 30 кой единицы.

ных значений непрерьганой функции с ограниченным диапазоном изменения, в устройство введены второй элемент И и элемент НЕ, вход которого подключен к выходу старшего разряда матричного умножителя, а выход - к входу элемента ИЛИ и первому входу второго элемента И, второй и третий входы которого соединены с выходами соответственно генератора импульсов и элемента ИЛИ, а выход подключен к вычитающему входу счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для вычисления функций | 1980 |

|

SU894720A1 |

| Генератор функций | 1984 |

|

SU1275411A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

Изобретение относится к вьиис- лительной технике. Целью является по- вьшение быстродействия при вычислении обратных значений дискретных значений непрерывной функции с С1граничен- ным диапазоном изменения. Устройство содержит регистр 1 аргумента, матричный умножитель 2, преобразователь 3 прямого кода в обратньш, сумматор 4, сумматор-вычитатель 5, элементы НЕ 6, ИЛИ 7, И 9,10. счетчик 11, генератор импульсов 8. Преобразователь 3 и сумматор 4 образуют блок 12 аппроксимации. 1 з.п. ф-лы, 1 ил.

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1983 |

|

SU1125623A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1335985A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-23—Публикация

1986-04-28—Подача