Изобретение относится к области вычислительной техники и может быть использовано, в частности, в 6pjicTpo- действ тощих арифметических устройствах цифровых и комбинированных машин.

Целью изобретения является повышение точности работы устройства.

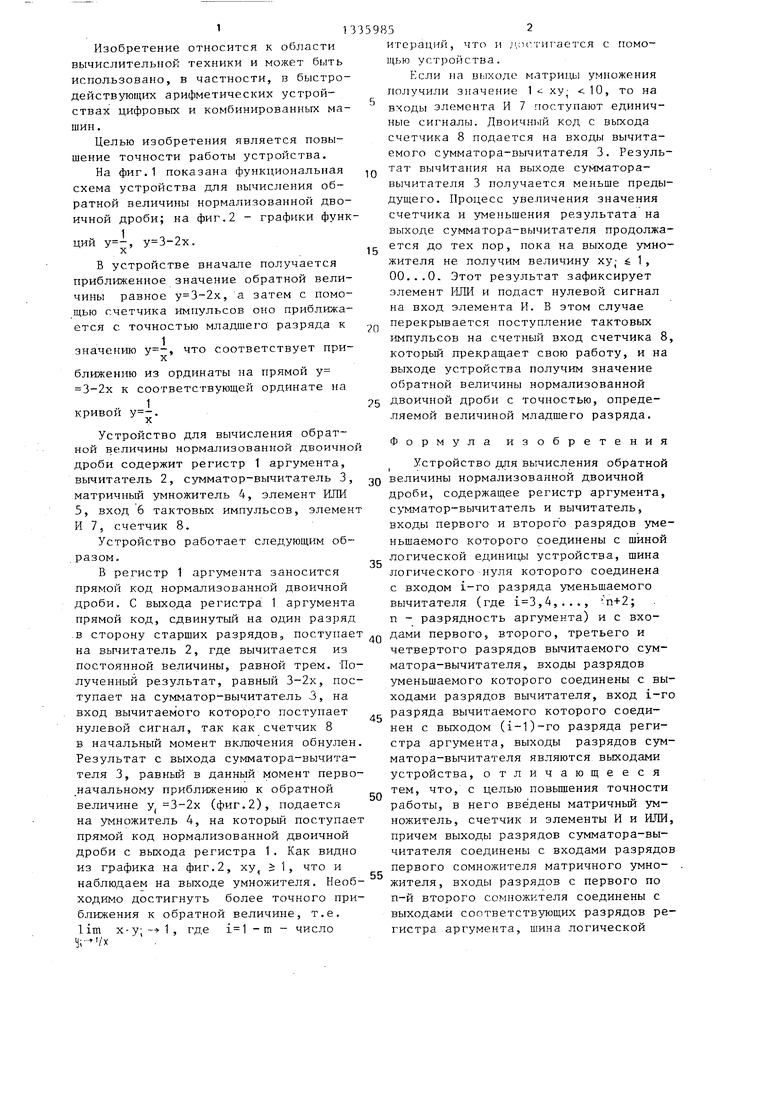

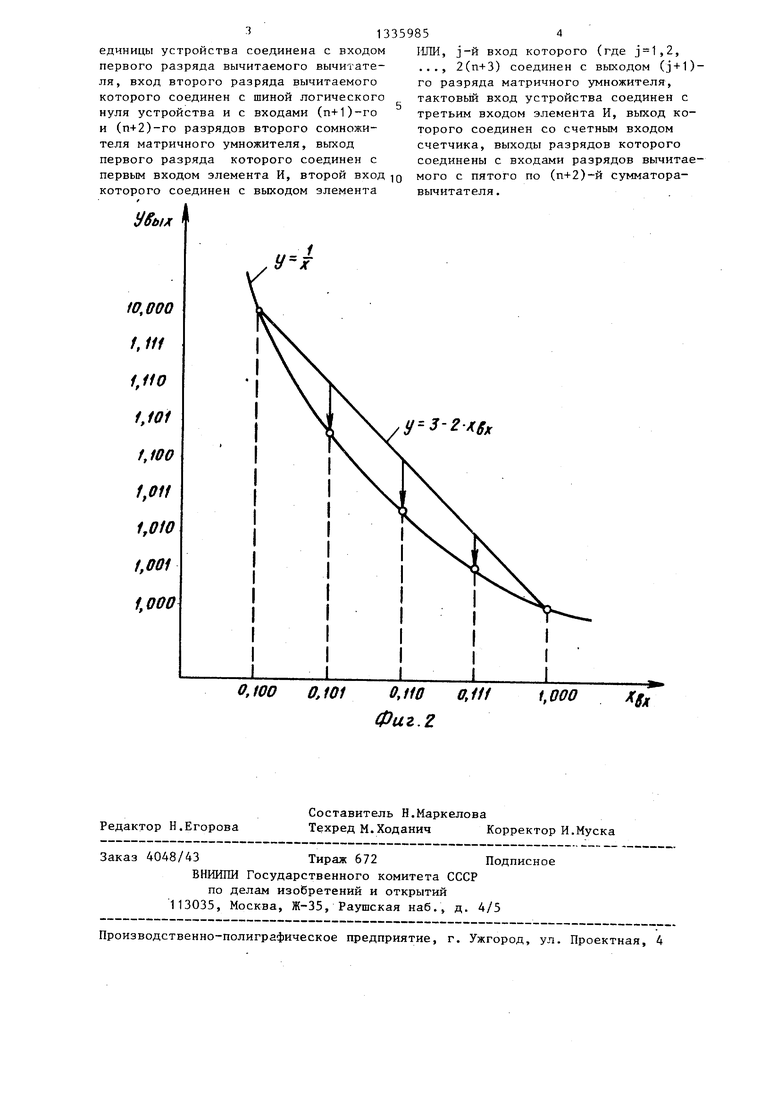

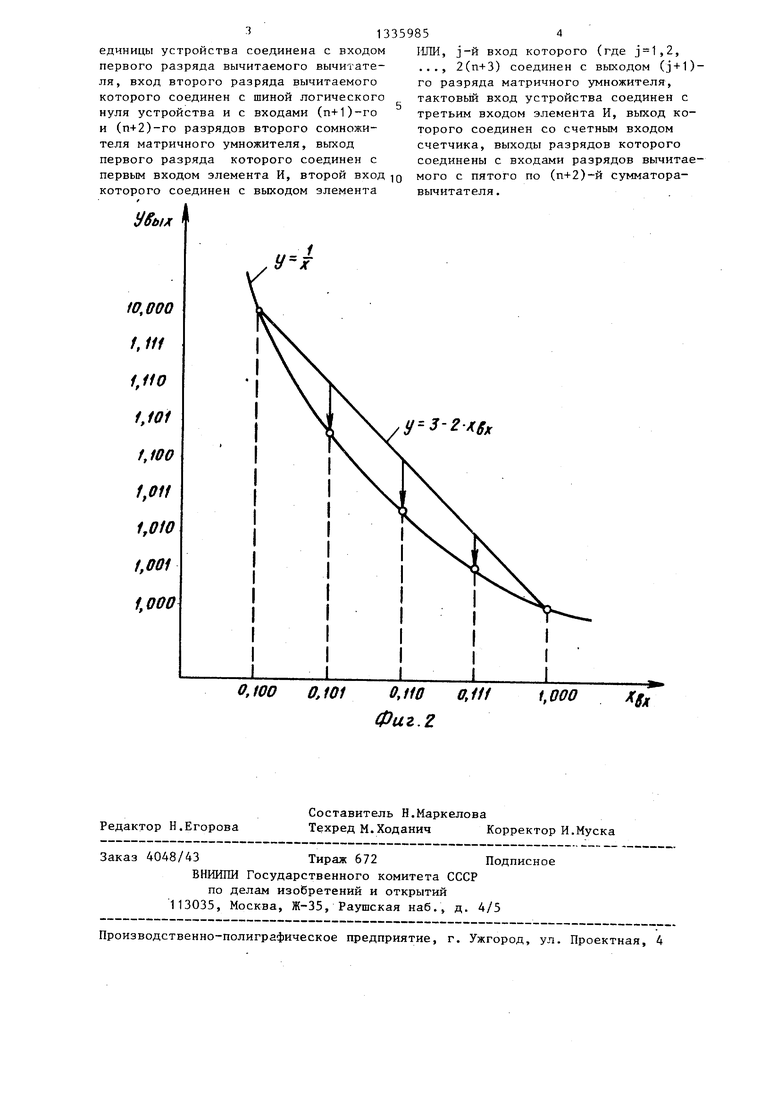

На фиг.1 показана функциональная схема устройства для вычисления обратной величины нормализованной двоичной дроби; на фиг.2 - графики функций , .

Л

В устройстве вначале получается приближенное значение обратной величины равное , а затем с помощью счетчика импульсов оно приближается с точностью младшего разряда к 1

значению ,

X

что соответствует приближению из ординаты на прямой у 3-2х к соответствующей ординате на

1 кривой .

Устройство для вычисления обратной величины нормализованной двоичной дроби содержит регистр 1 аргумента, вычитатель 2, сумматор-вычитатель 3, матричный умножитель 4, элемент ИЛИ 5, вход 6 тактовых импульсов, элемент И 7, счетчик 8.

Устройство работает следующим образом,

В регистр 1 аргумента заносится прямой код нормализованной двоичной дроби. С выхода регистра 1 аргумента прямой код, сдвинутый на один разряд ,в сторону старших разрядов, поступает на вьмитатель 2, где вычитается из постоянной величины, равной трем. Полученный результат, равный 3-2х, поступает на сумматор-вычитатель 3, на вход вычитаемого которого поступает нулевой сигнал, так как счетчик 8 в начальный момент включения обнулен Результат с выхода сумматора-вычита- теля 3, равньй в данный момент первоначальному приближению к обратной величине у 3-2х (фиг.2), подается на умножитель 4, на который поступает прямой код нормализованной двоичной дроби с выхода регистра 1. Как видно из графика на фиг.2, ху, 5 1, что и наблюдаем на выходе умножителя. Необходимо достигнуть более точного приближения к обратной величине, т.е.

1 im х-у; - 1 , где -т - число

5

0

итераций, что и п.ост игается с помо щьго устройства.

Если f:a выходе матрицы умножения получили значение 1 ху- 10, то на входы элемента И 7 поступают единичные сигнал1,1. Двоичн1 1Й код с выхода счетчика 8 подается на входы вычитаемого сумматора-вычитателя 3. Результат вычитания на выходе сумматора- вычитателя 3 получается меньше предыдущего. Процесс увеличения значения счетчика и уменьшения результата на выходе сумматора-вычитателя продолжается до тех пор, пока на выходе умножителя не получим величину ху; б 1, 00...0. Этот результат зафиксирует элемент ИЛИ и подаст нулевой сигнал на вход элемента И. В этом случае перекрывается поступление тактовых импульсов на счетный вход счетчика 8, который прекращает свою работу, и на выходе устройства получим значение обратной величины нормализованной 5 двоичной дроби с точностью, определяемой величиной младшего разряда.

Формула изобретения

Устройство для вычисления обратной 0 величины нормализованной двоичной дроби, содержащее регистр аргумента, су мматор-вычитатель и вычитатель, входы первого и второго разрядов уменьшаемого которого соединены с шиной логической единицы устройства, шина логического нуля которого соединена с входом i-ro разряда уменьшаемого вычитателя (где ,4,..., -п+2; п - разрядность аргумента) и с входами первого, второго, третьего и четвертого разрядов вычитаемого сумматора-вычитателя, входы разрядов уменьшаемого которого соединены с выходами разрядов вычитателя, вход 1-го разряда вычитаемого которого соединен с выходом (1-1)-го разряда регистра аргумента, выходы разрядов сумматора-вычитателя являются выходами устройства, отличающееся тем, что, с целью повьшгения точности работы, в него введены матричный умножитель, счетчик и элементы И и ИЛИ, причем выходы разрядов сумматора-вычитателя соединены с входами разрядов первого сомножителя матричного умно- . жителя, входы разрядов с первого по п-й второго сомножителя соединены с выходами соответствующих разрядов регистра аргумента, шина логической

5

0

5

0

5

единицы устройства соединена с входом первого разряда вычитаемого вычитате- ля, вход второго разряда вычитаемого которого соединен с шиной логического нуля устройства и с входами (п+1)-го и (п+2)-го разрядов второго сомножителя матричного умножителя, выход первого разряда которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента

1ШИ, j-й вход которого (где ,2, .,., 2(п+3) соединен с выходом (j+1) го разряда матричного умножителя, тактовый вход устройства соединен с третьим входом элемента И, выход которого соединен со счетным входом счетчика, выходы разрядов которого соединены с входами разрядов вычитаемого с пятого по (п+2)-й сумматора- вычитателя.

yst

Л//Г

О. WO Л101

y 3-2-j(Sx

OJ10 0.1 ff Фиг.г

1,000

Х8л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1986 |

|

SU1405050A1 |

| Устройство для вычисления обратной величины нормализованной двоичной дроби | 1988 |

|

SU1566344A1 |

| Устройство для определения обратной величины числа | 1989 |

|

SU1649536A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1983 |

|

SU1125623A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Устройство для потенцирования | 1990 |

|

SU1815635A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1987 |

|

SU1425678A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1259259A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

Изобретение относится к области вычислительной техники и может быть использовано, в частности, в быстродействующих арифметических устройствах цифровых и комбинированных машин. Целью изобретения является повышение точности вычисления обратной величины. Для достижения цели в устройство, содержащее регистр 1 аргумента, вычитатель 2, сумматор-вычи- татель 3, дополнительно введены элемент ИЛИ 5, элемент И 7, счетчик 8 и матричный умножитель 4. В устройстве вначале получается приближенное значение обратной величины .у 3-2х, затем оно с помощью счетчика приближается с точностью младшего разряда к значению . 2 ил. с S со со ел. о 00 ел

Редактор Н.Егорова

Составитель Н.Маркелова

Техред М.Ходанич Корректор И.Муска

Заказ 4048/43Тираж 672Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| ВО СОЮЗНАЯ-:.l;Jbi.{) 'ii.K^i'-EOiiliБИБЛИОТЕКАВ. И. Жук | 0 |

|

SU318940A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для приближенного вычисления обратной величины нормализованной двоичной дроби | 1983 |

|

SU1125623A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-17—Подача